一种基于FPGA的万兆以太网MAC层设计与实现

2023-11-30安超群李飞

安超群 李飞

作者简介:安超群(1986— ),女,湖北襄阳人,工程师,硕士;研究方向:模拟电路设计,集成电路设计,数字信号处理,可靠性设计等。

摘要:针对基于软件设计的万兆以太网MAC层无法满足高速数据实时传输的发展要求,文章提出了一种基于FPGA硬件平台的万兆以太网MAC层协议的设计与实现方案。该设计方案主要利用FPGA的并行处理能力,通过Verilog硬件描述语言完成万兆以太网MAC层数据实时处理的硬件设计,实现大带宽、低延时和高可靠性的万兆以太网MAC层的数据收发功能。试验验证表明:该设计方案实现了万兆以太网高速率的数据传输,具有低延时、高性能、高可靠性与简易性等优点。

关键词:万兆以太网;MAC控制器;并行CRC校验;并行数据处理

中图分类号:TP311 文献标志码:A

0 引言

以太网(Ethernet)是一种计算机局域网技术。IEEE制定的IEEE Std 802.3协议,规定了包括MAC层的协议内容、电信号以及物理层的连线。从1983年第一次发布IEEE Std 802.3协议至今,以太网经过了40年的发展,传输速率从10 Mbps、100Mbps提升到1 000Mbps,目前已经达到了10 Gbps[1]。万兆以太网是也称10 G以太网(10 Gigabit Ethernet),是在IEEE802.3ae协议中提出的以太网标准,该标准规范中规定使用光纤传输、传输带宽高达10 Gbps、传输距离最远能达到40km [2],经过不断的升级与扩充,万兆以太网以其速率高、兼容性好、稳定性强的优点逐渐成为以太网的核心设备[3],服务于工业自动化、5G网络传输和智慧城市建设等行业。

大多数系统设计中,10Mbps、100Mbps和1 000Mbps以太网协议除了物理层以外的协议层均以软件的方式实现,甚至10 Gbps以太网协议使用高性能CUP或服务器实现。基于串行处理的软件架构难以并行处理以太网协议中的各种事务,同时CPU还要优先响应中断事务,随着技术的发展,CPU的处理频率已经大幅提高,同时可以用多核CPU来处理多任务。但是,以太网速度的提升远大于CPU处理性能的提升,使得CPU能够用来处理单个网络数据包的时间减少。如果CPU不能及时处理网络数据包,那必然会影响网络传输的延时和吞吐量[4]。因此,基于软件控制实现的10 Gbps以太网协议数据传输效率较低,难以满足大带宽、低延时和高可靠性的数据传输。根据高速数据传输的处理要求,结合以太网的传输协议,引入一种并行的以太网协议处理方式是解决大带宽、高速率数据处理需求和软件计算能力有限之间矛盾的有效方法。

1 万兆以太网通信协议架构

1.1 万兆以太网各协议层的组成

基于IEEE Std 802.3标准的万兆以太网协议架构如图1所示,其架构主要包括:应用层(Application)、表示层(Presentation)、会话层(Session)、传输层(Transport)、网络层(Network)、数据链路层(Data_link)和物理层(Physical)。其中,数据链路层提供物理地址寻址,让成帧的数据按一定规则沿链路从一个节点传到另一个节点,负责发送一个分段内的数据,常见的链路层产品就是网卡、网桥等[5];物理层主要规范了数据传输的媒介、物理连接及光电特性能内容,保证光电信号的可靠传输。

1.2 万兆以太网MAC层特性

万兆以太网协议标准中规定,整个数据通信过程系统的物理层(Physical)通信速率必须具备10 Gbps带宽的数据传输能力。根据协议规定,数据在物理层的传输速率是比较固定的,除了受到器件的物理特性的影响外,设计者在这一层级的优化设计没有太大的空间。应用层(Application)、表示层(Presentation)和会话层(Session)的使用主要涉及具体的业务,这些层级功能主要靠软件实现。在协议中传输层(Transport)、网络层(Network)和数据链路层(Data_link)事务定义明确,因此具有一定的提速空间。本文主要重点优化设计数据链路层的数据处理速率。

由图1可知,数据链路层的数据处理过程主要是将用户数据进行MAC层协议的封装,MAC层协议的封装主要涉及传输控制协议(TCP)和用户数据报协议(UDP)。TCP 的传输速度慢,效率低,确认机制、重传机制、拥塞控制等都会占用大量的时间[6]。UDP协议具备传输速率块、效率高等优点,如果能够研究出有效可靠的数据处理流程保证UDP协议数据传输的可靠性,使用UDP协议传输数据将大大提高数据传输系统的数据处理速率。

2 基于FPGA的万兆以太网高效率MAC层设计与实现

2.1 高效率低延时万兆以太网MAC架构设计

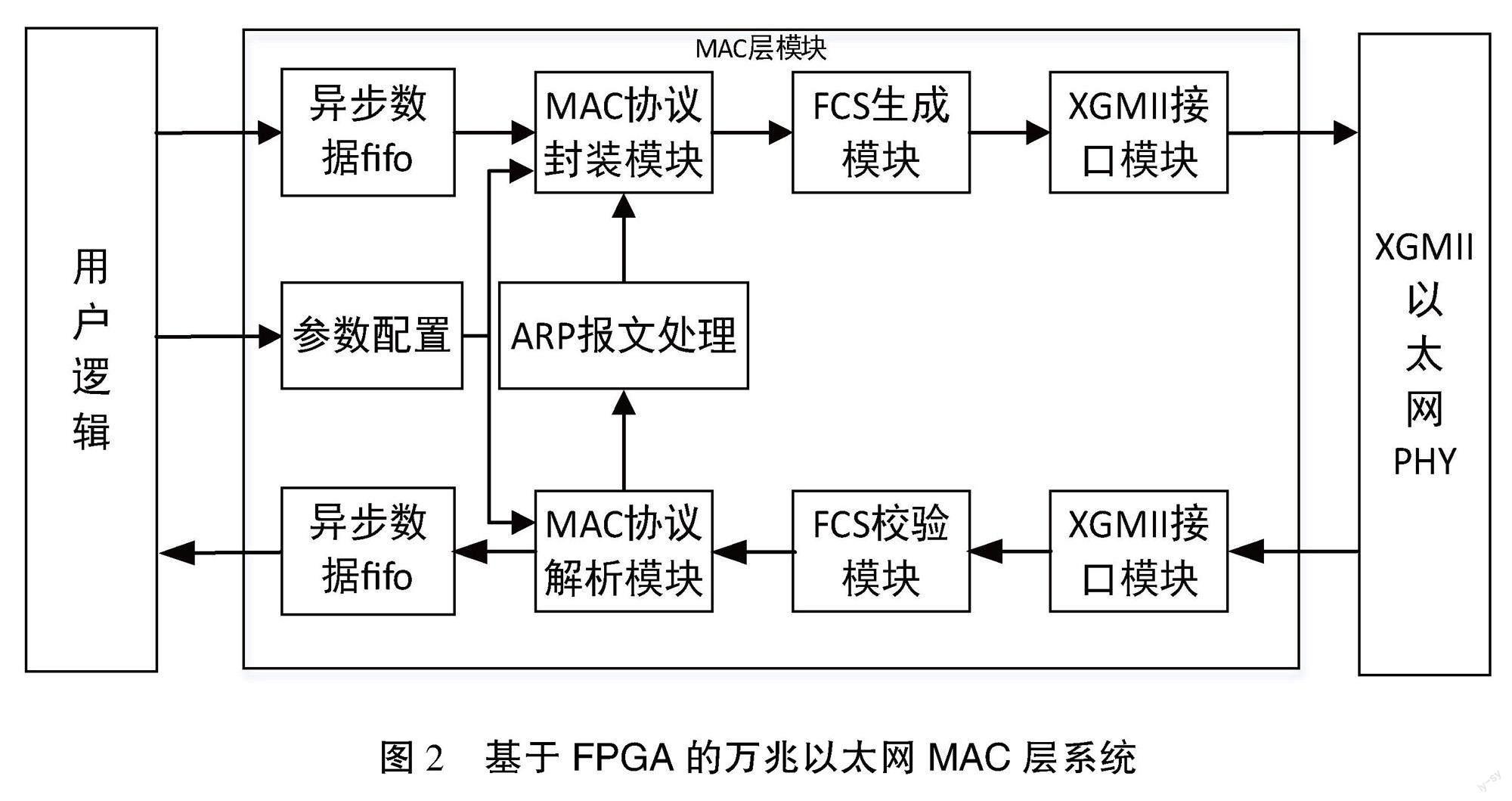

根据前面分析,应用FPGA的并行处理能力实现万兆以太网高效率的数据链路层,并对其可靠性进行验证,可实现高效率的UDP协议数据传输。基于FPGA的万兆以太网MAC层架构如图2所示。用户逻辑使用AXI4协议进行数据交互,MAC层模块内使用异步FIFO对数据进行跨时钟域处理,通过参数配置模块对MAC层模块进行本地MAC地址、本地IP地址、ARP控制参数和端口号等参数配置。在发送通路中,MAC协议封装模块将异步FIFO输出的数据按UDP协议添加UDP包头、IP包头和MAC帧头,将数据封装成MAC帧,再将数据传输至FCS生成模块生成CRC校验数据,最后将数据送至XGMII接口处理模块进行处理发送。在MAC协议封装模块中,要同时响应用户数据和ARP报文数据,其中ARP报文优先级最高。在接收通路中,在接收前端先将XGMII结构数据转换成MAC帧,将MAC帧数据送至FCS校驗模块进行CRC校验,数据校验正确后再将数据送至MAC协议解析模块进行处理,解析完成后按照接收的数据类型将数据传至异步FIFO或者将信息传至ARP报文处理模块进行ARP应答。

2.2 MAC层事务数据并行处理算法

根据图2分析,MAC层数据处理算法流收发模块相互独立,处于全双工工作状态。同时,FCS模块中CRC校验和计算根据数据长度不同,分别设计了并行处理的64 bit、56 bit、48 bit、40 bit、32 bit、24 bit、16 bit和8 bitCRC校验子模块,最多只需要1个时钟周期就能完成64 bit数据的校验和帧尾不同长度字节数据的验证,在一帧数据传输结束标准产生时能同步无延时地输出校验结构,很大程度提高了数据传输效率。在系统初始阶段,MAC层模块根据系统配置的参数向目标主机发送ARP报文请求,等待系统返回ARP帧获取主机MAC地址。在MAC层模块设计中,可通过参数配置设定ARP报文请求次数,等待报文超时时间等参数,目标主机发送ARP报文请求时,MAC层模块将优先回复ARP报文。

在整个MAC层模块中,UDP协议的封装和解析,IP层协议的封装和解析,MAC层的协议的封装和解析大都直接调用系统预先配置的参数封装和完成解析,这样处理大大提高了数据的处理效率。IP校验和计算和校验结果均能实时地计算完成,ARP报文处理、ICMP报文处理和数据帧处理均能实时地响应,降低了数据传输延时,提高了系统性能。

3 系统实现及试验验证

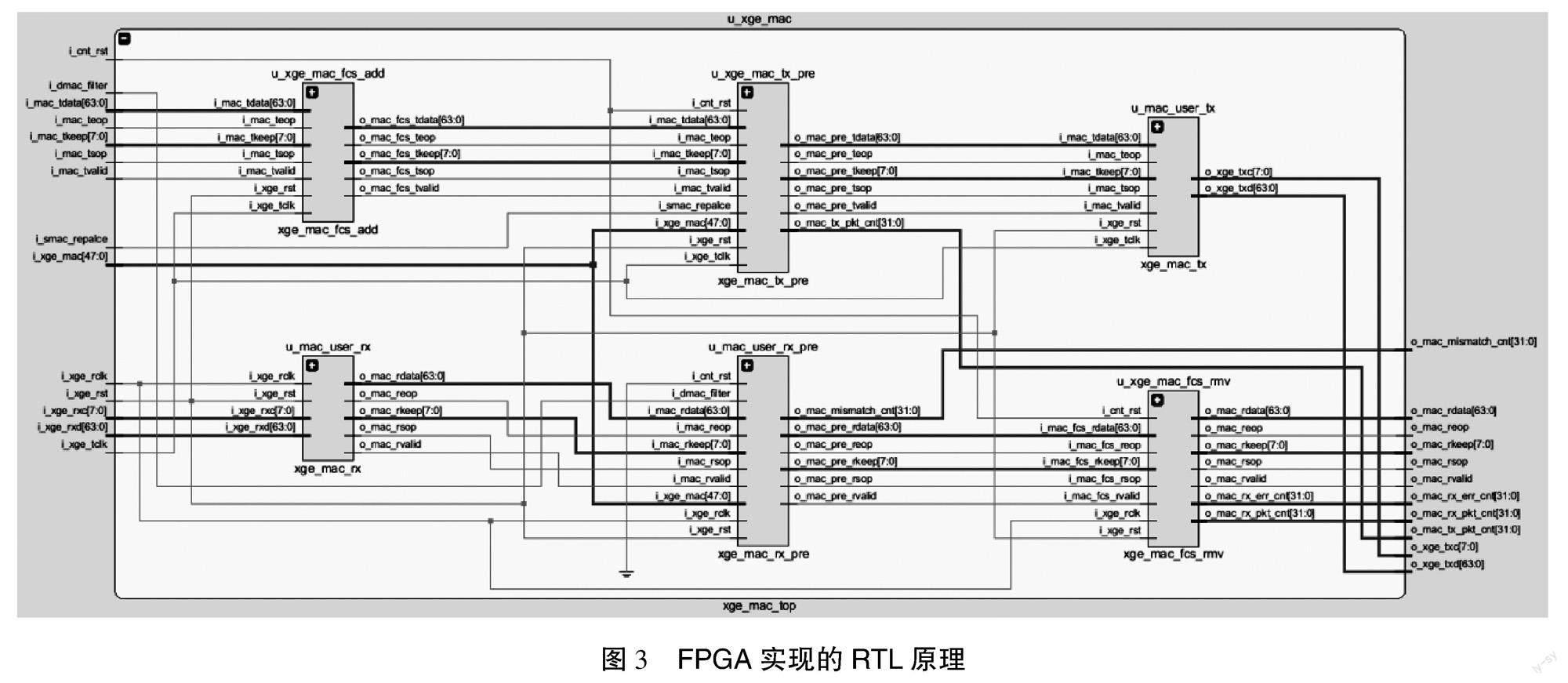

根据前面分析的系统架构和算法设计,万兆以太网MAC层FPGA实现的RTL原理如图3所示,整个系统设计运用自顶向下的设计思想。发送通道主要由u_xge_mac_fcs_add、u_xge_mac_tx_pre和u_mac_user_tx 3个主模块组成,3个主模块内均有是实现算法设计功能要求的相应的子模块。接收通道主要由u_xge_mac_fcs_rmv、u_xge_mac_rx_pre和u_mac_user_rx 3个主模块组成。与发送通道相同,3个主模块内均有满足算法设计功能要求的相应的子模块。

针对整个万兆以太网系统,设计测试模块进行数据回环测试,测试系统由数据产生模块、数据校验统计模块和debug参数管理控制模块组成。按照搭建的测试平台,利用FPGA内部的ILA在线逻辑分析仪对系统测试分析,测试系统RTL如图4所示。

整个系统对相同的一帧数据进行了10 000次的回環测试,错误统计结果为0,由此验证了整个UDP协议的MAC层数据传输的可靠性,帧头处理延时为91个时钟周期,除去帧头延时数据发送延时为2个时钟周期。根据试验结果,应用该方法设计的万兆以太网MAC层数据传输效率显著提高。

4 结语

本文介绍了一种基于FPGA硬件平台的万兆以太网MAC协议的详细设计与实现方案,利用此平台完成了万兆以太网MAC层数据的收发仿真与实物测试。该万兆以太网测试平台主要由光电转换模块、光纤和FPGA芯片及外围电路组成硬件框架,利用此硬件架构,通过数据回环测试实现了大带宽、低延时和高可靠性的万兆以太网MAC层的数据收发功能。试验验证表明,该设计方案完成了整个通信流程的数据收发,实现了万兆以太网UDP协议数据收发功能,除去协议开销,用户数据传输速率高达8.546 Gbps,具有高性能、高可靠性与简易性等优点。该方案设计在有高速率、大带宽且具有一定定制化要求的高速万兆以太网协议通信设计应用中具有重要参考意义。

参考文献

[1]敖志刚.万兆以太网及其实用技术[M].北京:电子工业出版社,2007.

[2]曹政,李磊,陈明宇.万兆以太网MAC控制器设计与实现[J].小型微型计算机系统,2007(6):5.

[3]赵柏山,王禹衡,刘佳琪.用于视频传输的10G网络接口设计[J].微处理机,2018(3):28-32.

[4]张佳怡.基于10G光通信网络加速系统的设计与实现[D].南京:南京理工大学,2020.

[5]王禹衡.基于FPGA的10G以太网UDP/IP处理器视频传输接口设计[D].沈阳:沈阳工业大学,2018.

(编辑 王永超)

Design and implementation of a 10 Gigabit Ethernet MAC layer based on FPGA

An Chaoqun1, Li Fei2

(1.Guangdong Vocational College of Mechanical and Electrical Technology, Guangzhou 510515, China;

2.Guangzhou Haige Communications Industry Group Co., Ltd., Guangzhou 510663, China)

Abstract: In response to the software based design of the 10 Gigabit Ethernet MAC layer being unable to meet the development requirements of high-speed real-time data transmission, a design and implementation scheme of the 10 Gigabit Ethernet MAC layer protocol based on FPGA hardware platform is proposed. This design scheme mainly uses the parallel processing ability of FPGA to complete the hardware design of real-time data processing of 10 Gigabit Ethernet MAC layer through Verilog hardware description language, and realize the data receiving and transmitting function of 10 Gigabit Ethernet MAC layer with large bandwidth, low delay and high reliability. Experimental verification shows that this design scheme achieves high-speed data transmission over 10 Gigabit Ethernet, excluding protocol overhead. It has the advantages of high performance, high reliability and simplicity.

Key words: 10 Gigabit Ethernet; MAC controller; parallel CRC verification; parallel data processing