介电损耗在TFT性能提升中的应用

2023-11-08李砚秋林鸿涛颜京龙崔晓鹏陈维涛周冉一刘丹方亮

李砚秋,林鸿涛,颜京龙,崔晓鹏,陈维涛,周冉一,刘丹,方亮

(1.北京京东方显示技术有限公司,北京 100176;2.重庆京东方光电科技有限公司,重庆 400700;3.重庆大学,重庆 400044)

电容器由上下电极和介质层组成,介质层即是绝缘层。在电场作用下,由于介质电导和介质极化的滞后效应,绝缘材料内部存在能量损耗,即介电损耗。介电损耗是评估介质材料绝缘状况和材料质量优劣的关键参数。在绝缘材料实际使用过程中,严禁出现大的介电损耗,否则会引起绝缘材料剧烈生热而损坏,因此,在电气设备绝缘材料的选用中,应选择介电损耗小的介质材料[1-2]。对于电容器来说,如果电介质的介电损耗增加,介质剧烈发热,最终会导致电容器被击穿。

薄膜晶体管液晶显示器(Thin film transistor liquid crystal display,简称TFT-LCD)是目前的主流显示技术,该显示器的核心部件是TFT。TFT 通常由栅极(Gate)、栅极绝缘层(Gate Insulator,简称GI)、非晶硅、源漏极(Source和Drain电极,简称SD电极)、像素电极、钝化层、公共电极组成,栅极采用Cu 电极,栅极绝缘层通常采用SiNx[3-5]。对栅极施加-20~+20V 的扫描电压信号,对源漏极施加15V 电压,TFT 源漏极之间的电流逐渐增加。为了提升TFT 的Ion,需要增加栅极绝缘层的电容。通常,通过降低栅极绝缘层的厚度来增加电容[6],但是,栅极绝缘层厚度降低,会导致该电容的耐压性能降低,栅极绝缘层容易被击穿,造成Gate和SD 电极短路[7-8]。综上所述,要提升TFT 的Ion,栅极绝缘层需要降低厚度;而要提升TFT 的耐压能力,栅极绝缘层厚度需要增加。对于栅极绝缘层厚度面临的矛盾,TFT 行业暂时无有效的解决方案。栅极绝缘层属于电介质,电介质的击穿与介电损耗相关,如果降低栅极绝缘层的介电损耗,那么绝缘层的耐压强度可以提升。鉴于此,可以在栅极绝缘层降低厚度的前提下,优化TFT 制程工艺,降低栅极绝缘层的介电损耗,这样既可以提升TFT 的Ion,又可以保证TFT 的耐压能力。

本文结合8.5 代TFT 产线,制作栅极绝缘层电容器和TFT,测试电容器的介电性能和TFT 转移曲线,明确影响介电损耗的因素;开发出一套表征栅极绝缘层电容器介电损耗的测试方法,明确介电损耗和耐压强度的关系;同时,揭示介电损耗和TFT 性能的关系,为产线优化TFT 性能提供参考。

1 实验

1.1 样品制作

1.1.1 SiNx 薄膜MIM 电容器的制作

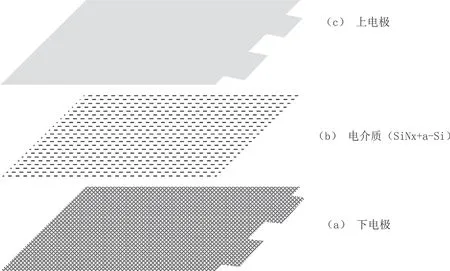

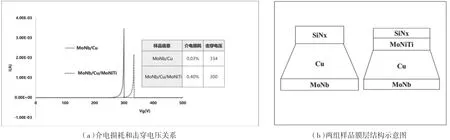

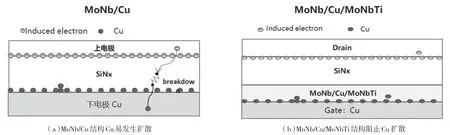

本实验中SiNx 薄膜MIM 电容器的整体工艺流程如图1 所示。第一步,先使用磁控溅射的方法沉积下电极薄膜MoNb/Cu,或者MoNb/Cu/ MoNiTi,并通过曝光显影、刻蚀对薄膜进行图案化处理[9],如图1(a)所示。第二步,使用PECVD 方法,在制备完成的下电极上沉积一层SiNx 介质薄膜和a-Si,使用刻蚀技术对薄膜进行图案化处理,如图1(b)所示。第三步,在完成SiNx 介质薄膜图形化的基片上采用磁控溅射的方法制备Mo/Al/Mo 薄膜,并进行光刻图形化处理[10],得到MIM 电容器的上电极[11],如图1(c)所示。

图1 MIS 膜层结构

1.1.2 薄膜晶体管TFT器件的制作

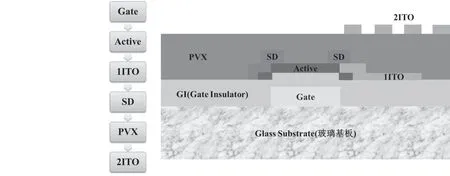

首先,在玻璃基板上依次制作Gate 层、SiNX(Gate Insulator,简称GI 层)层、a-Si 层、1ITO、钝化层(PVX)和2ITO,每一层均是经过成膜→光刻→刻蚀步骤,最终图形化,从图2 可以看出薄膜晶体管TFT 是由源极、漏极、栅极、有源层、栅绝缘层组成[3-5]。

图2 TFT 器件结构及制程顺序示意图

1.2 薄膜晶体管IV 曲线及MIM 电容器介电损耗测试设备及方法

本文采用Keysight 公司的B1500A 半导体分析仪和B2201A 开关矩阵组成的测试系统,对薄膜晶体管测试转移曲线,并对MIS 电容测试介电性能。

1.2.1 薄膜晶体管转移曲线测试方法

固定源漏电压(VDS)15V,栅极电压扫描范围为-20~+20V,测试源漏电流(IDS)随VGS变化的关系,最终获得器件的特性转移曲线。通过曲线获得器件的性能参数、开态电流Ion、关态电流Ioff,进一步可计算得到器件的阈值电压Vth 和迁移率Mob[12]。

1.2.2 介电损耗表征方法

介质在外加电场时,会产生感应电荷而削弱电场,这种被削弱的能量,一部分被介质储存起来,被称为介电常数;另一部分被损耗掉(转化为热能),被称为介电损耗,又称介质损耗因数,是指介质损耗角正切值[13]。本文主要研究介电损耗的相关内容。

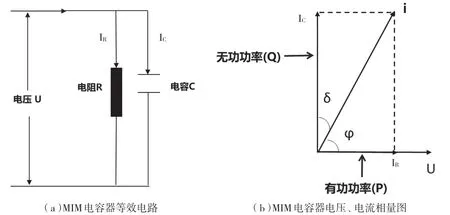

不同的电介质,在不同状态下,介电损耗也不尽相同。所以,在工程计算中并不选择计算电介质的能量损耗,而是通过电介质电流的有功分量和无功分量的比值来表征,即tanδ,如图3 所示。

图3 电压、电流相量图

在图3 中,δ 的产生主要是因为绝缘介质既产生有功损耗(电介质电阻产生的损耗),又产生无功损耗(电介质电容产生的损耗),导致施加在绝缘介质上的交流电压与电流之间的功率因数角φ不是90°,所以,将介电损耗因数定义如下:

根据图3(b)可知,施加在MIM 器件的总电流I可以分解为电容电流Ic 和电阻电流IR,因此,介电损耗因数(tanδ)可以用以下公式表示:

因为δ 是功率因数角φ的余角,所以可以用数字化仪器,通过测量δ 或者φ得到介电损耗因数。

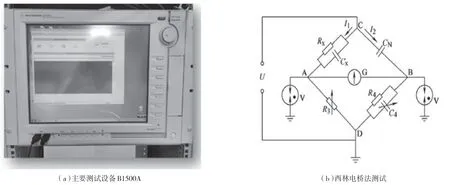

1.2.3 薄膜介电损耗测试方法

Agilent B1500A 半导体分析仪采用西林电桥法来测量阻抗,如图4 所示,通过仪器内部的等效电路模拟给出样品的电容和损耗,再通过公式tanδ=1/ωRPC,计算得到薄膜的介电损耗,公式中Rp为介质层漏电阻,C为介质层电容,ω为角频率。在测试过程中,连接在B1500A 半导体分析仪上的两根探针,一根扎在下电极,另一根扎在上电极,在-25~+25V 扫描电压和1kHz频率下,加100mV 交流信号(AC Level),测量介电损耗随电压变化的曲线。Agilent B1500A 测量介电损耗,生成两种模型:一种是串联模型,另一种是并联模型,本次使用的是并联模型。

图4 实验设备及电路示意图

1.2.4 介电损耗影响因素及测试优选条件验证

介电性能是指电介质在外施电场的作用力下,其微观极化作用反映在宏观中所表现出的性能。因此,电介质介电性能受环境因素影响的本质,就是极化效应受外部环境的影响,主要表现在电介质的介电损耗随频率、湿度、温度等环境因素的变化而不断改变,如表1 所示。

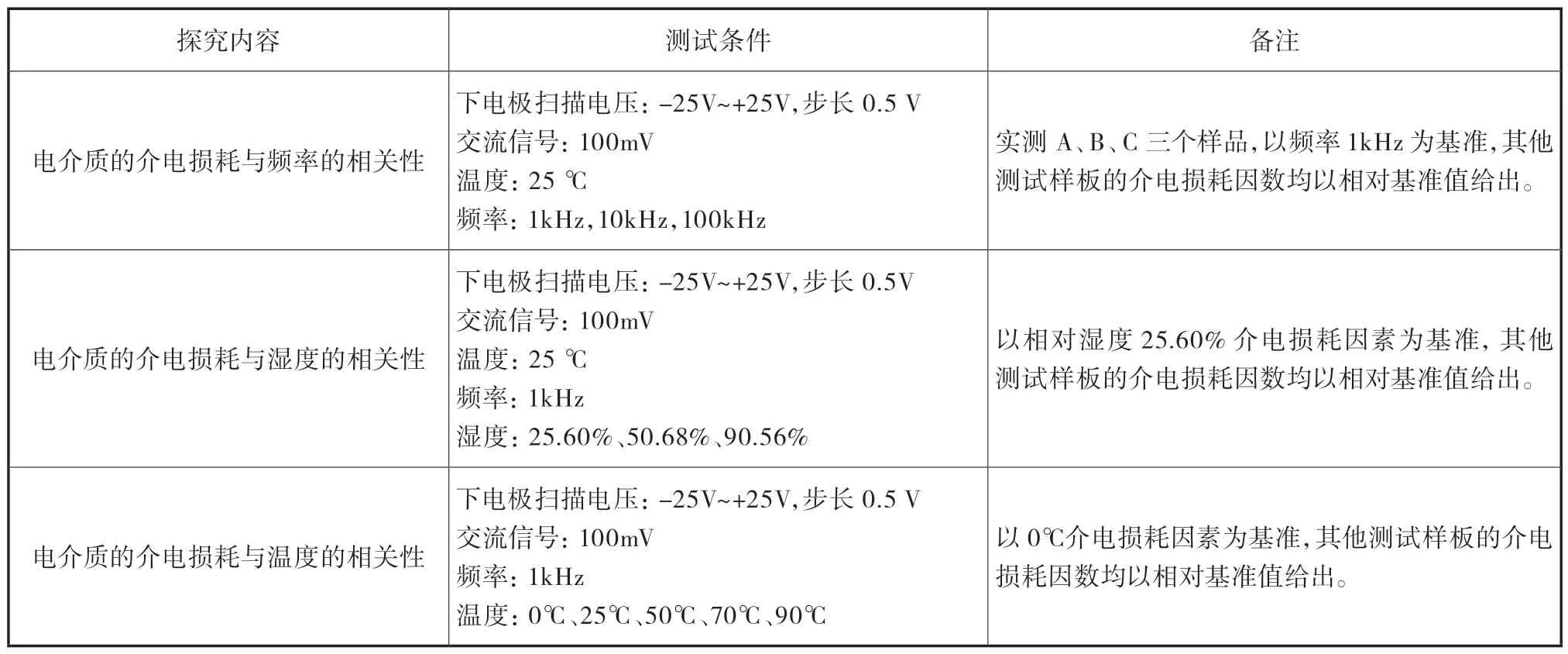

表1 实验条件汇总

2 实验结果与分析

2.1 MIM 器件介电损耗与频率的相关性

由表2 可以看出,随着频率的增加,A、B、C 三个样品的相对介电损耗均升高。在介电损耗测试过程中,对样品施加交流信号,当外电场的频率很低时,介质中各种极化都能跟上外电场的变化,介电损耗几乎为零。当外电场的频率逐渐升高时,缓慢极化在某一频率后开始跟不上外电场的变化,由于缓慢极化滞后于外电场的变化而产生电能的损耗,使介电损耗随着频率的增大而增大[11,14]。

表2 频率对介电损耗的影响

2.2 MIM 器件介电损耗与湿度的相关性

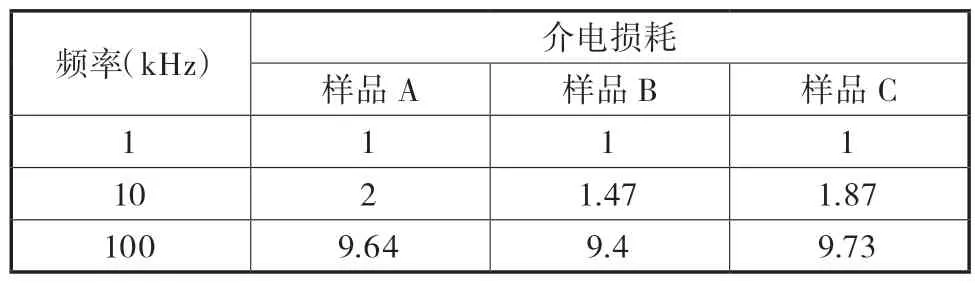

由表3 可以看出,随着湿度的增加,A、B、C 三个样品的相对介电损耗均升高,主要原因是松驰极化损耗增加,致使介电损耗增大。

表3 湿度对介电损耗的影响

2.3 MIM 器件介电损耗与温度的相关性

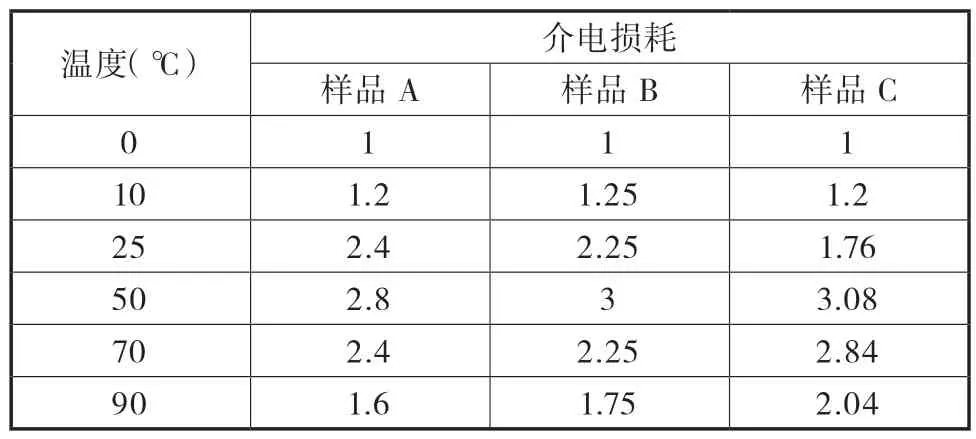

由表4 可以看出,随着温度的增加,介电损耗在50℃时存在拐点,主要原因是当温度很低(0℃)时,松弛时间很长,松弛极化完全来不及建立,此时介电损耗很小;当温度逐渐升高时(0~50℃),粒子热运动能增大,松弛时间逐渐减小,松弛极化开始产生,因而,介电损耗随着温度升高而增大;当温度超过某一数值(大于50℃)时,随温度上升,松弛极化减小,介电损耗减小。

表4 不同温度下介电损耗测试结果

SiNX层漏电阻产生的损耗,主要影响MIS 器件低频阶段;SiNX上下电极产生的损耗,主要影响MIS 器件高频阶段[11,14]。本文主要研究SiNX层的损耗,所以选取低频率1kHz 作为测试条件,实验室标准室温和湿度分别为 25℃、50.68%。在不考虑温度和湿度的条件下,将介电损耗测试的条件设为:频率为1kHz,温度为25℃,湿度为50.68%。

3 基于介电损耗分析表征的产品特性

3.1 MIS 器件介电损耗与击穿电压的相关性

介电损耗与击穿电压实验结果如图5(a)所示。介电损耗越大,电介质耐压能力下降,栅极的金属离子很容易越过降低势垒,扩散进入栅极绝缘层SiNX中,SiNX在电场作用下,因损耗作用膜层内部热量积累并以热能形式耗散,当温度达到足够高时,膜层失去绝缘能力,从而由绝缘状态突变为导电状态,致使膜层被击穿,如图5(b)所示。

图5 两组样品不同介电常数下的击穿电压曲线

3.2 介电损耗与TFT 器件的相关性

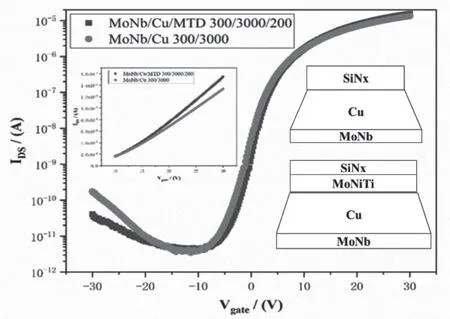

介电损耗与TFT 特性的实验结果如表5 所示。介电损耗大,Vth 大,Ion 偏小。主要原因是Cu 离子向栅极绝缘层扩散,形成导电通道,这会造成电容器的漏电流增加,介电损耗亦增加。Gate 充电到TFT 沟道产生电子的能量流过程:Gate 充电,获得电能;但Gate 存在电阻,部分电能会以Gate 热能形式损失,剩余部分能量极化栅极绝缘层;栅极绝缘层被极化,但该介质存在介电损耗,又有一部分能量以热能形式损失。栅极绝缘层的介电损耗越大,消耗的能量越多,为了使得沟道产生足够数量电子,需要增加额外的栅压来补充能量损失,最终表现为Vth 增加,Ion 下降,如图6、图7 所示。

表5 介电损耗与TFT 特性关系

图6 两种膜层结构击穿示意图

图7 两种膜层结构转移曲线

4 结语

本文通过引入介电损耗的概念,实现对TFT 的栅极绝缘层电容器膜质特性的表征。介电损耗受到测试频率、温度和湿度的影响,基于实验室条件,本文开发了一套可以表征栅极绝缘层介电损耗的方法。栅极绝缘层的介电损耗与击穿强度及TFT 的Ion 特性均呈负相关关系,当介电损耗由0.03%增加到0.40%,击穿场强由334V 降低到300V,TFT 的Ion 由3.99uA 降至3.48uA。依据介电损耗的变化,可以优化TFT 工艺,既能提高TFT 的耐压强度,又能提升TFT 的电学特性。