基于DDS的雷达中频信号模拟器设计

2023-09-07马绪铎

摘?要:信号模拟器在雷达、通信等有电子领域均有广泛应用。直接数字合成技术(DDS)能够有效的解决模拟频率合成电路中对频率、相位等信号特征控制复杂和误差较大的问题。本文介绍了一种基于DDS技术的雷达中频信号模拟器设计实现方法,以ARM嵌入式软核处理器控制DDS芯片,配合后端电路中滤波、放大、程控衰减等信号整形手段,最终产生满足要求的连续波/脉冲的单频信号、线性调频信号和频率快速捷变信号等多种雷达中频信号。通过实际电路测试给出结果,达到预期设计目标。

关键词:DDS;GM4940;ARM;STM32;中频信号模拟器

引言

雷达中频信号模拟器在雷达领域具有广泛的应用,可以用作频率合成器的重要组成部分,还可以作为调试检测时的模拟雷达中频回波信号的生成。直接数字合成技术(Direct Digital Frequency Synthesis)产生于上世纪七十年代初,与传统频率合成技术相比,DDS技术具有高的输出频率分辨率、高精度、低相噪、切换频率时保持相位连续等优点[1-6]。传统的直接频率合成和锁相频率合成(PLL)已不能满足现代雷达频率捷变、波形参数捷变等快速跳频的需求[7]。DDS技术是一种全数字技术[2-4],为满足现在雷达所需信号的要求,频率合成就是用一个高稳定度与高标准度的标准频率源作为参考,通过对该频率进行各项运算和滤波后得到相同稳定度和准确度的不同的频率信号,作为雷达发射的基准频率。中频信号模拟器作为辅助调试检测雷达使用时,需要对雷达接收到的回波信号进行模拟,产生相同频率的雷达回波信号便于整个接收通道的检查,可以辅助雷达完成距离零位标定、角度零位标定、相位补偿等各项工作。

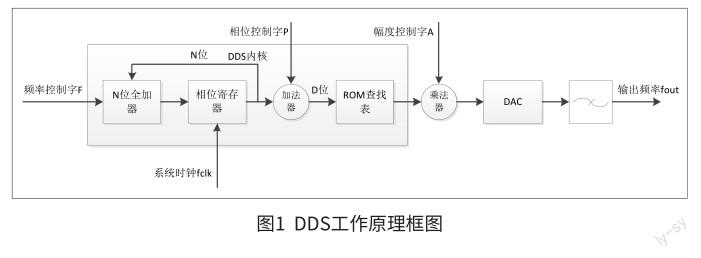

1 DDS基本工作原理

图1是DDS的工作原理框图[6],在DDS内核中作为DDS的系统时钟,N位全加器对频率控制字F和相位寄存器的N位输出值进行叠加运算[2][4],相位寄存器后信号流向分为两路,主路与相位控制字P通过加法器再次叠加运算后生成D位的ROM表寻址地址码,通过该寻址码在ROM查找表中找出当前频率控制字F和相位控制字P所对应离散波形幅度值数据;反馈路的信号等待下一个时钟信号与下周期的频率控制字F继续叠加,实时更新。当前系统时钟周期结束后,离散的波形幅度值数据構成了离散输出信号的波形,在DDS内核外幅度控制字A控制乘法器对输出信号的幅度值进行选取,后经DAC及低通滤波器组对信号进行D/A变换和滤波最终得到实际需要的波形信号fout。

2 中频信号模拟器的系统设计及实现

2.1 核心器件的选型及主要功能

DDS芯片选用成都振芯公司的GM4940,该芯片包含32位频率控制字F,16位相位控制字P,10位幅度控制字A,同时支持单点频、FSK、PSK、OSK、RAMP、混频、扫频等多种操作模式。支持多芯片同步,芯片内集成了单线SPI或8线SPI串行接口配置方式。总体满足高速、高动态、灵活的配置。DDS信号输出频率、相位及幅度如下:

MCU选用ST公司的ARM芯片STM32F407ZGT6。在系统中,MCU主要实现接收外部指令控制、内部逻辑控制、系统内外接口控制、电池充放电指示及电量监测、故障检测等功能。

2.2 系统硬件电路设计

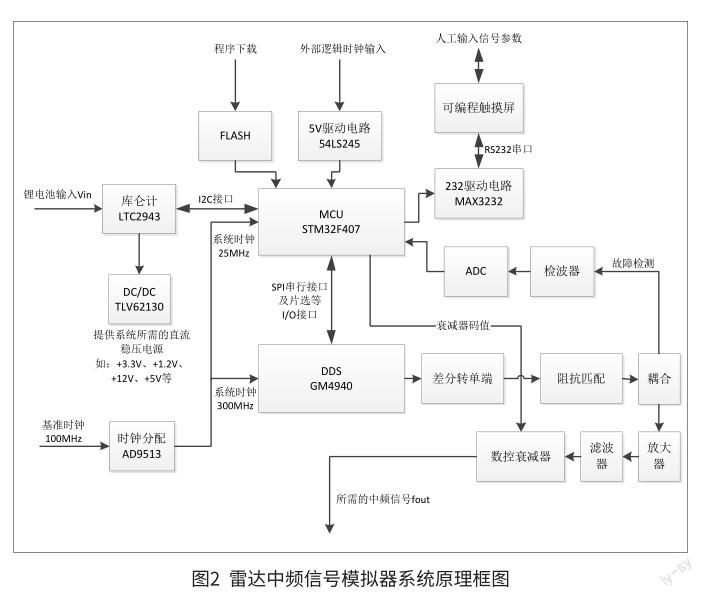

雷达中频信号模拟器的系统原理框图如图2所示。

系统的基准时钟源选用100MHz恒温超低相噪抗震晶振(OXLN),对所有芯片的系统时钟提供了可靠的时钟源并保证整个系统的相参性。时钟源首先经过时钟分配芯片AD9513将100MHz的基准时钟变为25MHz和300MHz两种系统时钟,分别提供给MCU芯片和DDS芯片。

DDS的内部寄存器通过SPI串行接口的方式进行配置,同时MCU通过通用I/O接口对其片选、IO_UPDATE、通道选择、多芯片同步等进行合理设置后DDS即可输出所需的信号波形,后端经过差分转单端(巴伦)、阻抗匹配、放大、滤波、数控衰减等信号整形手段,最终获得幅度、频率、相位、调制方式等信号参数合理的模拟雷达中频信号。

在外围电路中,MCU使用SW下载接口将程序通过配置项存入外部FLASH中。可编程触摸电容屏作为唯一的人机交互接口,可对模拟雷达中频信号的关键参数,如:频率、相位、幅度、多普勒速度、距离等进行设置,同时显示当前雷达中频信号模拟器的工作状态。内部通过RS232串口将信息转发至MCU中。外部输入的同步信号,如:雷达重复频率等通过245芯片驱动后发至MCU中作为逻辑控制的时序输入信号。此外,DDS的输出经过耦合、检波、A/D变换后将信号发至MCU中,用作负反馈故障检测。

2.3 ARM嵌入式软件设计

雷达中频信号模拟器系统的MCU软件为ARM芯片嵌入式软件,主体采用C语言在ST公司的Keil5中进行设计开发,软件设计时采用了RT-Thread嵌入式操作系统,减少软件设计周期,加强程序运行时的并行处理能力。RTThread嵌入式操作系统是源码公开的一种嵌入式实时操作系统(RTOS)[8-9],其可靠性、实时性、可裁减性、易用性和可确定性均有良好的表现,在近年内被广泛的应用于各高精尖的技术领域[10]。

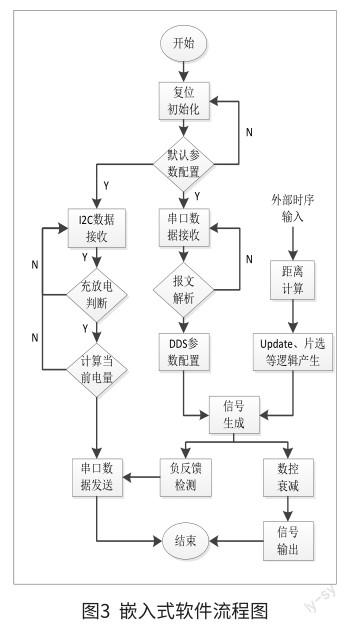

雷达中频信号模拟器的软件程序主要通过多个并行的中断服务函数来完成上电复位、初始化全局变量、I2C和RS232接口收發数据及解析、DDS信号生成的控制、负反馈检测等主要功能,软件流程图见图3。

程序开始运行后,首先进行系统内集成电路的上电复位及初始化全局变量,配置通用I/O接口和默认状态下的各芯片的寄存器。参数配置完成后进入并行处理,I2C接口主要用于与库仑计芯片之间的通讯,发送库仑计芯片的配置,接收当前电池充/放电状态及剩余电量,最终通过程序计算出百分比电量后经RS232串口送触摸显示屏显示输出。RS232接口主要用于与触摸屏之间的信息交互,接收人工信号参数装订,数据解析后通过SPI总线对DDS的各寄存器进行配置。有外部时序输入时,对人工装订的距离信息进行计算,内部通过TIMER定时器对时序逻辑进行合理的规划后,生成DDS最终所需的CS(片选)、I/O_UPDATE(波形触发)等信号。此外,DDS的输出信号经负反馈电路检测,对其输出的功率进行调整后作为最终生成的波形信号。

2.4 测试结果分析

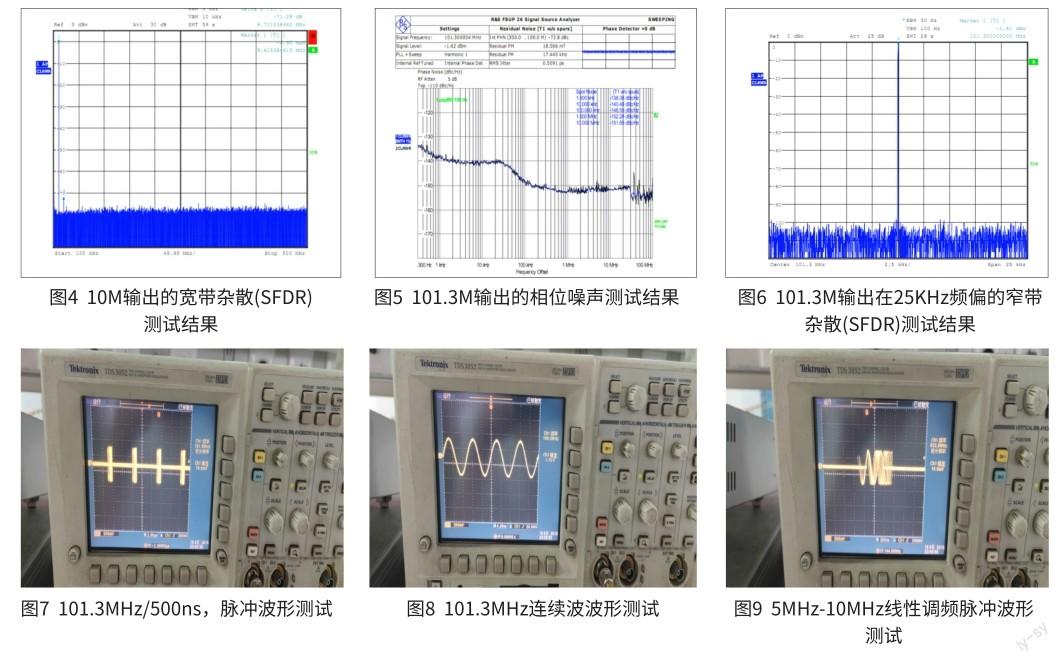

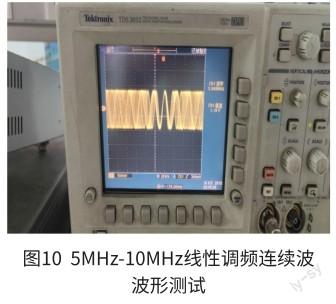

以10MHz、101.3MHz的中频信号,5MHz至10MHz的线性调频信号为例,对信号的连续波和脉冲两种波形及相关信号参数的进行测试。其中重点关注DDS生成信号的各项性能指标,如:相位噪声、窄带杂散、宽带杂散、频率稳定度、跳频稳定时间等。所有测试的试验结果由R.S公司的相噪分析仪、频谱仪和Tektronix公司的示波器采样所得,测试结果详见图4至图10。

以本文中所选信号频率为例,其信号特征中宽带杂散>70dBc,在25KHz频偏下窄带杂散>90dBc,相噪>-135dBc@1KHz,频率稳定度>±0.5ppm。在波形测试中,波形稳定、相位连续无截断,DDS芯片更新IO_ UPDATE时延<2ns,能够及时响应外部时序的控制,对连续波进行截取获得所需周期和脉宽的脉冲信号波形。

3 结语

采用本文中方法设计的雷达中频信号模拟器,通过嵌入式软件和硬件结合,充分发挥ARM芯片的高速和稳定性,能够通过低成本的数字电路实现DDS频率快跳、分辨率高、多种模式等特点。根据实际需要可作为雷达发射通道中的中频频率源使用,亦可作为某特定型号雷达的中频信号模拟器使用,功能多样、操作便捷、配置简单,满足工程需要。

参考文献

[1]倪宣浩,从彦超,武春飞,基于多路并行DDS的快跳频信号发射器设计实现[J],电子技术应用,2018,44(11):94-98.

[2]张铮,胡婷,基于AD9854的多功能高精度DDS信号源设计[J],电子科技,2017(3):182-184.

[3]贺军义,蒋坚,李男男. 基于FPGA的DDS信号发生器设计[J]. 计算机测量与控制,2017,25(2):231-233.

[4]李诗琪. 雷达信号模拟器的中频信号产生器设计[J]. 电子科技,2018(5):58-61.

[5]兰唯. 雷达宽带中频信号模拟研究及实现[D]. 长沙:国防科学技术大学,2016.

[6]熊娜. 基于DDS技术的雷达信号模拟器设计[J]. 电子技术与软件工程,2016(12):58-59.

[7]饶睿楠,王栋,余铁军,唐尧. 24GHz射频前段频率合成器设计[J].火控雷达技术,2019,48(1):66-69.

[8]杨巍. 信号模拟器软件的设计与实现[D]. 成都:电子科技大学,2018.

[9]李昌隆. 基于FPGA的DDS精确频率合成方法研究[D]. 西安:西北大学,2019.

[10]姚步堂,郭发勇. 手持式DDS信号源的设计与开发[J]. 电子世界,2019(14):119-122.

(作者简介:马绪铎,硕士,工程师,研究方向:雷达系统信号处理及数字电路设计;工作单位:西安导航技术研究所)