一种宽频率调谐范围的前馈型VCO 设计

2023-08-10岳旭龙

岳旭龙,唐 威

(西安邮电大学 电子工程学院,陕西 西安 710121)

近年来,自动驾驶、云计算、人工智能等热点应用的快速发展离不开高速数据的传输,SerDes(SERializer/DESerializer)技术可实现时分多路复用和点对点通信,已成为实现高速数据传输高效且经济的方式[1]。目前,Credo 公司已经基于TSMC 4 nm 工艺设计出了112G PAM4 SerDes IP,这套可覆盖各种传输距离且功耗可编程的IP,能够满足众多领域的需求。环形压控振荡器(Ring-VCO)是为时钟数据恢复电路(CDR)提供多相正交时钟的重要电路,其性能直接影响到CDR 恢复时钟的性能[2]。设计一款适用于CDR的高性能Ring-VCO 具有一定挑战性,在保证产生多相正交时钟的同时也应尽可能扩大频率调谐范围,以适应SerDes 不同传输速率下对时钟频率的灵活选择以及在非理想的温度和工艺环境下能得到所需频率[3]。采用前馈型VCO 是满足CDR 时钟需求的一种有效方法,通过前馈通路形成多个振荡环路,形成的较小环路也提高了振荡频率,而且由于纳米级CMOS 工艺的速度优势,前馈型VCO 可产生数GHz 频率正交偶数相的高速时钟[4]。当Ring-VCO 使用粗细调结构的频率调节电路时,可以使频率近似地跟随电流成比例变化,增大了频率调谐范围,所需振荡频率较低时可以通过减小电流来降低功耗。Sun 等[4]对8 相前馈型VCO 的振荡模式、频率和相位噪声进行了对比,在相同频率和功耗下,2 个主路径上的反相器和1 个前馈路径上的反相器(2D+1F)比4 个主路径上的反相器和1 个前馈路径上的反相器(4D+1F)结构有更好的相位噪声,但2D+1F 结构会产生双峰振荡的问题,需要额外的辅助通路来避免,增加了电路设计的难度。Wang[5]建立了前馈环形振荡器(FRO)的线性模型,并利用该模型对五级FRO 的最高振荡频率进行了优化,但不能产生偶数相正交时钟,不适用于CDR 电路。

本文根据半速率插值型CDR 架构,设计了一款具有频率粗细调节功能、可产生12 相时钟的前馈型VCO。频率粗细调节功能的实现,扩大了可调频率范围,保证了不同工艺和温度条件下能够得到所需频率;并且与4 相、8 相时钟相比,使用12 相时钟进行相位插值提高了插值线性度,从而可以更精确地恢复出CDR 的时钟,满足半速率插值型CDR 的时钟需求。

1 电路设计

VCO 是通过改变控制电压来改变信号输出频率的振荡电路,是一个闭环的反馈系统,电路振荡必须要满足巴克豪森准则[6]:

环形振荡器的振荡频率可以表示为:

式中:N为环形振荡器延迟单元的级数;td为将晶体管栅极电容充电到开关阈值电压的时间;Id为前一级近似恒定的电流;CG为MOS 管栅极电容;μn为载流子迁移率;Cox为单位面积栅氧化层电容;W和L分别为MOS 管沟道的宽和长;Vt为MOS 管阈值电压。为得到较高的振荡频率,设计VCO 时通常会选用较小的延迟单元级数[7]。

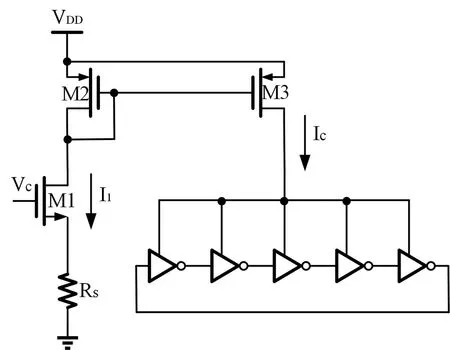

图1 为传统的VCO 电路结构,由于控制电压Vc与注入振荡器的电流Ic是平方关系,为了优化调谐线性度,使用了源极负反馈结构,该结构中电流大小为:

图1 传统的VCO 电路结构Fig.1 Conventional VCO circuit structure

式中:Rs为源级电阻;gm1为MOS 管跨导。当Rs≫1/gm1时,式(3)可变为I1=Vc/Rs,VCO 的调谐线性度得到了改善。使用源极负反馈结构后,尾电流源的输出电阻由原来只用一个NMOS 管的r0变成下式:

由式(4)可得,此结构的输出电阻增大,因此有更好的恒流源特性。同时,源极电阻的存在降低了源极负反馈的等效跨导,从而减小了M1 的闪烁噪声,但噪声的减小是以降低KVCO为代价的,最终导致频率调谐范围减小,无法保证在非理想的工艺和温度环境下得到需要的频率[8]。由于M3 管的源端直接与电源相连,电源上的噪声会直接传递到VCO 输出节点,使VCO 相位噪声性能变差。为了优化VCO 相位噪声和增大频率调谐范围,本文提出了一种数字编码控制的频率调节电路。

图1 所示由奇数级反相器组成的单端Ring-VCO很少用于高性能芯片中,因为它不能产生偶数相输出,而且相位噪声很差[9]。使用偶数级反相器组成的单端Ring-VCO 因不能产生非零频率会一直处于锁定状态,因此需要额外的电流通路改变振荡模式。使用前馈型VCO 是解决该问题的有效方法,通过增加前馈电流通路使某些模式下的自增益大于零频率模式时的自增益,从而使电路振荡,前馈电流通路的形成也提高了振荡频率。同时所设计的VCO 要保证相位插值型CDR 的插值线性度,理想情况下输出时钟的相位要与相位插值器的控制位呈线性关系:

式中:kPI为插值器的增益;n为控制码。若kPI不变,当n从0 增加到N时,输出相位从0 变化到2π。假设两个相邻时钟clk1=sin(ωt),clk2=sin(ωt+φd),权重系数分别为A1和A2,φd是两时钟的相位差,输出时钟信号可以通过对clk1和clk2进行相位插值得到:

令a=A1+A2cosφd,b=A2sinφd,对式(6)整理可得:

输出信号的幅度和相位是由A1、A2和φd决定的,即:

其中,A1和A2与插值控制码n有关,一般将其调整为线性关系,由式(5)和式(9)可知,提高插值线性度需要使clk1和clk2之间的相位差φd越小越好,这样每次调整的相位步进φd/n就越小,插值得到的时钟相位更精确[10]。因此相对于产生4 相位(φd=90°)和8 相位(φd=45°)的VCO 相比,产生12 相位(φd=30°)的VCO 可以提高相位插值电路的插值线性度。

采用12 相时钟的前馈型VCO 不仅可以产生高频正交时钟,也保证了较好的插值线性度。数字编码控制的频率调节电路不仅优化了电路噪声性能,也增大了频率调谐范围。下面将分别介绍前馈型VCO 电路和频率调节电路的设计。

1.1 前馈型VCO 电路设计

如图2 所示,所提出的前馈型VCO 电路共由24个反相器组成,主路径和前馈路径上的反相器分别用D 和F 表示。如果只有主路径上的12 个反相器将无法振荡,通过添加前馈路径的12 个反相器来改变主路径输出节点的相位,使主路径输出节点与频率有关的相移可以达到30°,因此经过12 级反相器与频率有关的相移达到360°,满足振荡条件。以X1~X5~X1为例,其中主路径上X1~X54 个反相器的尺寸是相同的,通过增大前馈路径X5~X11 个反相器的尺寸,可以增加前馈路径输出节点X1的充放电电流,加快反相器的电平翻转速度。经过主路径上的4 个反相器和前馈路径上的1 个反相器,形成的5 级环形振荡器极大提高了振荡频率。这样所提出的VCO 既可以产生12 相正交时钟的输出,又提高了振荡频率。

图2 所提出的前馈型VCO 电路Fig.2 The proposed feed-forward VCO circuit

前馈型VCO 形成的5 级Ring-VCO 输出节点的相位如图3(a)所示,延迟单元等效模型如图3(b)所示,采用主路径和前馈路径共同对输出节点Vn注入电流的方式来加快反相器的电平翻转速度,并改变输出节点的相位,从而满足振荡条件。

图3 (a)构成的5 级Ring-VCO 相位关系;(b)延迟单元等效电路模型Fig.3 (a) Constituted 5-stage Ring-VCO phase relationship;(b) Equivalent circuit model of the delay unit

处于稳定振荡状态的振荡器,任意两个节点的信号具有恒定的相位关系,因此对于Vn与Vn+4节点可以得到:

式中:φ1为Vn与Vn+4之间的相位差,因此φ1=2π/3。根据延迟单元等效电路由基尔霍夫电流定律可得:

将式(10)代入式(11)可得单级延迟单元的传输函数为:

式中:R为反相延迟单元的等效输出电阻;C为每个节点上反相延迟单元总的寄生电容;gm为主环路中反相延迟单元的跨导;gm1为前馈支路的跨导。所得到的传输函数需要满足巴克豪森判据中的相位条件:

式中:θ为相邻延迟单元的相位差。两边同取正切函数得:

可得频率表达式为:

振荡频率ω的第一项是主环路的工作频率,第二项为添加前馈支路后频率的增加量。振荡频率ω主要与相邻延迟单元间的相位差θ(Ring-VCO 的级数N)、反相延迟单元的等效负载电阻R、每个节点反相延迟单元总寄生电容C和前馈支路跨导gm1密切相关,其中增加级数N或者使等效负载电阻和总寄生电容C增加会降低频率,增加前馈支路的等效跨导gm1可以增加振荡频率,但其增加量有一定限制。

除了满足相位条件以外,还需要满足巴克豪森幅值条件,即:

将式(14)代入到式(16)中整理可得,当gm1R<2 时:

在上述约束条件成立时,满足巴克豪森的幅值条件,振荡器可以起振。

1.2 频率调节电路设计

所提出的频率调节电路如图4 所示,实际上是一个控制电压转换为电流(V/I)的电路,由频率粗调部分和细调部分组成。频率粗调部分通过控制传输门的开关来控制工作频段,可同时打开多条通路,增大调谐范围。电流经PMOS 复制到频率细调部分对相应频段内的频率进行细调。其中频率细调部分的电流源采用了共源共栅结构,有效避免了电源耦合到振荡器输出节点的噪声。

图4 所提出的频率调节电路Fig.4 The proposed frequency regulation circuit

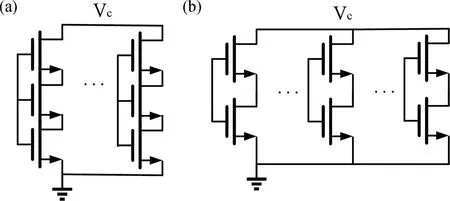

频率粗调部分由图4 左侧带传输门的NMOS 单元组成,NMOS 管栅端由固定电压Vb偏置,通过控制每条路径NMOS 管栅端传输门的开关来控制开启电流支路的条数,从而改变粗调电流的大小,最终改变频率使其处于不同的频率区间,其中控制位freq_sw<9:0>由二进制码控制。采用图5 所示改变级联晶体管与并联晶体管个数的方式实现图4 NMOS 单元M0~M9 权重分别为1,2,4,8,16,32,64,128,256 和512电流的产生。M7'为基准电流管,尺寸与M7 相同,因此M7'流过的电流权重Iref也为128,且不受传输门的控制,处于恒导通状态。NMOS 部分产生的电流经PMOS 电流镜复制到频率细调部分,以基准管电流Iref为参考,流经Iref_total的电流为:

图5 频率粗调部分NMOS 单元的实现。(a)并联2 组和4 组;(b)并联5 组和9 组Fig.5 Implementation of NMOS cells in the coarse frequency regulation section.(a) Parallel connection of 2 and 4 groups;(b) Parallel connection of 5 and 9 groups

式中: 8>m≥0,m代表将电流权重换算为Iref权重之后可开启电流支路的条数。

频率细调部分主要由I_copy<267:0>恒通部分、int_adjust<9:0>编码控制部分以及dn/up 控制部分组成。I_copy<267:0>恒通,电流权重为268×8;int_adjust<9:0>采用了不同类型的编码方式,其中低5 位采用二进制编码,权重分别为0.5,1,2,4 和8;高5 位采用温度计编码,权重为31×16,细调部分高位采用温度计编码以减小控制码切换时产生的电流毛刺,降低因毛刺噪声产生的精度损失。但在控制位多的场合,全部使用温度计编码会造成电流支路数呈指数形式增加,造成连线杂乱,难以实现。而对于控制位较少的电路,可以使用本文提出的两种编码方式结合的方法。dn 与up 根据相位比较结果来补充调节VCO 频率,其权重可调节的范围为4~28。最终输出的总电流为:

式中: 0.25>p≥0,p为int_adjust<9:0>和dn/up 两个细调控制部分的电流权重换算为Iref权重后所占的比重。通过对注入VCO 的整体电流Iout_total进行粗细调节,实现对振荡频率的精确调节。

2 相位噪声分析

在环形振荡器中,相位噪声主要是由器件的热噪声和闪烁噪声共同决定的,通常利用脉冲灵敏度函数Γ(ISF)来分析相位噪声,Γ表示振荡波形的幅度和相位对注入脉冲信号的灵敏度[11]。中心频率的较小频率偏移Δω处1/f噪声占主导,这个区域为1/f3区,随着Δω继续增大,热噪声将占主导,这个区域为1/f2区,当Δω很大时,只存在背景噪声。其中1/f3区噪声表示为:

式中:qmax为相关节点电容上的最大电荷量;ω1/f是1/f2与1/f3区的转角频率;是有源器件噪声电流的功率谱密度;c0是直流分量,且c0=2Γdc,Γdc是脉冲灵敏度直流分量,可表示为:

式中:η为振荡波形最大斜率与单级延迟单元延迟时间的乘积,通常接近于1;A与上升下降沿对称性有关。使用12 级前馈型VCO 在振荡过程中对输出节点负载电容充放电电流的匹配,保证了上升下降沿的对称性,使A近似为1,Γdc接近0,从而使1/f噪声对相位噪声的贡献降到最低。1/f2区噪声可表示为:

式中:Γrms为ISF 的均方根值。式(22)中可分别表示为:

式中:γ为与沟道长度有关的热噪声系数;gd0为漏源电压为0 时的电导。由式(23)和式(24)可知,适当增大N和最大化上升下降沿斜率可以降低ISF 的均方根,后者可由前馈型VCO 引入的额外电流通路来实现,使用长沟道器件不仅可以减小gd0,还可以使γ处于较小值,从而减少热噪声对相位噪声的贡献。延迟单元中的器件都使用了反相器,使用较少MOS 管减小了噪声源,优化了相位噪声[12]。

另外,电源电压的波动也会引起振荡频率的变化,导致相位噪声恶化,VCO 振荡频率对电源电压的敏感度可表示为:

式中:μ为迁移率;L为沟道长度。为了降低VCO 对电源噪声的敏感度,应尽可能使用长沟道MOS 器件,采用共源共栅结构的屏蔽作用可以进一步降低电源电压对VCO 振荡频率的影响,从而优化相位噪声。同时,产生的差分时钟信号也有效抑制了环境噪声对VCO 相位噪声的贡献。

3 结果与讨论

基于22 nm 工艺版图设计规则对VCO 电路进行了版图设计,核心部分是12 个相同的VCO 延迟单元,其版图如图6 所示,该VCO 版图尺寸为41.1 μm×27.9 μm。

图6 所提出VCO 电路版图Fig.6 Proposed VCO circuit layout

基于22 nm CMOS 工艺,采用Cadence 平台Spectre 软件对VCO 电路进行后仿真,在8 GHz 时钟频率下,该VCO 输出的12 相时钟波形经过buffer 整形之后,如图7 所示,该波形时钟周期约为0.125 ns。

图7 VCO 输出12 相时钟波形Fig.7 VCO output 12-phase clock waveform

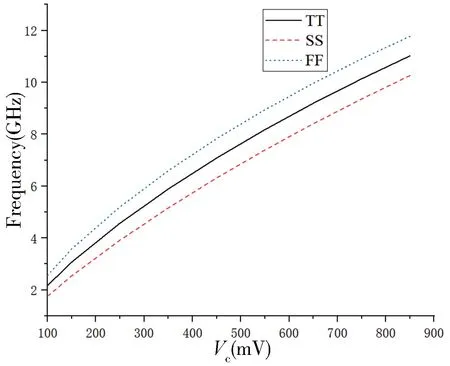

在TT、FF 和SS 三种工艺角下对控制电压Vc进行扫描,当控制电压的变化范围为100~850 mV 时,TT工艺角下振荡器的输出频率范围为2.21~11.23 GHz,得到频率f与控制电压Vc的关系曲线如图8 所示,仿真结果表明,在整个控制电压范围内,该VCO 具有较好的调谐线性度。

图8 VCO 振荡频率与控制电压Vc的关系Fig.8 VCO oscillation frequency versus control voltage Vc

图9 为所设计的VCO 在TT、FF 和SS 三种工艺角下相位噪声的仿真结果。其中TT 工艺角下相位噪声性能最好,在偏离本振信号1 MHz 频率处的相位噪声为-93.1 dBc/Hz,偏离本振信号10 MHz 处的相位噪声为-114.05 dBc/Hz。

图9 8 GHz 处VCO 的相位噪声曲线Fig.9 Phase noise curves of VCO at 8 GHz

本文提出的VCO 与其他文献的VCO 以工艺、电源电压、调谐范围、相位噪声和功耗为指标参数进行了对比,如表1 所示。其中工艺使用了较先进的22 nm 工艺,相对于文献[4,13-15],所提出的VCO 具有非常宽的调谐范围和较高的振荡频率,在相位噪声方面,所提出的VCO 略优于文献[4]和[15],在功耗方面也比文献[13-15]要低一些。整体结果显示,所提出的VCO 拥有很宽的调谐范围、较好的相位噪声和较低的功耗。

表1 与其他文献VCO 性能对比Tab.1 Comparison of VCO performance with other literatures

4 结论

本文基于22 nm 工艺,设计了一种可产生12 相正交时钟、宽频率调谐范围的前馈型VCO。该VCO 通过前馈通路构成5 级Ring-VCO 提高了振荡频率;具有粗细调功能的频率调节电路增大了频率调谐范围,实现了对频率的精确调节。仿真结果表明: 所设计的VCO 在控制电压范围为100~850 mV 时,输出频率范围为2.21~11.23 GHz,且具有良好的调谐线性度,当工作频率为8 GHz 时,振荡器的相位噪声为-93.1 dBc/Hz@1 MHz,-114.05 dBc/Hz@10 MHz,功耗为5.18 mW。基于上述特性,该VCO 适用于相位插值型时钟数据恢复电路。