一种便携式多通道时间同步应变采样系统的设计∗

2023-08-04文聪楠张晓明赵文科

文聪楠 张晓明,2 赵文科

(1.中北大学电子测试技术国家重点实验室 太原 030051)(2.中北大学仪器科学与动态测试教育部重点实验室 太原 030051)

1 引言

随着近年来相关领域的快速发展,应变测试需求快速增长,应变采集系统的通道数也相应增加[1],这就对测量采集的通道数和时间同步性提出了要求。工程实践表明,需要多通道同步采集的场合,实际上是指需要在各个通道的不同传感器测量点处实现同时采样,并非是指在采集系统本身的端口处实现同时采样,两者具有明确差异[2],同时应力应变测试的部分测试场合处于野外环境,所以在设计测量系统时也应满足一定的便携性。

2021 年,董力纲等[3]设计了一种48 路同步应力应变采集系统,但设计结构较为复杂,外围电路较多且采集时间同步性没有进行确定。2022 年,江红等[4]提出一种信号的时间轴校准方法,采用插值法校准信号,但不适用于快速测量场合。2020年,顾宪成等[5]基于LabVIEW软件开发了振动与应变测量系统,设计结果也同样存在测量结构复杂和未能确保采样结果时间同步性等问题。

考虑到上述问题,本文设计了一种基于STM32H743 高性能单片机的便携式多通道时间同步应变采样系统。使用全桥电路结合仪表放大器来完成应变信号到电信号的转换,结使用单片机完成多通道采存,对信号进行多次测量处理得到相邻通道的采样时间差并对采样结果进行时间同步补偿,在满足便携性的基础上,达到多路时间同步采样的目的。

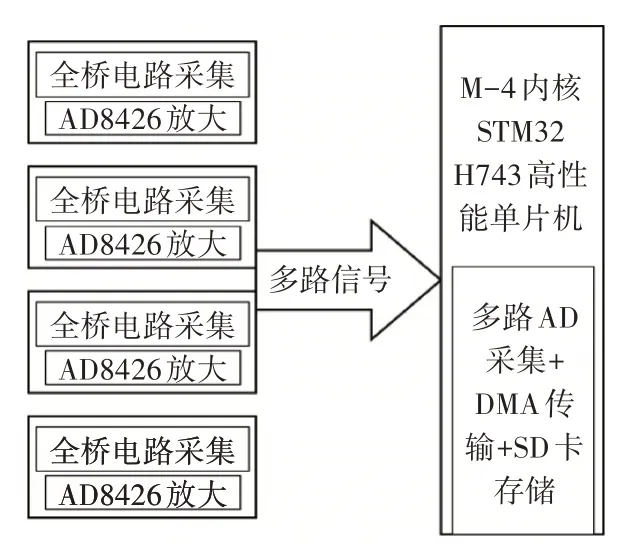

2 采集放大部分设计

针对多通道应力应变测量中外围电路复杂、采样起始时间不一致、时间同步性差等问题,根据应力应变值变化的连续特性,依靠仪表放大器、H743内部高精度定时器、内部多通道ADC 以及支持任意互联的DMA,结合FATFS 文件系统和SDMMC 控制器,通过对相邻通道采样结果进行多次测量进行时间同步补偿的事后插值法,设计了一种针对小面积内多点应力应变测量的便携式多通道同步采集存储系统。系统硬件由采集放大部分、控制采样部分和数据存储部分组成。采集放大部分主要由多路全桥采集电路和仪表放大器组成。控制采样部分均由H743 单片机完成,通过单片机最小系统即可满足测量需求,存储模块采用FATFS文件系统挂载SD卡对数据进行存储。系统总体结构如图1所示。

图1 系统总体框架

3 采集放大部分设计

3.1 应变采集原理

测量物体应变的传感器多种多样,电阻应变片因其制造工艺简单、成本低廉、方便检测等原因被广泛应用于实际工程测量中[6],且目前应变片的加工工艺已经可以将敏感栅栅长做到0.1mm[7],便于实现小型化,能满足本系统设计的便携性需求,方便采用惠斯通电桥完成由应变到电信号的转换[8]。使用时,将电阻应变片使用专用的粘结剂粘结在被测构件表面上,当被测构件发生变形时,电阻应变片会跟随构件发生变形,从而改变电阻应变片上的金属丝的形状,金属丝电阻发生改变[9],引起电信号的变化。

3.2 应变采集设计

实际使用中需要将电桥输出信号进行放大,放大电路是每一个测量仪器必备的电路,它不仅可以将微弱信号无失真地放大至采集电路可接受的范围内,还可以将较大的信号进行衰减,以扩大信号输入范围,提高测量仪器的测量量程,扩展测量仪器的适用方向[10]。每一路电桥输出采用AD8426仪表放大器进行放大。单通道应变采集电路如图2。

图2 单通道应变采集电路

4 采存控制部分设计

4.1 STM32H743简介

本系统中采集存储部分选用STM32H743IIT6单片机(以下简称H743)来完成。其采用的M7 处理器在采集数据的速度、精度以及可靠性上相较F4、F2 系列处理器都有大幅度的提高[11~12],同时H743 拥有三个互相独立的分辨率最高可达16 位的ADC,最高单通道采样率可达3.6MHz。每个ADC 的复用通道多达20 条,能以其最小系统电路配合SD卡插槽满足本系统的采样存储部分需求。

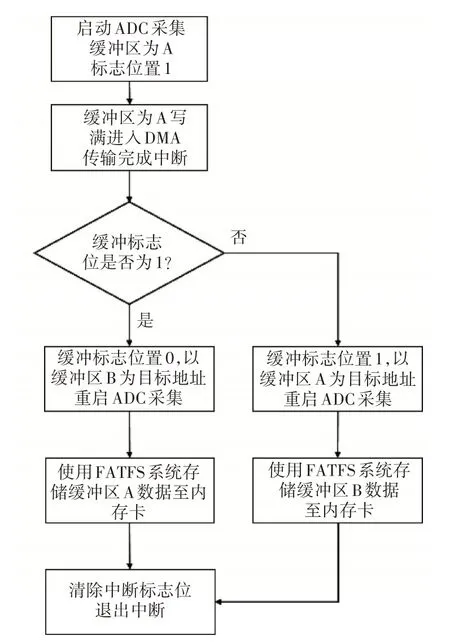

4.2 多路采集存储设计

为了简化外围电路考虑,本设计通过确定采样率来确定采样时间轴。为了准确确定采样结果的时间轴,系统通过使用内部高精度定时器来产生PWM波,使用其上升沿来触发ADC采样[13]。此时,ADC 实际采样率由PWM 波周期决定,预先在ADC的配置代码中使能各路ADC 通道的I/O 口,调用通过PC 端串口助手输入而更改的全局变量来更改PWM 波周期配置和ADC 采样通道数及其序列配置。同时为了提高ADC 采样的幅值精度,降低输入阻抗,可在每个ADC 接口前配置一个跟随器。使用DMA 传输完成中断进行乒乓操作以实现同步采存,具体实现流程如图3。

图3 DMA传输完成中断乒乓操作

4.3 时间同步补偿及误差分析

对于H743 的三路ADC 而言,通过同一PWM波信号上升沿触发采样时,三路ADC 的启动均受此信号触发开始预设序列的采样。此时的时间同步性受到ADC 时钟频率影响,三路ADC 的启动时差不超过一个ADC 时钟周期,但是同一ADC 的采样通道序列上的相邻两通道采样时间差无法在硬件层面上来确定。对于同一ADC 的相邻采样通道而言,后一个通道要在前一个通道的采样结果产生并且写入专用寄存器之后才会开始AD 转换和采集。

针对以上问题,系统采用事后时间补偿的插值法来补偿同一ADC 不同通道的时间同步性。在配置好采样率后,设此时单通道采样周期为T,使用单片机多次测量已知锯齿波周期信号,令第一通道和之后某通道同一个被测信号周期的测量数据相减求均值,设均值为U1,利用Matlab 对后通道所测得的锯齿波信号进行解卷绕拟合[14]得到解卷绕拟合斜率,设斜率为k1。设两通道平均采样时间差为ΔT1。

此时有

得到ΔT1后,在实际采集数据时,对于后通道的数据,可以通过取测量结果中相邻两点连线的斜率ΔK 结合所测得的ΔT1来对测量结果进行时间同步性补偿。

设后通道第N 个采样点采样结果为UN,第N+1个采样点采样结果为UN+1,补偿后第N+1个采样点结果为U,则有

此时有

将式(3~4)代入,可得

通过将后通道相邻两采样点间的电压变化曲线近似看作直线求得斜率,用单通道采样周期减去两通道平均采样时间差,近似的得到后通道第N+1个采样点与前通道第N+1 个采样点时间同步的采样结果。此时T、k1、U1均为已知量或测量量,在计算U时,可以将看作已知量,将其等效为k,此时U与ΔU为线性关系,有

根据上述的时间同步补偿的插值法计算方式可知,时间同步计算的主要误差来源在ADC 的采样误差上,设平均采样误差为ΔU1。此时ADC 的平均采样误差ΔU1与补偿后的第N+1 个采样点的电压值U之间关系如式(3)~(7)。

5 采样实验验证

5.1 多通道采样验证

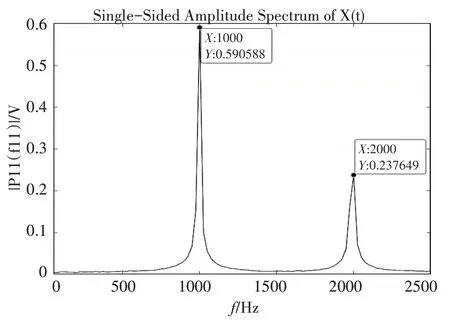

将系统调整到16位分辨率模式,6路AD通道,设置单通道采样频率为200kHz,然后对幅值为2.2V的直流信号进行采样,对比万用表测量值得到系统采样幅值误差。然后对偏置为2.2V、幅值为2V、频率为1kHz 的锯齿波信号进行采样,以200kHz 为采样率确定时间轴,再对被采样信号进行快速傅里叶变换得到被采样信号频谱,结合采样结果的频谱来反验系统采样率。各路幅值误差及如表1,锯齿波采样结果频谱如图1(以ADC1CH1为例)。

表1 ADC采样测试

从频谱分析中可以看出,主要频率分量出现在1kHz,与实际信号频率一致,可知采样频率设计较为准确。整体采样幅值平均误差为2.0mV。

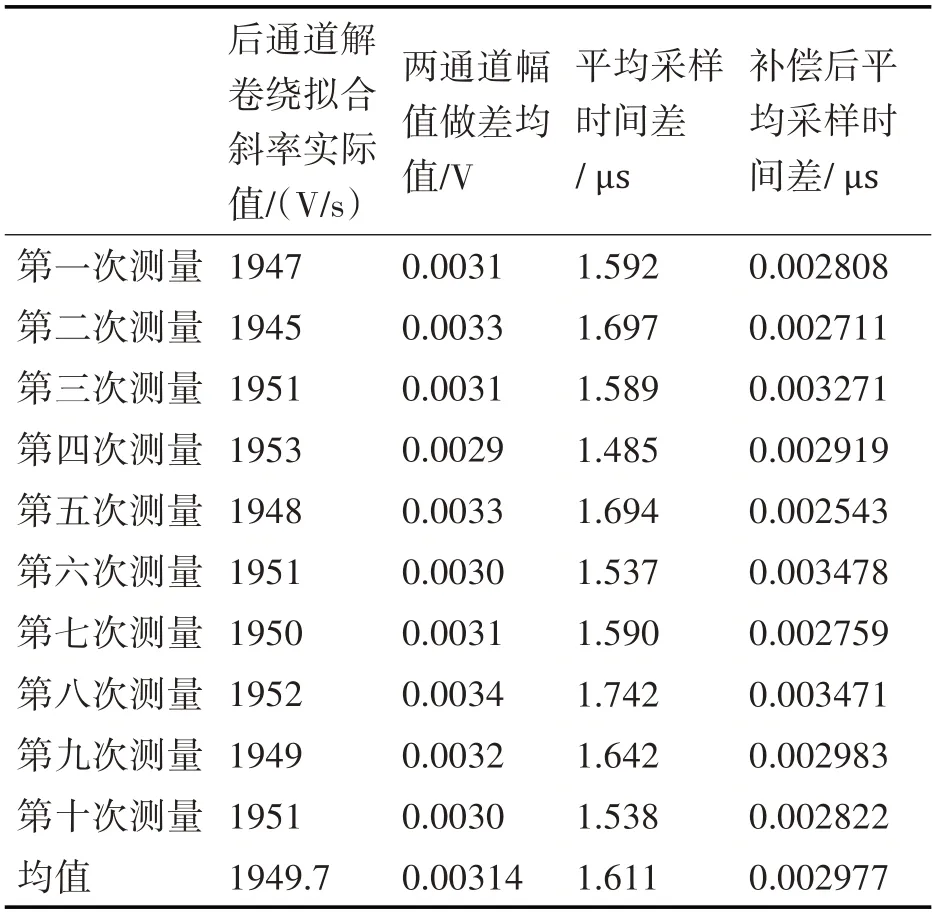

5.2 时间同步验证

验证时间同步性时需要前后通道采样结果做差,考虑到锯齿波信号只有上升沿,方便前后通道做差,所以采用锯齿波信号来验证时间同步补偿。仍以本文5.1 节测试配置验证时间同步,多次重复测试后,根据本文4.3 节中提出的插值采样时间补偿方式,对后通道采样结果进行时间同步性补偿,通过Matlab 软件实现实际数据计算和处理,由实际测试结果可知,经过时间同步补偿后的两通道平均采样时间差有了明显的降低,补偿后时间同步精度平均可达99.814%,测试数据如表2。

表2 ADC采样测试

图4 被采样信号频谱

6 结语

本文针对多点应力应变同步测量中,多通道测量数据时无法保障时间同步性和测量电路结构不便于小型化的问题,设计了一种基于STM32H743高性能单片机的多通道同步采样系统。并设计模拟采样实验,验证了在200kHz采样率下,多通道A/D采样电压误差在2mV 左右,补偿后时间同步精度平均可达99.814%,并给出了平均采样误差和补偿后电压值间的关系,能够完成多点应力应变同步测量的需求。该系统结构简单,测量电路体积较小,布设安装方便,适用于常温下多种应力应变测试环境,为多点应力应变时间同步测量提供了基础。