一种高增益、高带宽全差分运算放大器的设计

2023-08-03彭春雨张伟强蔺智挺吴秀龙

彭春雨,张伟强,蔺智挺,吴秀龙

(安徽大学集成电路学院,合肥 230601)

1 引言

在过去的几十年里,人们在增益提升(Gainboosing)技术的基础上提出了采用不同的电路拓扑来获得高增益和高带宽的运算放大器(运放)。起初,Gain-boosting 技术的典型应用是在单级套筒式共源共栅(Cascode)结构中[1],此结构的增益得到了显著的提升,但是由于输出电压摆幅受限,极大地限制了此结构的应用场景。增益提升折叠式运放结构[2-4]随即被提出并被广泛使用,虽然此结构输出电压摆幅得到了扩大,但增益提升有限,并不能满足当下高性能模数转换器的要求。基于折叠式级联的增益提升运放电路[5-8]通过级联的方式进一步提升了运放的增益,但是由于级联数目的增加和寄生电容的原因,此结构存在功耗大和稳定性差的问题。双增益级联提升技术[9-11]可以显著提高增益,同时主运放的电路结构也相对简单,但是辅助运放需要不同的偏置电路,采用此技术也面临功耗过大的问题。可见,在追求高增益、高带宽的同时,要求运算放大器功耗和输出电压摆幅等性能良好是Gain-boosting 技术当下的研究瓶颈。

针对以上问题,本文设计了一款主运放采用宽输入共模范围的全差分折叠式共源共栅运算放大器,该结构在扩大输入电压范围的同时增大了运放的整体输入跨导,从而提高了运算放大器的增益和带宽。采用Gain-boosting 技术,使用三输入管运放作为2 个辅助运放。在主运放带宽不变的条件下,进一步提升了主运放的增益,从而达到了高增益、高带宽的目的。采用三输入管的辅助运放结构更为简单,并与主运放共同使用一个偏置电路,极大地节省了电路总功耗。主运放采用高线性度的开关电容共模反馈(CMFB)电路来稳定其输出电压。在1.8 V 供电电压和5 pF 负载电容下,低频增益可达115 dB,增益带宽积(GBW)为209 MHz,功耗仅为2.8 mW。

2 运算放大器的分析与设计

2.1 增益提升技术分析

使用Gain-boosting 技术可以将Cascode 结构的输出阻抗进一步提高,电路增益随之提升[12],但是没有改变运算放大器的输入跨导与负载,所以并不会改变原运算放大器的GBW,类似于将运算放大器主极点的位置拉高,GBW 保持不变。增益提升电路原理如图1所示,其中Vref为参考电压,Vin为输入信号,Vout为输出信号。输出阻抗rout[13]为

图1 增益提升电路原理

其中:gm2为M2 的跨导,ro2和ro1分别为M2 和M1 的输出阻抗,Aadd为辅助运放的直流增益。

需要注意的是,使用Gain-boosting 技术会不可避免地带来一对零极点对(Doublet),且此Doublet 一般在辅助运放的增益带宽积附近,即辅助运放的增益带宽积在ωAux处,主运放的-3 dB 频率在βωAux处,第二极点位置在ω2处。为使Doublet 对系统响应的影响小于主运放带宽的影响,同时考虑辅助运放环路的稳定性,要求βωAux<ωAux<ω2[13]。

文献[14]对增益提高技术频率响应进行了详细分析,可以将M1 的尺寸设计得比较小,M2 的尺寸尽可能大,达到将引入的零极点对重合的目的。同时可以在辅助运放的输出端即X 点处再增加补偿电容和调节辅助运放的宽长比,达到零极点远离主运放单位增益频率点的目的。

2.2 偏置电路

本文提出的主运放与2 个辅助运放的结构大致相同,为节省功耗和达到电流复用的目的,可以使用同一个偏置电路共同偏置。为了增大输出电压的范围,偏置电路选择宽摆幅的低压共源共栅结构[15]。偏置电路如图2 所示,其中P9 和N5 管的栅长分别是P4 和N3 管栅长的4~5 倍,这样做的目的是给C 点和D 点提供合适的电压,减小MOS 管上的压降,从而扩大输出电压摆幅。

图2 偏置电路

P1~P4 和N1~N4 的宽长比与主运放和2 个辅助运放的宽长比相同,只是并联个数(Multiplier)的取值有所不同。这样设计可以把偏置电路和辅助运放相应管的Multiplier 成比例缩减,把偏置电路和辅助运放的功耗降到最低。

2.3 运放电路结构分析

主运放电路结构如图3 所示,采用的是宽输入共模范围全差分折叠式共源共栅运放结构。输入对管由一对NMOS 管和一对PMOS 管共同构成,当输入电位较低时Mp1 和Mp2 导通,当输入电压较高时Mn1和Mn2 导通。这种结构在扩展了输入共模范围的同时,输入跨导提高至传统运放结构的2 倍。根据2.1 节的理论分析,为了避免使用Gain-boosting 技术时引入Doublet 对运放频率造成影响,在主运放设计时可以使Mp1、Mp2(Mn1、Mn2)的尺寸取值小于Mup1、Mup2(Mun1、Mun2)的尺寸。

图3 主运放电路结构

三输入管辅助运放电路结构如图4 所示,同样选取输入和输出更为灵活的折叠式共源共栅运算放大器,在其输入端相应加入一个管子,省去了辅助运放的共模反馈电路[16],这种电路结构更为简单也更加高效。其中,VPC和VNC是当主运放不加辅助运放时A、B两点的电位,Cc是为了避免辅助运放引入的零极点对系统的稳定性造成影响所加的补偿电容。

图4 三输入管辅助运放电路结构

2.4 共模反馈

以图4(a)中NMOS 管输入的辅助运放Au1 为例,解释辅助运放如何利用电流共模反馈稳定输出共模电压的过程,辅助运放Au2 的原理与其相似。

1)假设由于晶体管失配、工艺制造等原因,造成共模电压Vin1-和Vin1+升高;

2)由于M1 和M2 栅极电压上升,导致原先流过的一个单位电流I 略微增加,而M4 的电流2I 保持不变,流过M6 支路的电流减小,则输出的共模电平Vo-和Vo+下降;

3)辅助运放Au1 的输出共模电平抬高,导致主运放中的A 点即辅助运放的输入端电位下降,抵消Vin1-和Vin1+电压升高的趋势,从而达到稳定辅助运放共模的目的。

主运放采用的是开关电容CMFB,与连续时间CMFB 结构相比,开关电容CMFB 具有对输出电压范围没有限制[17]、高线性度(电路中只使用无源器件)、CMFB 环路不会引入新的寄生零极点且功耗低等优点[18]。

本文采用的开关电容共模反馈时序及电路结构如图5 所示,其中开关控制时序为2 相非交叠时钟,Φ1为采样态时钟,Φ2为放大态时钟,T 为非交叠时钟周期。VCM是给定的输出稳定电平值,Vb1为运放电路设计时电流偏置工作电压值,C1取值一般为C2的4~5倍[19]。开关电容共模反馈的过程为

图5 开关电容共模反馈时序及电路结构

其中,Vcm-out为主运放实际输出共模电平,VCMFB为共模反馈电压,an为输出共模电平与反馈电压的差值,b 为给定输出共模电压与偏置电压的差值,n 代表第n 个开关时序。经过数个开关电容时序,an与b 趋于相等,即

最终VCMFB稳定在Vb1附近。

3 仿真结果

通过理论分析与设计过程描述,本文基于55 nm CMOS 工艺,对全差分运算放大器电路进行了仿真。在供电电压为1.8 V 时,本文提出的全差分运算放大器的交流小信号(AC)仿真曲线结果如图6 所示。运放的低频增益约为115 dB,GBW 为209 MHz。宽输入摆幅结构增大了主运放的输入跨导,在提高增益的同时也提升了速度。在不影响单位增益频率的情况下,采用增益提升技术显著提升了运放的直流增益。减小辅助运放输入对管的尺寸并在辅助运放的输出端加上补偿电容的原因是使运放整体具有良好的频率特性,相位裕度约为71°。

图6 运算放大器的AC 仿真曲线

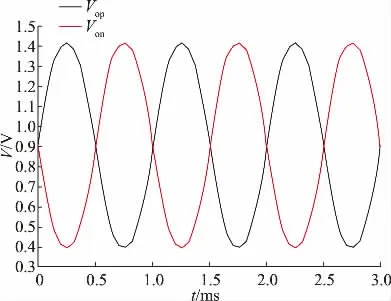

全差分运算放大器的输出摆幅仿真曲线如图7 所示,Vop、Von分别对应运放差分正端输出和负端输出信号。可以看出,单端输出摆幅为1Vpp,差分输出摆幅为2Vpp,Vpp代表输出电压峰峰值。电路消耗的总功率为2.8 mW,由于部分电流复用的原因,其有着较高的功耗效率。本文与其他文献提出的运算放大器参数对比如表1 所示。

表1 本文与其他文献中运放的参数对比

图7 运算放大器的输出摆幅仿真曲线

4 结论

本文基于宽输入共模范围的折叠式共源共栅运算放大器,采用Gain-boosting 技术,基于开关电容共模反馈原理设计了一种高增益、高带宽的全差分运算放大器。辅助运放采用结构更为简单的三输入管,并与主运放电路共用一个偏置电路,极大地节省了电路的功耗;同时在辅助运放输出端加上补偿电容,使运放整体具有更好的频率特性。仿真结果表明,该运放具有高增益、高带宽的特点,其他性能也较理想,适用于高精度流水线ADC。