基于FMQL和HT-61843GB的1553B总线RT端的设计与实现

2023-06-17卢韦平

卢韦平

(中兴通讯,陕西 西安 710065)

0 引 言

1553B 总线是飞机内部时分制指令响应式多路传输数据总线[1-5],最早应用于20世纪70年代末美国军用飞机,近年来逐步扩展到航天、坦克、舰船等领域。我国从20世纪80年代开始对1553B 总线接口进行研究,由于早期研究受工艺和器件的限制,设计的产品体积大、集成度不高。随着计算机技术的快速发展,特别是大规模集成电路的应用,设计的1553B 总线产品体积减小、集成度有所提高。本文采用FMQL[6]中的PL 部分配置HT-61843GB 器件,读取BC 端发送的数据;然后再通过AXI 总线传递给PS 端进一步处理,实现了1553B 总线RT 端[7]的功能。

1 硬件介绍

硬件关键器件包括FMQL、HT-61843GB、变压器。

1.1 FMQL 介绍

FMQL 芯片采用复旦微电子的全可编程PSOC 芯片,它在单芯片集成了四核高性能处理器(Processing System,PS)和可编程逻辑(Programmable Logic,PL),PL 部分为PS 部分的可扩展单元,它既可以配合PS 完成一些外部逻辑的处理,也可以利用PL 部分并行、硬件处理的特点,构成PS 中算法的一个外部协处理单元,形成一个强大的算法加速器。

1.2 HT-61843GB 介绍

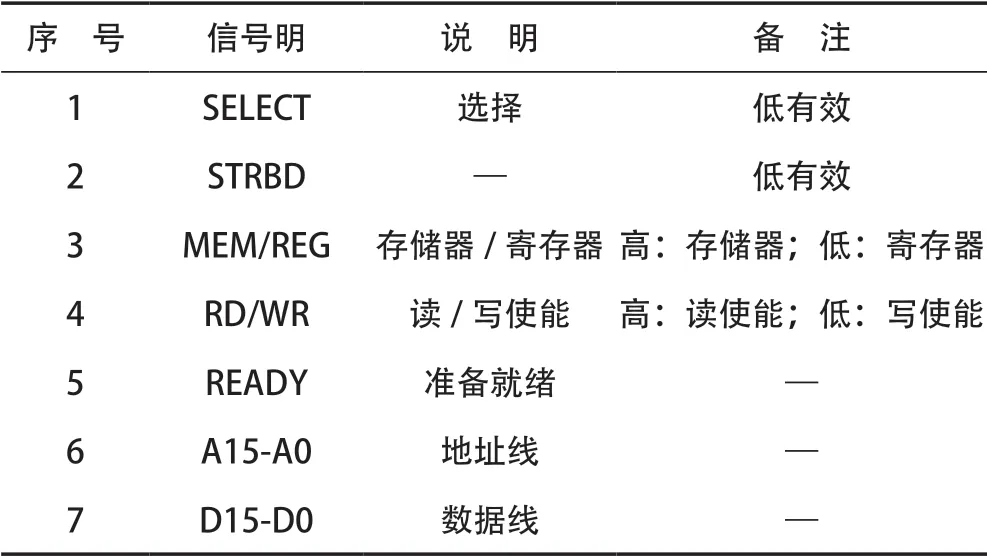

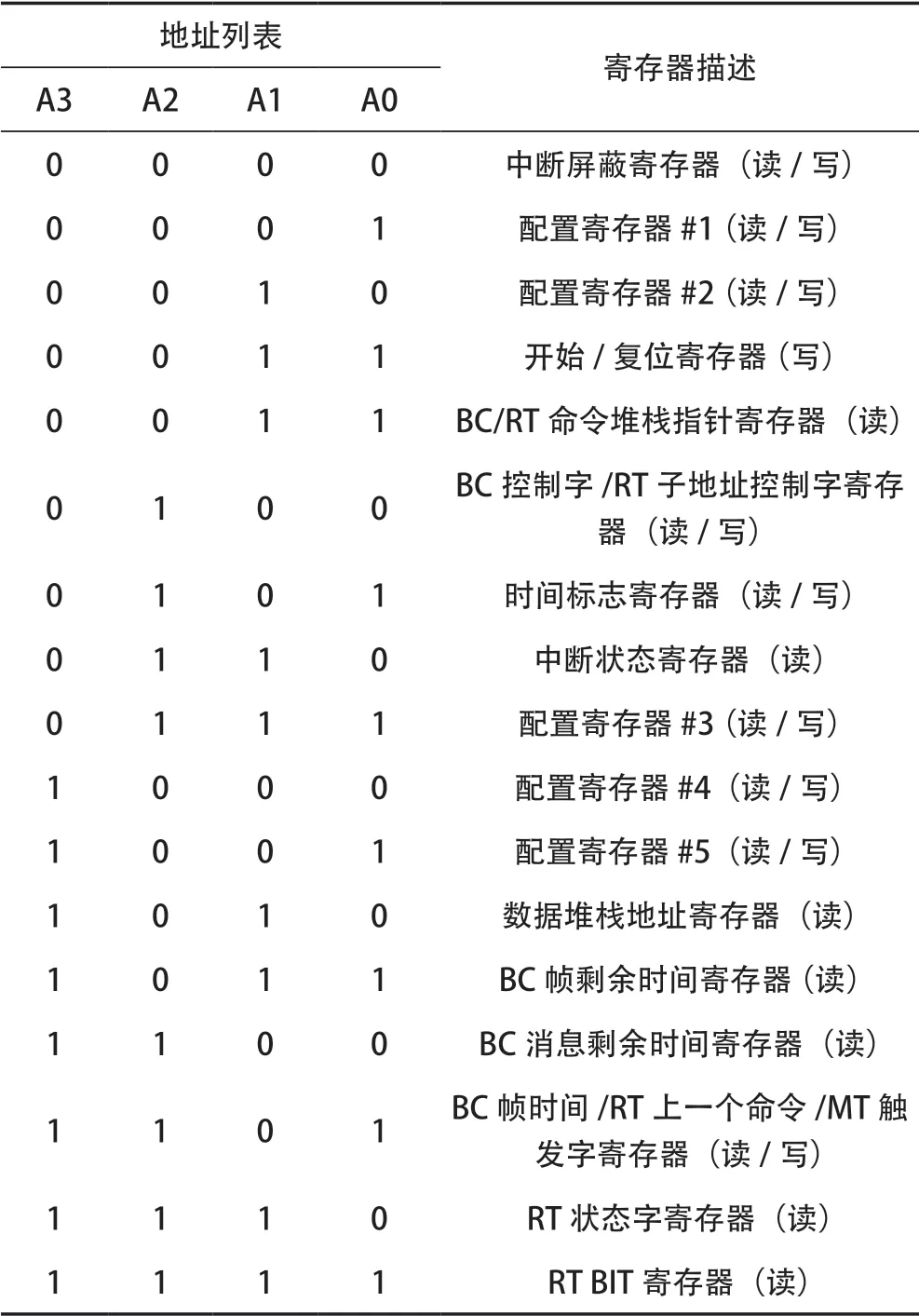

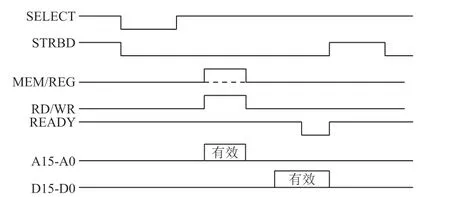

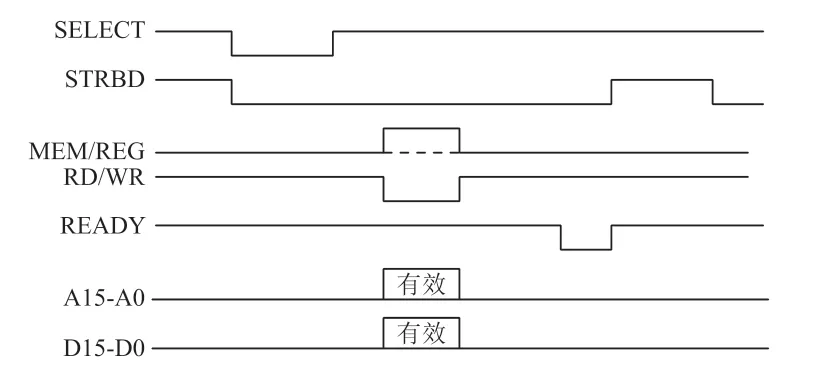

HT-61843GB 是国微电子的一款传输速率为4 Mb/s 的1553B 总线通信控制器,可实现1553B 总线数据传输方向控制、远程终端节点间的数据传输,以及总线数据监控,主要应用于航天航空、导弹等领域[8]。HT-61843GB 的读写时序如图1、图2所示。信号说明见表1所列。HT-61843GB 内部寄存器见表2所列。

表1 信号说明

表2 内部寄存器

图1 读时序

图2 写时序

1.3 软件设计

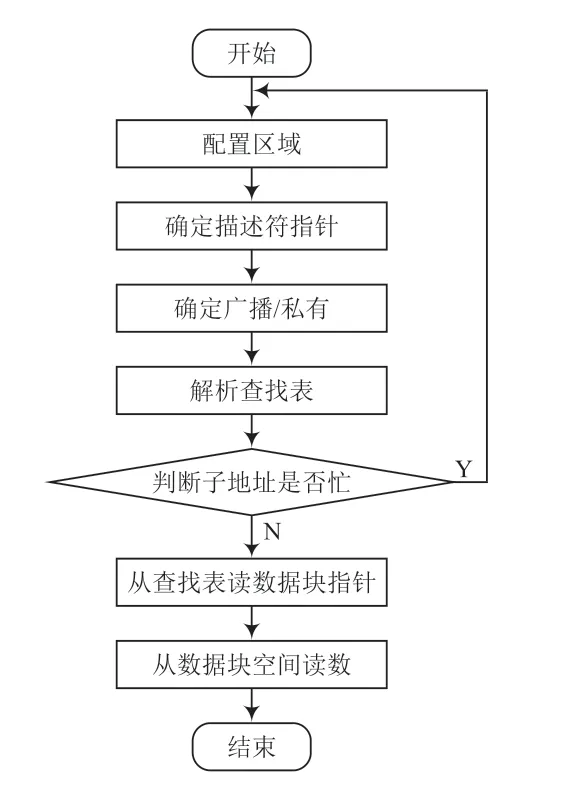

PL 部分软件实现采用Verilog 语言编写[9-10]。RT 协议处理消息的基本流程如图3所示。

图3 RT 协议处理消息的基本流程

2 实验验证

实验验证在Vivado 开发环境上实现[11-12],分为读写寄存器、读写内部存储器、接收BC 发送的数据三部分。上电后,复位端口(mstclr_1553b_temp)输出低电平,10 ms 后输出高电平,复位HT-61843GB 芯片。ssflag_1553b 输出高电平,极性选择端口polarity_sel_1553b 输出高电平,rtad_1553b输出“11010”,rtap_1553b 输出低电平,配置本地模块地址为26。

2.1 写寄存器

FMQL 写HT-61843GB 寄存器时序如图4所示。图中寄存器存储器选择信号(mem_reg_1553b_temp)输出低电平,读写选择信号(re_wr_1553b_temp)输出低电平,配置为写寄存器模式,片选信号(select_strbd_1553b_temp)输出低电平,地址线(address_1553b_temp)输出十六进制3、7、0、2 等地址;数据线(data_1553b_temp)输出十六进制1、8000、6294、b87b 等数据;数据有效信号(data_1553b_select)输出高电平。在数据写完成信号(ready_1553b)电平上升沿时刻,片选信号(select_strbd_1553b_temp)输出高电平,数据有效信号(data_1553b_select)输出低电平。

图4 写寄存器

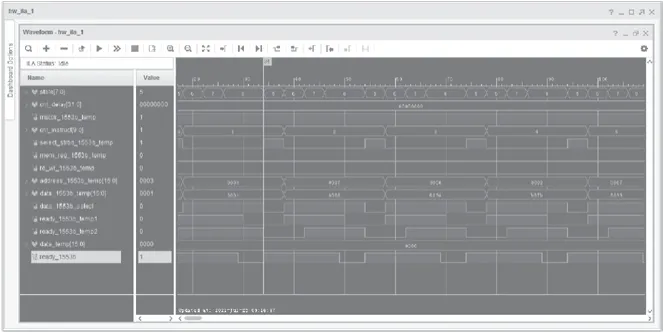

2.2 读寄存器

FMQL 读HT-61843GB 寄存器时序如图5所示。图中寄存器存储器选择信号(mem_reg_1553b_temp)输出低电平,读写选择信号(re_wr_1553b_temp)输出高电平,配置为读寄存器模式,片选信号(select_strbd_1553b_temp)输出低电平,地址线(address_1553b_temp)输出十六进制3、7、0、2、7 等地址;在数据读完成信号(ready_1553b)上升沿时刻将HT-61843GB芯片数据线上数据锁存入data_temp,片选信号(select_strbd_1553b_temp)输出高电平,从图中观察读出数据为十六进制8099、6294、b87b,数据正确。

图5 读寄存器

2.3 写存储器

FMQL 写HT-61843GB 存储器时序如图6所示。图中寄存器存储器选择信号(mem_reg_1553b_temp)输出高电平,读写选择信号(re_wr_1553b_temp)输出低电平,配置为写存储器模式,片选信号(select_strbd_1553b_temp)输出低电平,地址线(address_1553b_temp)输出十六进制140、141、142、143 等地址;数据线(data_1553b_temp)输出十六进制400、420、440、460 等数据;数据有效信号(data_1553b_select)输出高电平。在数据写完成信号(ready_1553b)电平上升沿时刻,片选信号(select_strbd_1553b_temp)输出高电平,数据有效信号(data_1553b_select)输出低电平。

图6 写存储器

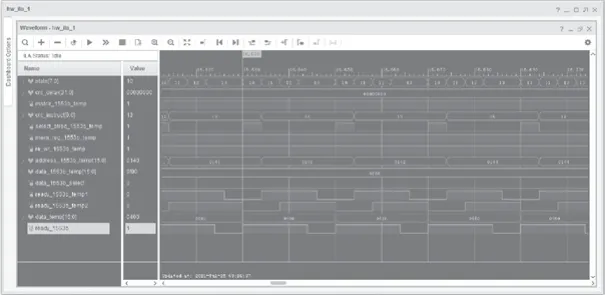

2.4 读存储器

FMQL 读HT-61843GB 存储器时序如图7所示。图中寄存器存储器选择信号(mem_reg_1553b_temp)输出高电平,读写选择信号(re_wr_1553b_temp)输出高电平,配置为读存储器模式,片选信号(select_strbd_1553b_temp)输出低电平,地址线(address_1553b_temp)输出十六进制140、141、142、143、144 等地址;在数据读完成信号(ready_1553b)上升沿时刻将HT-61843GB 芯片数据线上数据锁存入data_temp,片选信号(select_strbd_1553b_temp)输出高电平,从图中观察读出数据为十六进制400、420、440、460,读出数据正确。

图7 读存储器

2.5 接收BC 数据

初始化配置完成后等待中断,准备接收BC 数据。中断信号(int_1553b)输入高电平后,读命令堆栈寄存器、中断状态寄存器、消息命令存储器、消息数据块地址、消息时间、消息块状态、拆解子地址、数据长度。如果为发送数据指令,则完成发送数据;如果为接收数据指令,则根据子地址读取接收数据查找表指针,根据数据查找表指针读取数据。本文需要接收BC 数据,接收BC 数据时序如图8所示。图中寄存器存储器选择信号(mem_reg_1553b_temp)输出低电平,读写选择信号(re_wr_1553b_temp)输出高电平,配置为读寄存器模式,片选信号(select_strbd_1553b_temp)输出低电平,地址线(address_1553b_temp)输出十六进制6、3 地址;在数据读完成信号(ready_1553b)上升沿时刻将HT-61843GB芯片输出数据线上数据锁存入rtcommandstackpointer,值为十六进制8041、0054,片选信号(select_strbd_1553b_temp)输出高电平。同理读取消息命令存储器(message_command)54、消息数据块地址存储器(message_datablockaddr)55、消息时标存储器(message_timetag)56、消息块状态存储器(message_blockstatus)57,其值为十六进制d020、0600、905b、800,从中解析出命令信息(message_command[10])为0,判断为接收命令,子地址(subaddress)为1,长度(message_command[4:0])为0,因为用5 位数据只能表示0~31,因此用0 代表32个数据,读存储器141,输出接收查找表(receivelookuppointer)值为十六进制600,从存储器地址600~620 中读取接收数据(data_temp)为0~31,读出数据与发送数据一致,数据接收正确。

图8 接收数据

3 结 语

本文采用国产化FMQL、HT-61843GB 芯片,通过Verilog 编程,实现了1553B 总线RT 端关键器件国产芯片化,提高了1553B 总线RT 端模块国产芯片率,降低了对进口芯片的依赖,对促进国产芯片[13-14]的推广应用具有一定意义。