基于PCIe+X86系统的毫米波信号实时处理研究及FPGA实现

2023-06-02梁辉周建烨袁行猛

梁辉 周建烨 袁行猛

关键词:5G NR;毫米波;PCIe;FPGA;X86

0 引言

随着移动通信的迅猛发展及5G NR 技术的成熟,低频频谱资源的开发已经非常成熟,剩余的低频频谱资源已经不能满足5G 时代10 Gbit/s 的峰值速率要求,因此未来5G 系统需要在毫米波频段上寻找可用的频谱资源。随着全球移动通信技术向着网络化和宽带化趋势发展,5G 商用的基站和手机也已近开始部署与批量生产。现在仪表除了能够分析6 GHz 以下频率的信号以外,还需要分析微波、毫米波等波形。毫米波传输的技术难点主要在于5G 极高速的传输速率导致信号宽带和基带信号处理速度都将大大增加,对极高速数据流的实时处理和解析使得测试变得更加困难,作为测试技术的先行者,测试仪表5G功能毫米波测试技术开发也已提上日程[1]。

目前的高速数据传输系统中数据之所以可以高速、稳定的进行传输,总线技术在其中起到了很大的作用。早期的总线是以PCI 总线为代表的并行总线,并行总线因其并行结构的缺陷,导致传输速率无法进一步提高。PCIe 总线作为其中代表,在带宽、性能、时延、功耗、可靠性等方面有着卓越的表现,为高速数据传输系统提供了坚实可靠的技术支持。

赛灵思公司为其FPGA 提供了PCIe IP 核,提供了多种用户接口,可以大大降低设计成本,缩短整个项目的研发周期。随着人们近年来对5G 移动通信和人工智能等领域的深入研究,越来越多的科研人员基于FPGA高性能运算平台进行课题研究,但是运算过程中出现的海量数据传输问题成为需要克服的问题,所以对基于FPGA 的PCIe 高速数据传输系统进行研究有着重要的研究价值。

基带接收处理模块是满足多通道接收、不同系统带宽、不同子载波间隔、多用户基带接收的指标要求,完成参数灵活可配单用户、多用户基带信号接收功能,满足5G 终端的低延时、高效率、高质量的处理能力。FPGA 是现阶段实现采用的主流方式,具有较强的处理数字能力,设计采用Xilinx 公司的FPGA 芯片作为主要的实现平台。为了实现基带数据成功采集后的实时分析,采用PCIe 将FPGA 数据传输给上位机进行处理,突破高速信号不易实时分析的难题。

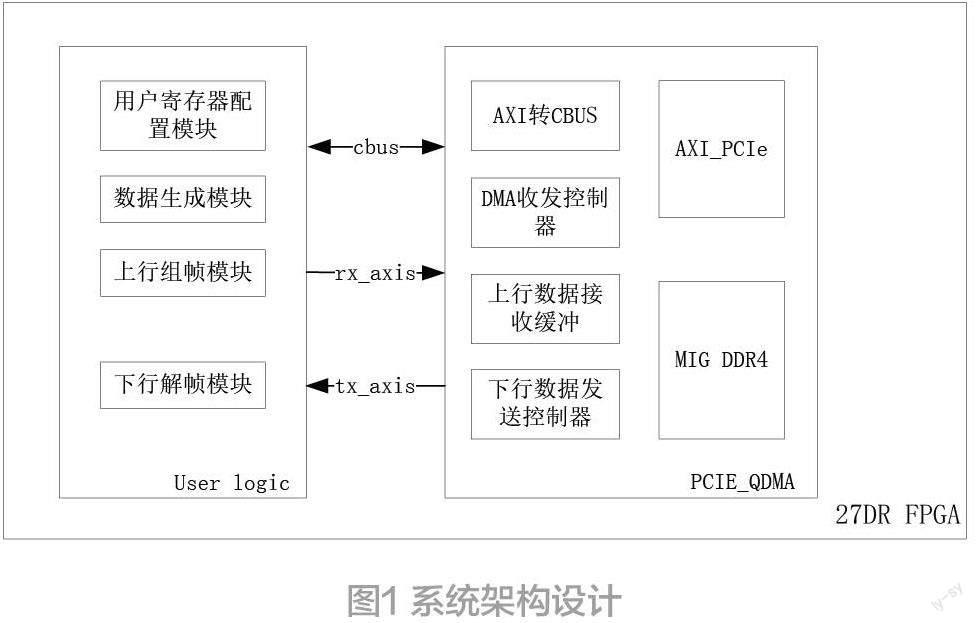

1 系统架构

为了满足5G 信号采集传输控制系统中对前端射频芯片的控制以及5G 数据到上位机的高速传输的需求。本设计实现了一套基于FPGA 的高速采集系统。该系统可允许用户通过PCIe 总线访问FPGA 中的用户配置寄存器,同时该系统可对前端射频产生的不高于4 GB/s(若使用多通道,则全部通道的累加带宽不高于4 GB/s)的连续或非连续上行数据进行实时采集,同时可以将上位机中的下行数据以不低于4 GB/s 的速率写入FPGA 侧的DDR4,并通过控制相应的发送寄存器将DDR4 中的数据以循环或单次的形式发送给射频端。

系统设计主要分为两部分:用户侧逻辑和PCIe_DMA 传输侧逻辑。

1.1 用户侧逻辑

1)模拟数据产生模块。用户可通过配置寄存器来产生4 种带宽模式的模拟数据。

2)用户寄存器配置模块。用户可通过cbus 接口读写用户寄存器。通过用户寄存器配置各类参数。

3)上行组帧模块。根据用户配置的四种模式,对模拟数据产生模块生成的数据添加相对应的32 字节帧头和32 字节帧尾。

4)下行解帧模块。该部分由用户自己实现,对DMA 收发控制器发出的下行数据进行解帧。

1.2 PCIe_DMA传输侧逻辑

1)AXI 转CBUS 模块。该模块实现用户通过PCIe总线的AXI 接口访问用户端的CBUS 接口。

2)DMA 收发控制模块。该模块提供1 路AXIS 接收接口,供用户接入上行数据;提供1 路AXI 接口供用户读写寄存器;提供1 路AXI 接口,供用户将下行数据写入DDR4。提供1 路传统中断。

3)上行数据接收缓冲模块。该模块实现1 个数据虚通道,使上行数据通过DDR4 缓存后再发送给DMA收发控制模块。

4)下行数据发送控制器模块。该模块实现用户通过配置寄存器完成DDR4 中任意地址任意长度的下行數据循环发送和单次发送。

5)AXI PCIE 桥模块。该模块使用XILINX 官方IP核实现,用户可通过AXI 接口实现对上位机的内存读写访问。

6)MIG DDR4 模块。该模块实现上行数据和下行数据的DDR4 缓存。

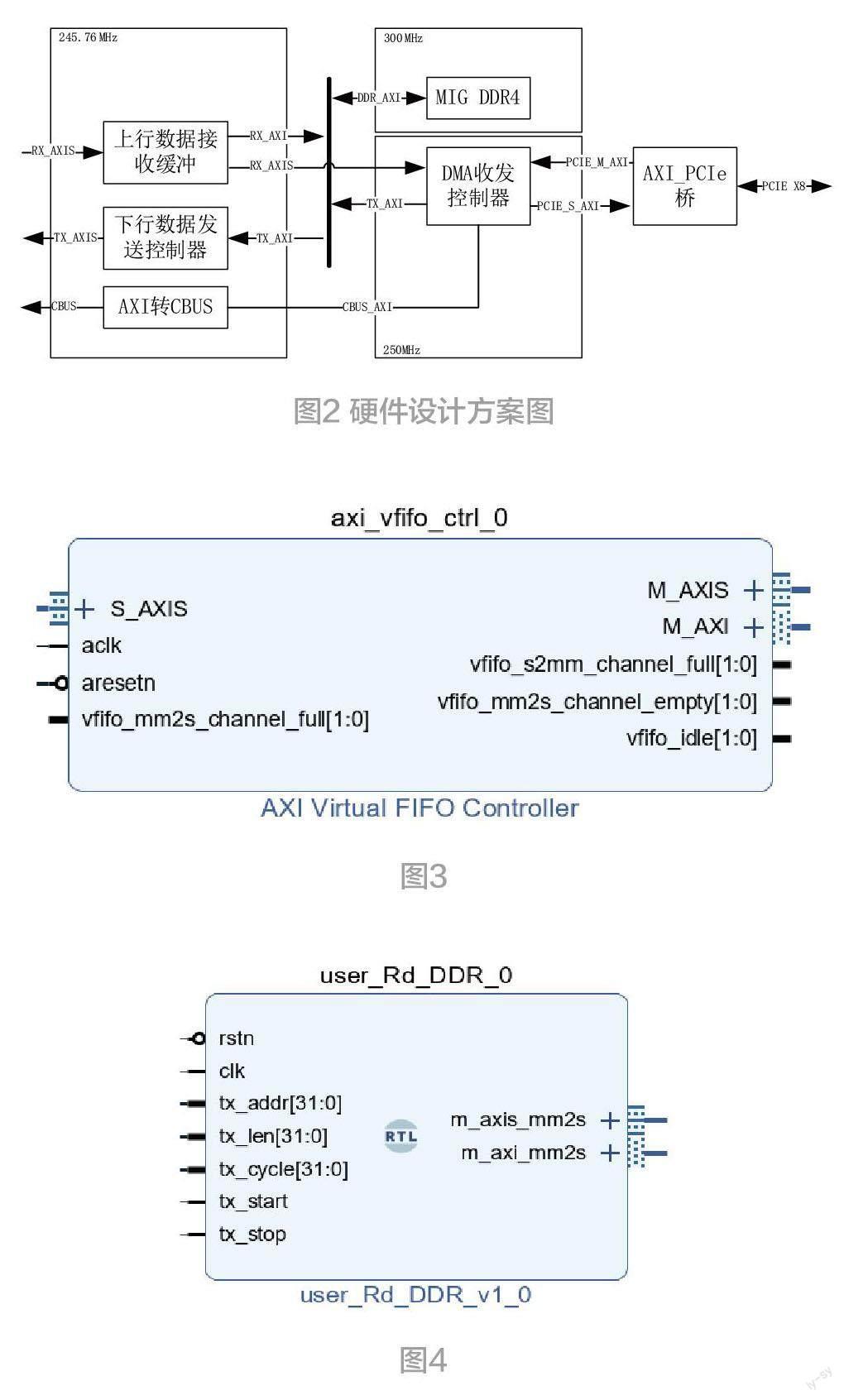

2 FPGA详细设计方案

PCIe 数据采集DMA 控制器模块(PCIE_DMA) 是该采集系统的核心模块,图2 为该模块的逻辑设计框图。上行数据流向描述如下:上位机用户通过AXI_PCIE 桥的PCIE_M_AXI 接口读写用户寄存器,控制上行模拟数据的产生;上行模拟数据通过RX_AXIS 接口写入上行数据接收缓冲,经过FPGA 板载DDR4 做缓冲后通过RX_AXIS 接口写入DMA 收发控制器;DMA收发控制器模块将收到的数据通过PCIE_S_AXI 接口写入上位机内存。下行数据流向描述如下:上位机用户通过AXI_PCIE 桥的PCIE_M_AXI 接口读写DMA收发控制器中的发送配置寄存器;DMA 收发控制器通过PCIE_S_AXI 接口从上位机获取下行数据并通过TX_AXI 接口写入FPGA 板载DDR4;上位机用户通过AXI_PCIE 桥的PCIE_M_AXI 接口读写用户侧的发送地址、发送长度、发送周期等寄存器;下行数据发送控制器根据用户侧的发送地址、发送长度、发送周期等寄存器从板载DDR4 中读取数据并通过TX_AXIS 接口发送到次级模块。

3 数据传输设计

3.1 上行数据缓冲模块

3.1.1 输入输出接口

该模块为上行数据缓冲模块。该模块利用vfifo 控制器实现,vfifo 控制器本质是两个DMA。第1 个DMA 将S_AXIS 收到的上行数据转换成M_AXI 接口写入DDR4做缓存,第2 个DMA 通过M_AXI 接口将数据从DDR4中读出来并转换成M_AXIS 接口送入次级处理模块。该模块主要为了实现瞬时带宽较高的情况下,上行数据的缓存。

3.2 下行数据发送控制器

3.2.1 输入输出接口

该模块是下行数据发送控制器模块,此模块可帮助用户通过tx_addr、tx_len、tx_cycle、tx_start、tx_stop来实现从DDR4 中读取任意长度的数据并以单次或者多次或者循环发送的方式发送到次级模块。具体接口定义如下。

tx_addr :發送地址。

tx_len:发送长度。

tx_cycle:循环发送次数,0 为循环发送,1-n 为固定次数发送。

tx_start:发送开始。

tx_stop:循环发送停止。

m_axi_mm2s:通过AXI 接口从DDR4 中读取数据。

m_axis_mm2s:通过AXIS 接口将下行数据发送给用户。

3.3 AXI转CBUS

该模块为AXI 转CBUS 模块。该模块实现将来自PCIE IP 核的M_AXI 接口转换成用户读写寄存器CBUS接口。接口定义及时序如下。

cbus_addr: 寄存器地址。

cbus_wr: 寄存器写使能。

cbus_rd: 寄存器读使能。

cbus_din: 寄存器写数据。

cbus_dout: 寄存器读返回数据。

该模块为DMA 收发控制器模块。该模块实现上下行数据的DMA 传输。用户上行数据通过adc_axis 接口写入,通过PCIE_M_AXI 接口写入AXI PCIE 桥。用户下行的数据通过PCIE_M_AXI 接口从AXI PCIE 桥读返回后,通过DDR_M_AXI 接口写入FPGA 板载DDR4。PCIE_S_AXI 接口用于上位机通过AXI PCIE 桥来访问DMA 收发控制器中的各个配置寄存器。cbus_axi 接口用于上位机通过AXI PCIE 桥来访问用户侧的自定义寄存器。axi_aclk为AXI PCIE 桥产生的250 MHz 时钟。Intx_msi_request为DMA 收发中断。RcvEn 为上位机发出接收使能信号。Rxready 为DMA 接收控制器准备好信号。

3.5 AXI PCIE桥模块

该模块为AXI PCIE 桥模块。此模块为XILINX 提供的IP 核,具体设置以及接口说明可参考官方手册pg195 DMA/Bridge Subsystem for PCI Express v4.1。本设计中M_AXI_B 接口用于上位机读写DMA 收发控制器中的配置寄存器或者用户侧自定义的寄存器。S_AXI_B 接口用于DMA 收发控制器访问上位机内存地址空间。S_AXI_LITE 接口用于动态配置AXI PCIE桥模块,本设计不实际使用。Usr_irq_req 为DMA 收发控制器产生的中断请求。PCIE_MGT 为8x Gen3 的PCIe 收发串行链路。s_axi_aclk 和s_axi_aresetn 为PCIe 输出时钟(250 M)和复位信号( 低有效)。其余输入输出接口本设计不实际使用。

3.6 MIG模块

该模块为MIG 模块,此模块为XILINX 提供的IP 核,具体设置以及接口说明可参考官方手册pg150 LogiCOREIP UltraScale Architecture-Based FPGAs Memory InterfaceSolutions v4.2。本设计中采用64 位DDR 数据位宽,时钟1 200M。AXI 数据位宽512 位,输入参考时钟300M。

4 仿真与测试

采用Vivado2020.2 软件进行本次开发设计工作,开发的FPGA 型号为XCZU27DR-ff vg1517-2-i,本次设计通过基带板以及整个采集平台,验证本次试验的可行性。

测试结果运行测试程序,启动上行测试,上行测试结果如下图所示,上行速率测试6 276 Mbyte/s,下行测试结果如下图所示,下行速率测试6 620 Mbyte/s, 满足数据实时传输要求。

5 结束语

本研究完成了毫米波基带数据的实时传输,本设计主要研究开发了,经过仿真和硬件验证了传输的正确性,确认了本研究的可行性。