基于软件无线电的弹载一体化通信终端

2023-04-29李世博

李世博

摘要:针对当前常规弹载通信系统集成度低、配置繁琐等问题,提出一种基于软件无线电的弹载一体化通信终端。该终端采用一体化设计思路将电源转换、接口采集、信号处理、载波调制和功率处理单元高度集成在同一块电路板上,基于软件无线电思想实现通信方式、射频参数的实时在线配置。该终端经试验验证,性能可靠,操作便捷,优化了现有弹载通信产品。

关键词:软件无线电;一体化;弹载通信

一、前言

软件无线电思想是20世纪90年代以后逐渐兴起的一种全新设计思想,其核心是在通用通信硬件平台上加载不同的通信软件,以实现不同通信方式间的转换。软件无线电平台良好的兼容性和可编程性使得通信系统的开发演化为数字信号处理软件的研究,这将极大缩短通信系统开发周期并有效降低研制成本。

现有弹载通信产品基于模拟技术设计,产品功能往往需要依据不同任务需求进行定制化设计。一款弹载通信产品仅供某一特定任务系统使用,功能要求稍有变化就需要重新进行电路、结构和软件设计[1]。针对这一问题,本文提出一种稳定性、灵活性更高的基于软件无线电的弹载一体化通信终端。

二、系统总体设计

(一)设计要求

基于软件无线电的弹载一体化通信终端的主要技术要求:

无线电频段为S波段,采用PCM/FSK调制模式[2];

供电范围+18V~+32V;

三次以上谐波抑制:≥80dBc;

带外杂波抑制:≥60dBc。

(二)系统原理

通信终端的工作流程主要包括接口采集、信号处理、载波调制、功率放大和发射天线单元。其中,接口采集和信号处理单元实现模拟信号的调理和转换、数字信息的接收和缓存、图像信息的提取和压缩,按预定的帧格式对信息进行编码,再经过信道编码后形成具有纠错能力的PCM信号,载波调制单元将PCM信号以一定的频偏调制到载波并输出,功率处理单元将已调载波信号滤波并放大至一定功率,发射天线单元实现射频功率信号近似全向辐射的功能。

三、设计方案

(一)主要元器件选型

数字处理电路主要由FPGA、NOR FLASH、SPI EEPROM、射频收发芯片、AD转换器、RS422接口、LVDS接口、接口缓冲器、电源等器件组成。其中FPGA选取Xilinx公司的XC7A100T-2CSG324I作为核心处理器件,主要完成所有通信信息的接收缓存,按预定的通信帧格式对信息进行编码,再经过信道编码后形成具有纠错能力的PCM基带信号传输给载波调制。对信号采集控制功能实现所占用资源、芯片尺寸等进行综合评估,选用Xilinx公司Artix-7系列的XC7A100T-FGG484I工业级FPGA芯片。该芯片尺寸为23mm×23mm,封装为FGG484,最大可用I/O为285个,逻辑单元101440个,内部RAM为4860Kb,同时采用1.0V内核电压,能够较好地降低系统功耗,接口电平可选择使用1.0V、1.8V、3.3V等多种标准。FPGA的配置芯片选用Micron公司的MT25QL256ABA8ESF-0SIT。

射频收发器采用ADI公司的AD9361,AD9361是一款高集成的解决方案,内部集成了模拟滤波、混频器、数据转换器、发射和接收通道的频率合成器以及可编程增益、直流偏置校准等数字域的其他功能[3]。这款器件通过正交误差校准和直流偏置校准的功能,很好地解决了此前零中频架构的直流偏置和正交误差限制,从而使零中频架构成功应用于软件无线电的芯片产品。AD9361集成2个发射和两个接收通道,频率范围70MHz~6GHz,通道带宽200kHz~56MHz,1GHz条件下噪声系数为2dB,在更高的频率如2GHz时,可做到小于3dB;AD9361因为集成有ADI自有的12位连续时间的∑-ΔADC,采样率达640MHz,大大降低了对模数转换器前端的模拟滤波器的要求,因此可以实现滤波器的集成,无需外置滤波器,可有效降低系统成本。

(二)电源转换单元设计

通信终端的外部输入电压为18V~32V之间的直流电源,需要变换为终端内部的各种电压。FPGA的内核电压、IO电压和辅助电压,RS422接口、LVDS接口、Flash芯片的电压,AD9361的电压,功放电路的电压等,需求的电源种类丰富,对电源的设计要求较高。

(三)接口采集和信号处理单元设计

接口采集和信号处理单元以FPGA为中心,外围专用接口芯片、光耦隔离电路和信号调理转换电路等构成。FPGA模拟信号、开关信号、RS422和LVDS总线信号成组装订后进行PCM编码,然后将编码信息进行FSK调制生成IQ数据流,FPGA将IQ数据流发送给射频收发芯片AD9361。AD9361完成信号的数模转换及正交上变频,输出射频信号。

模拟信号经过调理电路以后,送入交换子,按照固定的帧格式选通后进入A/D转换器量化,转换为数字量后进入FPGA完成采集。调理电路选用运放AD824AR,其压摆率为2V/μs,带宽为2MHz,外围连接调节电阻和滤波电容。交换子选用的是ADG426,ADG426是CMOS型十六选一多路模拟开关。A/D转换器选用AD公司的AD9240AS,其转换速率最高可达10Msps,转换速率由时钟CLK决定。由FPGA输出的A/D转换器的时钟CLK_AD电平为3.3V,通过AD8042运算放大器,实现电平转换为+5V,接入AD9240AS中,以满足其时钟输入幅度的要求。

LVDS信号分为CLK和DATA两路,分别用于同步时钟和同步数据的传输。DS90LV048ATMTC为四通道接收LVDS接口芯片,可用于本方案的LVDS接收电路,最高时钟速率为200MHz。

本设计选用MAX3491芯片用于发射机的功能配置和调试串口,该芯片是一款低功耗收发器,用于RS-422和RS-485等串行数据接口标准系统中,内部有驱动、接收和使能控制模块,可实现全双工传输,最大传输速率为12Mbps。对外接口增加了ESD保护电路和接口悬空保护电路,进一步提高了电路的静电防护能力。

本设计选用HCPL-0631/HCPL-063L作为开关量输入电路,适配+3.3V或+5V的工作电压,可完成开关信号的采集处理。选用AT25M02用于频点存储,采用+3.3V的SPI总线接口,存储容量2Mbits。

本方案中FPGA是信号处理的核心,主要完成所有通信信息的接收缓存,按预定的通信帧格式对信息进行编码,再经过信道编码后形成具有纠错能力的PCM基带信号传输给载波调制。对信号采集控制功能实现所占用资源、芯片尺寸等进行综合评估,选用Xilinx公司Artix-7系列的XC7A100T-FGG484I工业级FPGA芯片。该芯片尺寸为23mm×23mm,封装为FGG484,最大可用I/O为285个,逻辑单元101440个,内部RAM为4860Kb,同时采用1.0V内核电压,能够较好地降低系统功耗,接口电平可选择使用1.0V、1.8V、3.3V等多种标准。FPGA的配置芯片选用Micron公司的MT25QL256ABA8ESF-0SIT。

本方案采用数字变频设计,射频链路采用射频收发器AD9361实现。AD9361内部集成了完整的发射链路,包括滤波器、放大器、衰减器、本振、上变频等电路。AD9361射频输出后进入后级发射链路。

1.功率处理单元设计

功率处理单元主要由驱动放大器、衰减器、功率放大器、隔离器、低通滤波器等多个功能部件组成。

根据射频链路中的各级衰减及放大器增益,计算可得产品输出功率为31.5dBm。另外,通过调整链路增益,使末级功放工作时处在深度饱和状态,降低高低温状态下功放输出功率的变化,保证产品在三温状态下输出功率均不小于31dBm。

功率放大器采用国产高增益GaAs功率管,输出能力33.5dBm,增益29dB,内部集成放大器偏置电路,采用标准化管壳封装。功率放大器设计效率为46.7%。

采用管壳封装形式可以实现功放芯片使用过程中的气密性设计,而且提高了功放的空间隔离,有效地减小了与其他射频器件间的空间串扰;另外,与裸芯片的烧结加金丝键合的微组装方式相比,装配过程中管壳封装的螺钉安装加焊接方式更方便快捷。采用标准的管壳进行封装可以更好地保证供货周期。

整个射频前端由+8V进行供电,内部集成线性稳压器和负电荷泵,用于生成+5V与-5V,给各个功能单元供电。同时射频前端集成时序保护电路,可以在-5V电压开路或欠压时及时关断功放漏极+8V供电,从而保护功放不被烧毁。

稳压电路常用的有两种形式:线性电源(LDO)和开关稳压电源(DCDC),线性电源(LDO)的输出电压纹波小,但是在输入电压和输出电压相差较大时转换效率较低,只能降压不能升压。开关稳压电源(DCDC)的纹波大,但是在输入电压和输出电压相差较大时转换效率较高,并能实现升压输出。

+5V和-5V被用于给放大器供电,电流几十毫安,功耗小;但是电压的稳定性会影响放大器的工作状态。综合考虑,采用LDO稳压方式可保证放大器供电的稳定性,进而提升了产品性能的稳定性。

通信终端需具有输出开路、短路保护功能,开路、短路5分钟不损坏电路的要求。功放输出端口开路、短路时,端口驻波严重恶化,饱和功率工作状态下反射信号回来倒灌管子的话,很容易引起自激而烧毁。考虑到此种情况,功率放大器后级联隔离器,选取的隔离器设计保证耐受功率大于36dBm,损耗小于0.5dB,可以满足隔离器在模块中能够正常工作。隔离器对放大器的保护作用很明显,因为微波放大管的输出匹配在有大功率反射回来的时候,很容易造成失配而烧毁;隔离器的材料是采用铁氧体隔离器又称单向器,它是一种单向传输电磁波的器件,当电磁波沿正向传输时,可将功率全部馈给负载天线,对来自负载的反射波则产生较大衰减,这种单向传输特性可以用于隔离负载天线变动对放大器的影响。

通信终端具有杂波抑制指标要求,在射频链路没有混频电路,因此不会引入带外杂散;在模数转换过程中,AD9361出口主信号间隔50Mhz处存在杂散干扰,由于与主信号间隔太小,很难通过射频滤波器滤除掉,只能通过数字电路进行调节,令带外杂散抑制大于60dBc,测试结果显示杂散抑制为63.4dBc,满足指标要求。

通信终端有谐波抑制要求,通常放大器在工作时,都会产生高次谐波。采用的驱动放大器的高次谐波功率与主信号相比,均小于-25dB,在驱动放大器和功率放大器之间级联一级对二次谐波及以上频率抑制度大于35dBc的滤波器,保证功放入口处的谐波抑制度不小于60dBc,消除驱放谐波对产品谐波抑制性能的影响。

通信终端中,功放的高次谐波为影响产品谐波抑制的主要因素,采用的功放高次谐波测试结果与主信号功率相比,二次谐波为-28.7dB,三次谐波为-54.0dB,四次谐波为-48.2dB,五次谐波为-60.1dB。

为满足谐波抑制指标,在功放后级联低通滤波器以抑制功放的高次谐波。由于单级滤波器的带外抑制度有限,不能保证对高次谐波的有效抑制,设计方案中采用两级滤波器级联的方式以调高抑制度,滤波器采用LC+传输线形式两级级联,并用金属罩封装,提高了器件的稳定性和抗干扰性

2.通信终端软件设计

通信终端采用FPGA软件完成输入信号采集、编码、调制及射频配置等功能,采用模块化设计思路,软件可靠性高。FPGA软件对模拟信号、开关信号、数字总线信号进行采集、信道编码(CRC和R-S信道纠错编码及随机化编码),形成串行数据流,经正交I/Q调制,形成调制信号,并根据EEPROM和外部命令完成射频配置[4]。

FPGA软件使用复位信号生成模块、使能信号生成模块、模拟信号处理模块、开关信号处理模块、RS422数据处理模块、LVDS数据处理模块、CRC编码模块、版本信息生成模块、通信帧格式编码模块、输出预编码模块等通用模块。

其中频点配置、启停控制等功能主要通过时序控制模块实现。该模块用于控制射频输出状态及AT命令的执行流程,该模块内部为一个状态机,每个状态完成相应的功能:

(1)系统复位后,首先完成对RF捷变器的配置;

(2)从EEPROM中读取当前的载波频率,根据载波频率计算RF捷变器中相应寄存器的频率控制字,并将频率控制字写入RF捷变器中相应寄存器;

(3)从EEPROM中读取当前的功率衰减值,并将功率衰减值写入RF捷变器中相应寄存器;

(4)设置AT命令接收使能,并等待外部输入的AT命令;

(5)读取AT命令状态寄存器,根据AT命令的类型、命令功能、命令参数值完成相应的功能。

四、试验结果

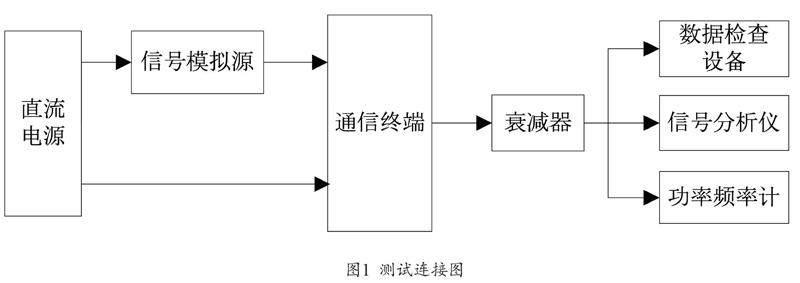

通信终端试验测试项目包括工作电流、射频和通信参数,测试连接图如图1所示。

测试连接图中,信号模拟源模拟各种被测参数送给通信组件,直流电源提供所需工作电压,功率频率计显示通信组件工作功率和频率,信号分析仪显示谐波抑制、杂波抑制和频偏,数据检查设备完成通信信号的接收解调和数据处理、输出显示[5]。

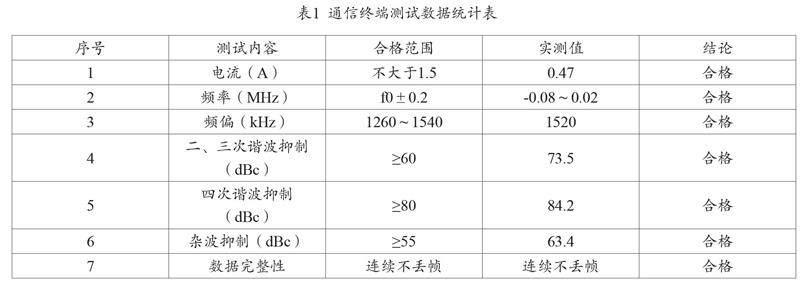

其中,滤波器性能的实测结果为低通滤波器对二次谐波抑制大于78dBc,对三次谐波抑制大于71dBc,对四次谐波大于80dBc。综合功放的性能和滤波器的性能可以满足设计要求的二次谐波抑制不小于60dBc,三次谐波抑制不小于60dBc,三次以上谐波抑制不小于80dBc。通信终端的完整测试数据统计结果如表1所示。

五、结语

基于软件无线电的弹载一体化通信终端采用一体化设计思路,将电源转换、接口采集、信号处理、载波调制和功率处理单元高度集成在同一块电路板上,基于软件无线电思想实现通信方式、射频参数的实时在线配置。同时采集多路模拟量和数字量,通过外部命令可配置无线通信和无线通信模式,工作模式灵活,具有成本低、低功耗、高集成度及良好通用性的特点,对于常规兵器弹载通信装置的小型化、集成化和通用化设计具有一定的指导价值。

参考文献

[1]杜向辉,于晓辉,郑立会.弹载数据链信道模型仿真研究[J].航空兵器,2013(6):27-29+64.

[2]吴志宏.遥测PCM信号源的设计与实现[D].太原:中北大学,2014.

[3]郭凯.航天遥测技术现状及发展思考[J].遥测遥控,2015,36(5):7-15.

[4]宋启成,张西韩.遥测技术的发展及应用探讨[J].科技咨询,2013(13):41+71.

[5]白静栋.基于软件无线电技术的遥测遥控通信系统的研究与实现[D].北京:北京邮电大学,2015.

作者单位:中国空空导弹研究院