应用于MEMS陀螺仪的SoC设计

2023-04-26刘昊哲杨拥军

刘昊哲,任 臣,王 晓,杨拥军

(中国电子科技集团 第13研究所,石家庄 050051)

0 引言

MEMS陀螺仪相对于传统陀螺仪具有体积小、智能化、功耗低、成本低以及可批量生产的优势,在汽车电子、消费电子和轨道交通等领域广泛应用[1]。随着MEMS陀螺仪设计的不断优化和完善,成为微型惯性系统的核心和导航系统进一步发展的关键器件,正逐步取代传统陀螺仪的地位。

MEMS陀螺仪的性能指标包括量程、零偏稳定性和速率精度等[2],其中零偏稳定性是对MEMS陀螺仪的精度起着重大影响,是MEMS陀螺仪性能优劣的重要评价标准。现有的MEMS陀螺仪产品一般为MEMS敏感结构、专用集成电路(ASIC,application specific integrated circuit)硬件逻辑处理电路、印刷电路板(PCB,printed circuit board)供电电路及通用微控制器模块组成的三级架构。PCB板上的微控制器模块负责对经过C/V、ADC和多级滤波器处理后的信号的补偿和存储[3],因此从ASIC芯片到PCB板的数据传输过程需要满足低延迟、低噪声、低抖动以及高速率的要求。当前主要采用的方式为串行外围设备接口(SPI,serial peripheral interface)协议的信号传输,对陀螺输出的角速度信号存在着一定的失真[4],且选择通用的微控制器对陀螺信号进行处理和存储难免存在微控制器数据处理能力和存储空间大小与实际需求不匹配,无法实现陀螺仪的最优性能或产生一定的资源浪费现象。

因此,为了解决MEMS陀螺仪集成度不高、制造步骤繁琐、产品体积偏大等问题,本文提出一种新的设计思路来解决这些问题。通过为MEMS陀螺仪设计专用的SoC,依据陀螺仪对微处理器数据处理能力、存储模块大小、数据传输速率和位数的需求对SoC的组成模块进行定制设计[5],在提升陀螺仪的性能的同时丰富陀螺仪的应用场景。本文基于ARM的Cortex-M3内核针对应用于MEMS陀螺仪的SoC进行了集成设计,通过软硬件协同设计的方式,将SoC芯片所需功能的实现方式划分为软件实现和硬件实现两部分[6],对MEMS陀螺仪数据实时带宽有限、体积较大、存在处理资源浪费等问题进行解决。

1 MEMS陀螺仪的智能化需求分析

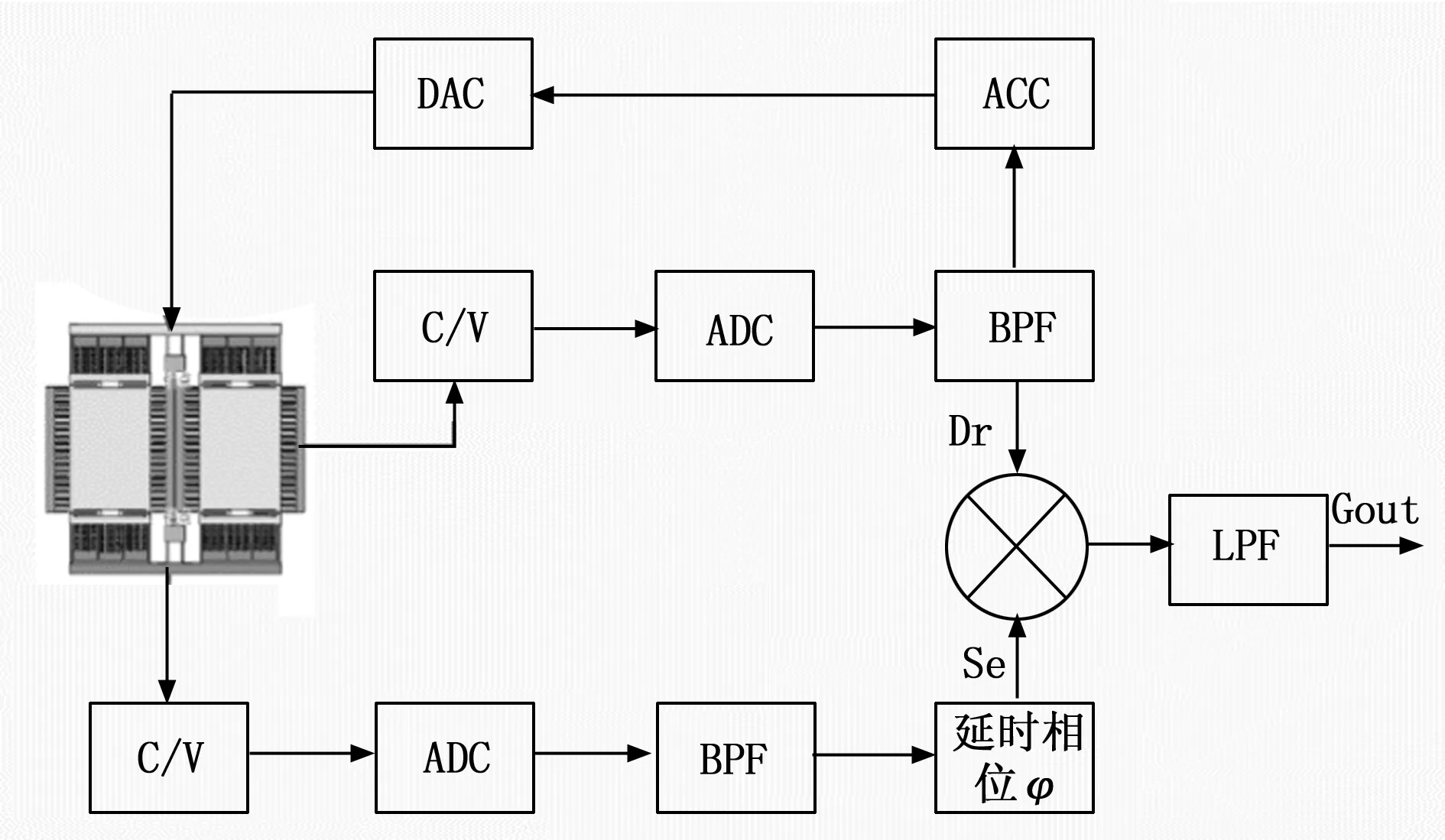

本文的研究对象为硅MEMS振动式陀螺,其敏感结构采用双质量框架,选用静电驱动、变间距电容检测工作方式,基于体硅SOI和圆片级真空封装工艺加工而成。MEMS陀螺仪的检测电路原理如图1所示,驱动环路采用四阶带通Sigma-Delta数字闭环结构、检测通路选用开环检测的工作方式[7]。

图1 MEMS陀螺仪基本工作原理

图1中,C/V单元将外界加速度导致的陀螺仪敏感单元所产生的差分电容的变化转换成模拟电压信号。ADC模块采用斩波(CS)技术和相关双采样(CDS)技术,有效抑制了低频噪声和中频段噪声,更高精度的完成模拟量到数字量的转换。BPF模块为带通滤波器,有效滤除干扰信号。AAC为自动增益控制模块,实现驱动振幅稳定控制。DAC模块完成对MEMS结构的驱动反馈,实现驱动闭环,使得MEMS结构保持谐振。检测通路为开环结构,由C/V、ADC、BPF和延时相位模块组成。φ为检测通路的延时相位,为检测信号,为驱动信号。LPF模块为低通滤波器,有效滤除干扰信号。经过对驱动信号和检测信号的相干解调并经过低通滤波后得到陀螺仪角速度输出信号。

由于MEMS陀螺芯片的主要制作材料单晶硅对温度较为敏感,其机械和物理参数如杨氏模量和应力受温度影响较大,进而对陀螺的谐振频率和系统刚度产生影响,导致陀螺产生输出温度漂移。另一方面,MEMS陀螺生产过程中经过了刻蚀和高温键合等工艺,在结构中不可避免的产生了残余应力;MEMS陀螺封装过程中,由于陶瓷管壳、粘结胶和MEMS芯片之间的热膨胀系数的不一致,同样会产生应力,导致陀螺温度漂移的出现[8]。综上可知MEMS陀螺仪不可以避免的会出现温度漂移,传统的解决方案为在PCB板级供电电路上连接一个通用的微控制器对陀螺温漂进行补偿,同时将陀螺仪输出数据进行存储并打包发送到上位机,产品整体尺寸达到22 mm×20 mm,如图2所示。

图2 组合通用单片机的陀螺仪

然而,在PCB上进行MEMS陀螺仪数据处理需要使用SPI通信协议将ASIC上的数据传输到片外微控制器,这一过程需要在不断采集新的数据的同时将数据进行串行传输具有一定的风险且向上位机传输需要再次进行串行同步传输,影响陀螺稳定性的同时限制了数据处理速率,直接影响MEMS陀螺仪的性能。因此本文提出设计MEMS陀螺仪专用SoC芯片推动MEMS陀螺仪的集成化和智能化,来解决传统ASIC和单片机组合方式存在的固有问题,实现MEMS陀螺仪的智能高精度控制。

2 SoC电路设计

2.1 SoC总体架构

本文对应用于MEMS陀螺仪的SoC进行了设计,其中硬件电路部分的设计优势在于对特定功能实现速度快,可以达到十倍、百倍的速度提升;降低了对处理器复杂度的要求,简化系统设计;减少相应的软件程序设计时间[9]。SoC设计过程考虑到MEMS陀螺仪使用过程中低功耗和高速处理复杂任务的需求,选择Cortex-M3内核作为核心处理单元[10],SoC运行过程中需要实现对数据采集模块所采集数据进行打包、存储并设计软件算法进行补偿、滤波,以提高MEMS陀螺仪的数据精度,因此使用高级微控制器总线结构(AMBA,advanced microcontroller bus architecture)进行SoC的架构设计[11]。不同于通用的微控制器,集成设计的SoC中的微控制器模块结构选用由设计需求决定,例如本设计中考虑到其主要服务于内部模块信息的处理,因此未添加通用输入输出接口模块(GPIO,general-purpose input/output),节约了芯片的面积,使得芯片结构更为合理。SoC整体架构如图3所示,SoC系统主要由Cortex-M3微处理器、SRAM、ROM、数据采集模块、系统时钟模块以及外围通信接口组成。

图3 SoC整体架构

为了解决传统装配方式对MEMS陀螺仪ASIC输出处理不够及时的问题,本文提出了将数据采集模块直接作为高性能总线(AHB,advanced high-performance bus)的从机进行集成设计的SoC总线架构,通过微电容检测和模数转换器的组合设计,将外界惯性信息转换为数字形式的电信号后,经过AHB总线通信输入微处理器内核进行数字信号处理和存储操作。不同于传统的SPI串行数据传输模式,本设计中数据采集模块直接通过AHB总线接口进行32位并行数据传输的模式在减小数据丢包风险的同时有效提高了数据传输效率。

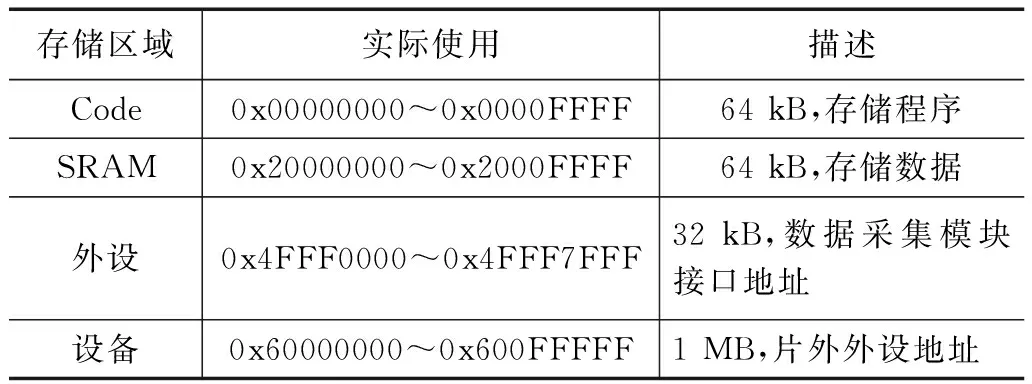

在SoC的设计中,需要对数据采集模块、数据存储单元、外围通信接口等外设进行寻址访问,外围设备所上传的数据也需要暂时存放在指定的存储单元中,所设计的软件程序同样需要在Cortex-M3内核的寻址空间中搭载存储单元进行存储[12]。根据ARM对Cortex-M3内核应用程序、数据存储、片上外设、片外外设以及供应商定义等地址使用类型的粗略划分,本设计在Cortex-M3处理器的4 GB寻址空间中实际使用的存储空间地址设计如表1所示。

表1 SoC部分寻址空间使用情况

为了实现数据采集模块的高速数据传输、微处理器对数据采集模块的基本控制以及SoC系统与上位机的数据通信等要求,本研究通过IP复用技术对系统总线、存储单元、数据采集模块、外围通信接口等模块进行了设计,通过单个SoC芯片的设计替代了原有ASIC芯片和单片机的组合。本SoC系统相比于传统的MEMS陀螺仪板级数据处理模式明显的减少了组件数目、大幅度地缩减了数据处理单元所占用的板级空间,在满足陀螺仪输出信号的补偿、存储和通信需求的同时大大提升了系统的集成度。

2.2 数据采集模块专用接口设计

数据采集模块的主要由微电容检测模块和模数转换器模块组成,是MEMS智能传感器采集外界信息的关键模块。本设计选择通过MEMS敏感结构将外界的变化转变为微电容形式的电信号[13],是由于电容式传感器在应对复杂的温度、湿度以及磁场环境的不敏感性可以提高陀螺仪的基础测量精度,降低环境因素的干扰。微电容检测模块对检测电容的大小进行测量,将其转换为等效的电压信号,模数转换器模块对模拟形式的电压信号进行采样、量化后转换为数字信号[14],数据采集模块良好的温度特性和BCD工艺兼容性可以很好地与后续数字信号处理部分的电路兼容,符合SoC设计整体要求。

在SoC系统中,数据采集模块作为自定义外设,其设计过程首先需要在Cortex-M3内核的寻址空间中定义外设地址,本设计在Cortex-M3处理器用于片上外设的512 MB寻址空间中将0x4FFF0000~0x4FFF7FFF区域内32 kB的地址空间设置为数据采集模块外设寄存器的地址映射区域。为了实现微处理器主机对AHB总线从机的控制,需要微处理器通过地址译码器对自定义外设寻址空间生成总线选择信号,根据具体地址对该地址上的外设寄存器进行读写操作,进而实现对自定义外设的控制[15]。

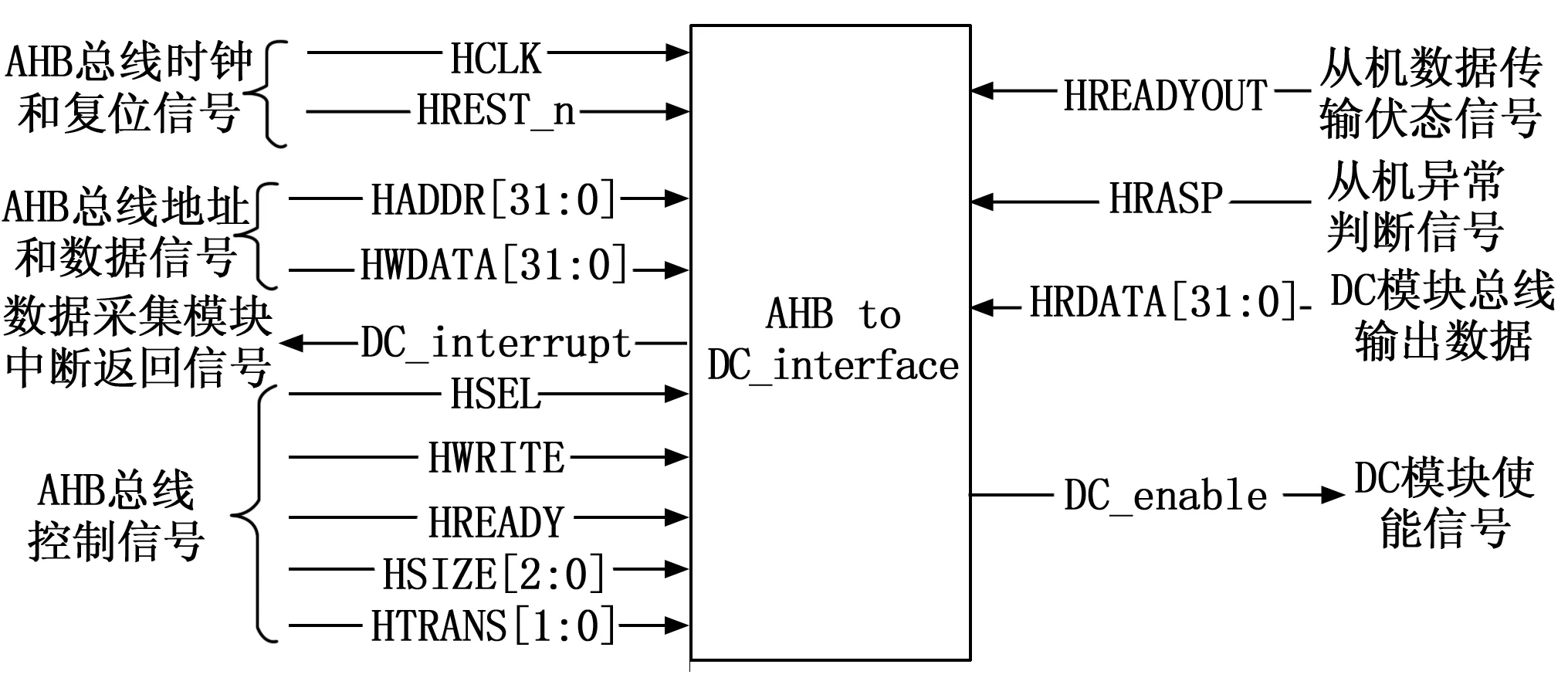

本设计对数据采集模块的设计需要实现数据采集模块与处理器模块的高速数据传输以及微处理器对数据采集模块的参数控制,因此本次数据采集模块专用接口的设计需要设计专用总线接口与数据采集模块的顶层端口一一对应,同时将Cortex-M3核内部的嵌套中断向量控制器(NVIC,nested vectored interrupt controller)模块接口与外设输出中断信号接口相连接,使得微处理器可以对数据采集模块的中断请求做出响应并执行相应的中断服务程序(ISR,interrupt service routines)。基于以上需求,整个数据采集模块专用接口的结构如图4所示。

图4 数据采集模块专用接口设计

图4中,左半部分主要为AHB总线与主设备输入接口部分,HADDR信号经过总线地址译码器选中数据采集模块的控制寄存器,再通过AHB总线控制信号对数据采集模块进行行为控制,如发出读写访问、产生使能信号、传递中断信号等。主机控制和数据传输过程按照AHB总线协议在片内进行,可以降低信号传输过程中的丢包率,微处理器对数据采集过程的控制也更为灵活。

图4中右半部分主要为从机对AHB总线传输的反馈信号和输出数据信号,HREADYOUT信号向主机反馈当前传输是否完成,高电平有效;HRESP信号则是判断从机是否正常工作,当其为高电平时触发从机中断信号,中断会传递给微处理器中的NVIC模块进入对应中断服务程序,微处理器将对数据采集模块进行复位操作。数据采集模块最终得到的数字形式MEMS陀螺仪输出角速度信号将按照32位的数据格式通过HRDATA数据总线传输到微处理器模块进行数据处理和存储。

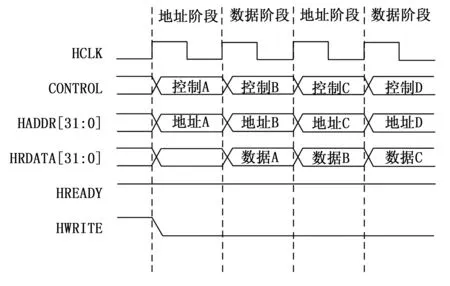

当MEMS陀螺仪正常工作时,微处理器模块将不断向数据采集模块发送读指令[16],即将控制信号写入数据采集模块对应的控制寄存器中,而陀螺仪所采集的陀螺角速度信号也将通过移位寄存器读出到数据总线HRDATA,这一过程中的关键信号时序如图5所示。

图5 AHB总线从机数据读取时序图

在这一读传输过程中采用了流水线的工作模式,在HWRITE信号确定了数据传输方向为总线从机到总线主机之后,每一个时钟周期中在确定总线可以进行传输的信号HREADY高电平有效时从上一时钟周期确定的地址中读取一次数据[17]。每一次读取的数据在放入处理器默认寄存器后,放入处理器专门放置数据采集模块数据的存储单元进行后续的信号处理和上位机传输工作。

3 SoC软件环境搭建及测试程序设计

SoC软件部分的设计主要包括软件开发环境的搭建和应用程序的开发,其优势主要在于软件开发成本较低,受芯片销量影响很小,可以在其他设备上应用;软件辅助设计工具较便宜;调试简单,不需要考虑设计时序、功耗等问题。

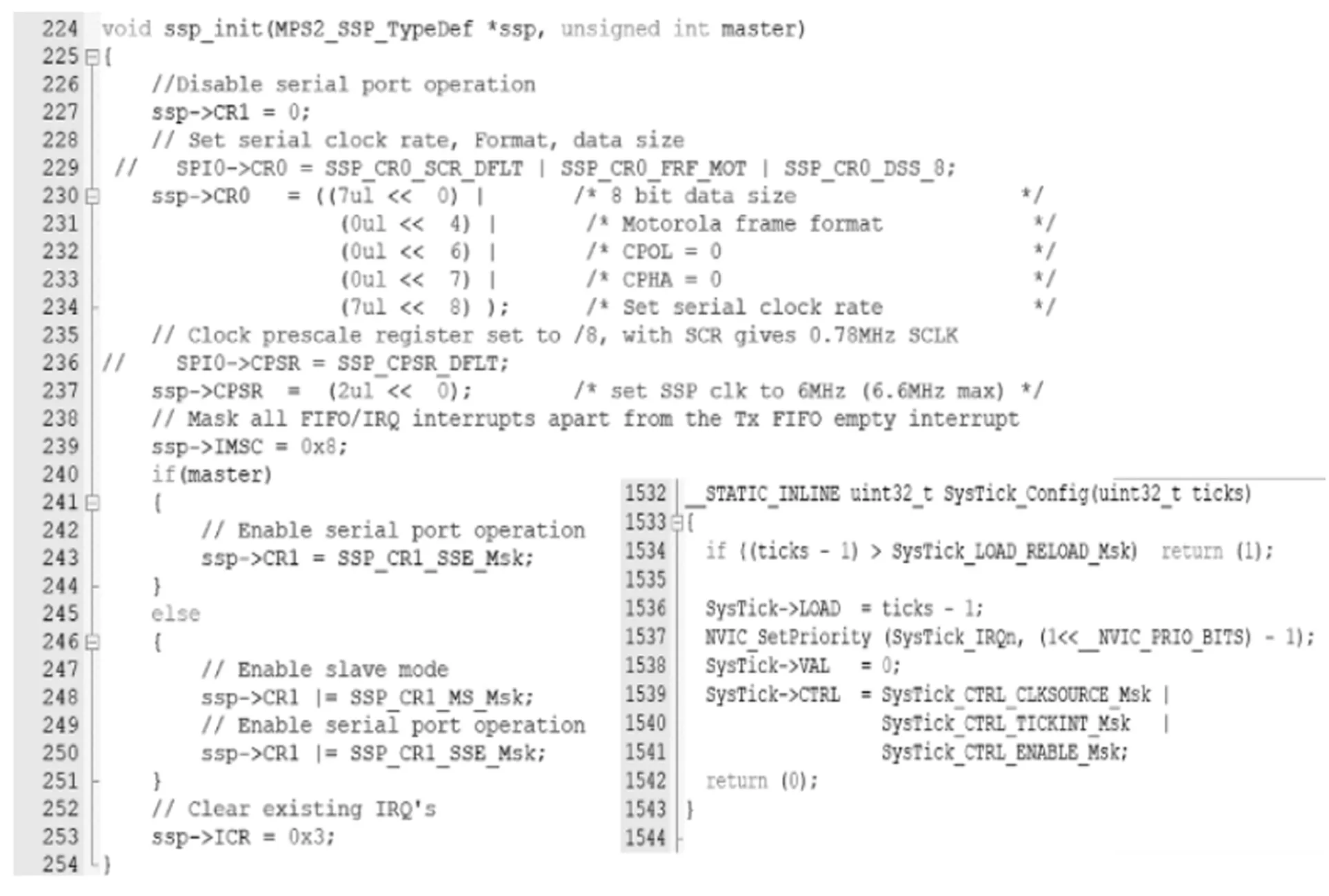

本文是基于ARM公司的Cortex-M3内核进行SoC的设计,因此使用ARMCortex微控制器软件的接口标准(CMSIS,Cortex microcontroller software interface standard)进行软件系统环境的搭建,通过标准化的函数定义简化软件环境搭建步骤,提高应用程序的可移植性[18]。CMSIS的定义主要分为内核访问层、设备外设访问层和外设访问函数三大部分,由于本设计硬件部分主要对MEMS陀螺仪的数据采集模块与Cortex-M3内核进行集成设计,因此相应部分软件环境搭建主要通过CMSIS-Core对内核的外设访问函数进行标准化定义,对处理器内部寄存器进行地址定义并建立统一的系统时钟,其程序如图6所示。

图6 标准化外设和系统时钟初始化函数

完成软件环境的搭建之后,根据硬件电路对数据采集模块的设计,在相应软件部分对外设寄存器组函数进行分配设计,实现对数据采集模块的软件控制和数据读取。为了验证SoC软硬件协同设计的效果,测试应用程序针对MEMS陀螺仪温度漂移的特点进行温度补偿程序的设计。

本设计将分段线性插值法的软件算法应用到SoC上进行对MEMS陀螺仪输出角速度信号的温度补偿,首先通过变温法采集MEMS陀螺仪在全温度区间(-40~85 ℃)的零偏变化量,之后将陀螺的零偏特性曲线等比例的分为若干个单调区间,计算每个区间对应的温补参数[19]。由于同一个陀螺具有较好的温度曲线重复性,因此可以根据区间对应温补参数在陀螺零偏-温度曲线的每个单调区间内分别进行线性插值补偿,降低陀螺温度漂移现象对陀螺输出的影响。

基于MEMS陀螺仪的工作温度分析,将温度区间按△T平均分为n个区间,通过插值法计算各个区间端点的平均零偏变化量,在单个温度区间内建立陀螺零位输出和温度相关的线性模型,可得:

Ui=Ui0+Ui1Tij

(1)

式(1)中,Ui为第i个温度区间的陀螺零位输出;Tij为第i个温度区间中的第j个温度点;Ui0和Ui1为第i个温度区间内陀螺温补参数。将全温度区间采集到的MEMS陀螺仪的零偏数据通过MATLAB进行拟合,获得n个温度区间内的陀螺温补参数,以表的形式嵌入到MEMS陀螺仪的软件算法中。

不同于传统的陀螺温度补偿模式的纯硬件逻辑处理或者经过低频数据接口到板级PCB上进行数据的转换和处理[20],本文所设计的SoC通过软硬件相结合的模式实现陀螺输出角速度信号的内部温度补偿处理。通过软件程序向数据采集模块的控制寄存器写入控制指令[21],将MEMS陀螺仪采集到的外界惯性信息从数据存储寄存器发送到SoC内部存储单元,经过分段线性插值温度补偿处理后整理成上位机所要求的数据格式后通过SPI接口实现上位机通信。

4 SoC性能测试及结果分析

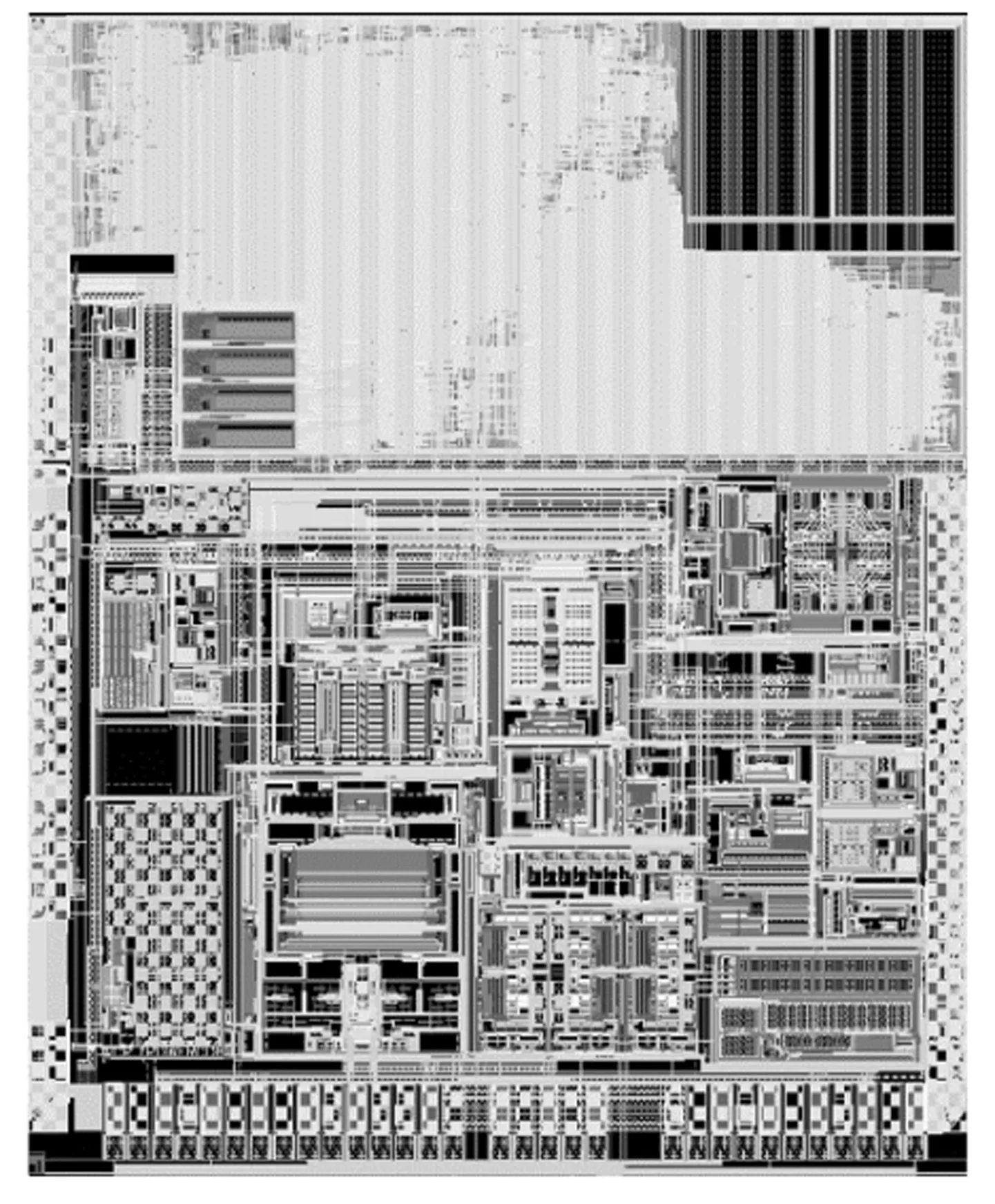

在设计电路的实现过程中,考虑到本SoC芯片中既有数字逻辑处理电路也有模拟电路,为了更好地发挥SoC芯片的综合性能,选用0.18 μm BCD加工工艺对SoC电路进行设计并加工,通过对RTL级电路设计的逻辑综合和物理设计,得到整个电路的版图如图7所示,版图尺寸为3.885 mm×4 mm。

图7 SoC版图设计

将物理验证后的二进制GDSII版图文件交付到某芯片制造厂流片可得到所设计的SoC电路芯片,将SoC芯片与MEMS陀螺表头进行金丝键合并封装得到可测试的集成MEMS陀螺仪,相比于ASIC芯片和单片机组合的陀螺形式,有效地减小了陀螺仪的体积,丰富了陀螺仪的应用场景。为了对SoC的设计功能和性能进行验证,选择对陀螺仪的输出温度漂移误差进行数字补偿测试,通过SoC芯片对MEMS陀螺输出信号进行温度补偿前后陀螺仪输出的全温零偏变化量的优化效果来验证SoC芯片的信号处理性能。

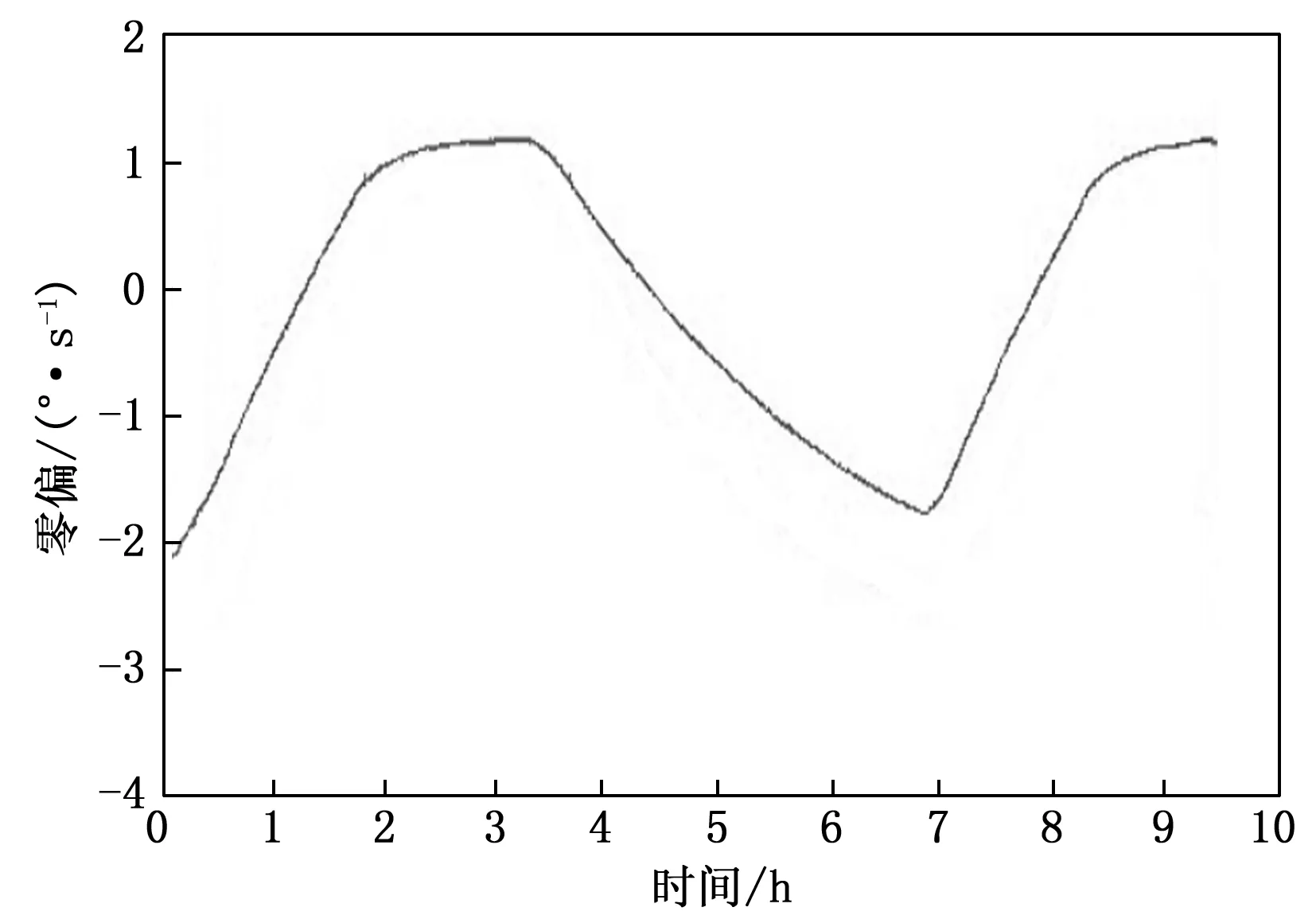

首先对没有烧写温度补偿程序的陀螺静态温度漂移情况进行测试,将待测陀螺静置在温箱中,设定温箱先缓慢降温至低温段(-40 ℃)后在两个小时内匀速升温至高温段(85 ℃),保持高温两个小时后以与升温时相同的速度降至低温段并保持两个小时完成一次温度循环,这一温度循环在测试过程中连续进行。测试的初始温度为室温,当陀螺温度稳定后,从升温过程开始对陀螺的输出信号进行采集,获得陀螺的输出曲线如图8所示。

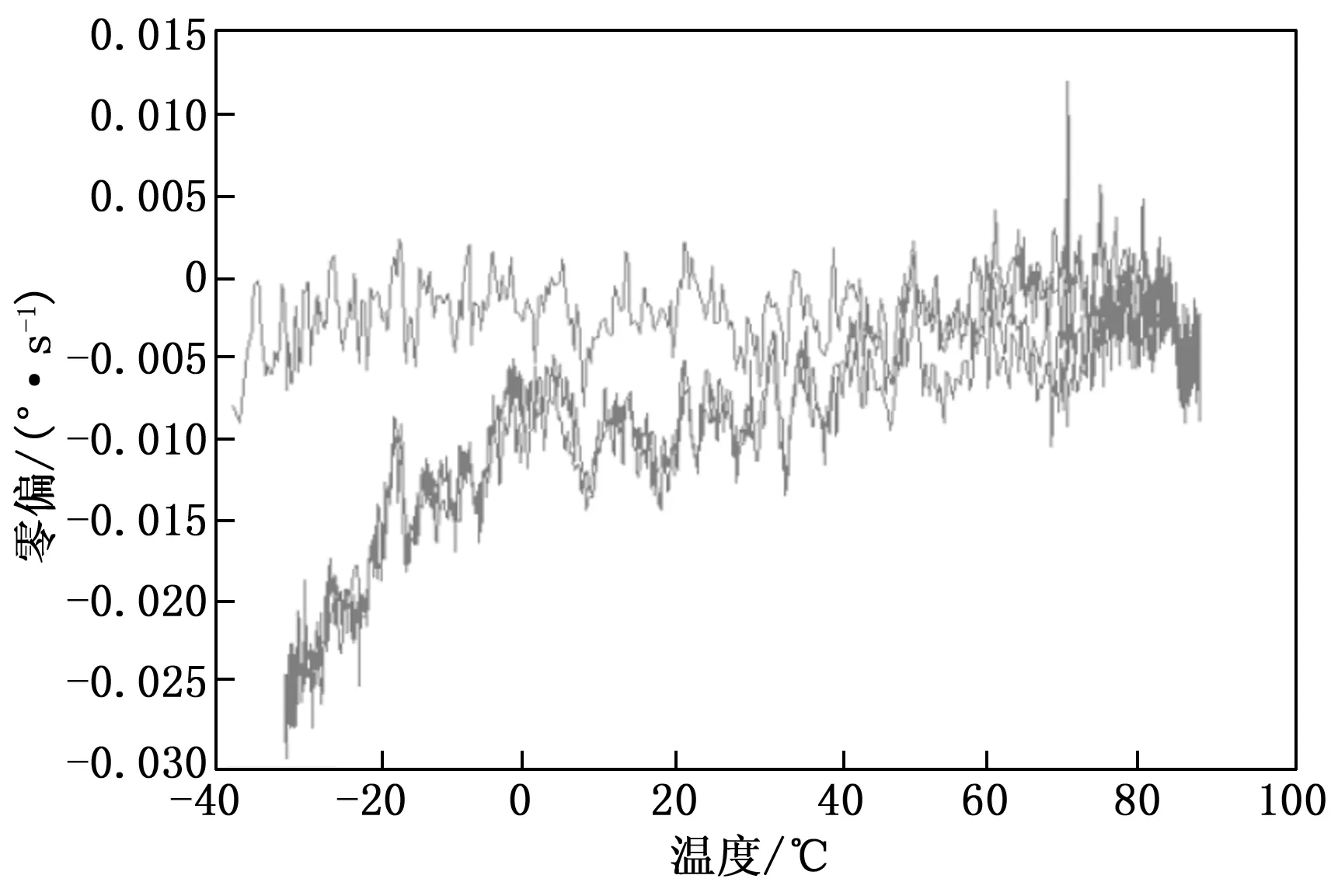

图8 温补前陀螺输出零偏曲线

根据陀螺输出零偏曲线的起伏变化可以看出,该陀螺的零偏漂移量与外界温度变化量大致呈现出正比态势。为了更为直观的表征出陀螺仪的输出零偏漂移和外界温度的关系,将温度传感器随时间的输出变化即实际测量温度数据作为横坐标,将MEMS陀螺仪全温度区间的零偏变化量作为纵坐标,可以得到如图9所示的陀螺零偏变化量随温度变化的试验曲线。

图9 温补前陀螺零偏-温度曲线

温度补偿前的陀螺零偏-温度曲线可以近似认为是一条倾斜的直线,具有较好的线性度,因此适合进行线性拟合,当将其分为若干个相同大小的温度区间,单个温度区间的线性度将更为突出,温度补偿处理的效果也会更好。

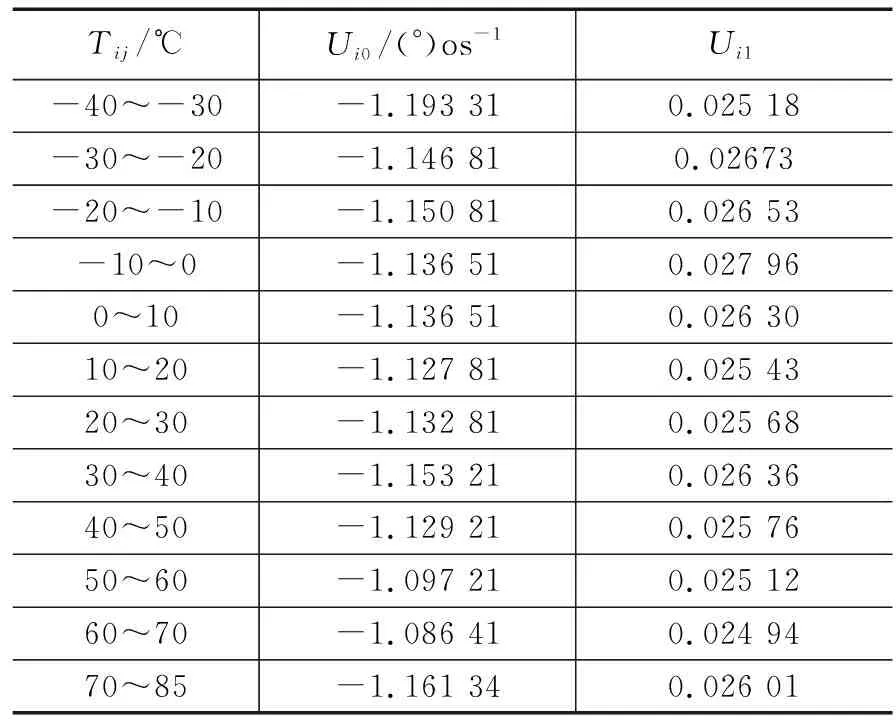

测试过程中采用分段线性插值法对MEMS陀螺仪在全温度区间的零偏温度漂移进行分段线性拟合,根据SoC性能验证需要及该陀螺温补前零偏-温度曲线良好线性度的实际情况,将温度按照每10 ℃为一个温度区间进行划分,根据式(1)计算可以获得各温度区间的温补参数,该陀螺仪的具体温补参数如表2所示。

为了验证SoC在实际工作中对MEMS陀螺仪性能的提升,将写入温补参数的陀螺放入温箱中,设定温箱固定温度循环流程运行,采集温度补偿后的陀螺仪输出,测试补偿后陀螺的全温度区间输出特性。集成有SoC的MEMS陀螺仪进行温度补偿后陀螺零偏的改善效果如图10所示。将同一陀螺在相同温度变化情况下的测试结果进行对比可得,温度补偿前MEMS陀螺仪的全温度区间零偏变化量为3.147°/s,温度补偿后全温度区间零偏变化量降低到0.035°/s,SoC对MEMS陀螺仪输出角速度信号的补偿效果明显,有效提升了陀螺仪的性能。

表2 陀螺零偏温度补偿参数

图10 温补后MEMS陀螺仪全温零偏

5 结束语

本文针对传统MEMS陀螺仪ASIC和单片机组合形式的数据处理模式,设计了一种应用于MEMS陀螺仪的SoC,采用0.18 μm BCD加工工艺对电路进行设计和制作,并配合自主设计的MEMS敏感结构进行测试。本SoC以ARMCortex-M3为基础,对SoC的数据采集模块接口进行了集成设计,将陀螺仪所采集的惯性数据直接通过AHB总线传输到微处理器中进行处理和存储,实现了MEMS传感器的小型化、智能化、集成化和高精度设计。流片后的SoC芯片测试结果显示,MEMS陀螺仪经过SoC的分段线性插值法温度补偿处理后,全温区温度漂移减少了两个量级,大幅提高了MEMS陀螺仪的温度特性,证明了专用SoC芯片设计的可行性和有效性。本SoC对于应用于陀螺的信号滤波处理及上位机通信等方面的研究开发尚有不足,接下来对于外围通信协议的开发以及数据采集模块的精确控制方向进行研究,进一步地提升MEMS陀螺仪的性能。