基于MicroBlaze的时间触发以太网终端设计与实现

2023-04-26顾青松艾斯卡尔艾木都拉马博阳刘兆沛

顾青松,艾斯卡尔·艾木都拉,马博阳,刘兆沛

(1.新疆大学 信息科学与工程学院,乌鲁木齐 830000;2.清华大学 计算机科学与技术系,北京 100084)

0 引言

机载网络通信系统结构的发展过程分为4个阶段:分立式航电系统、联合式航电系统、综合模块化航电系统和分布式集成模块化航空电子系统(DIMA,distributed)[1]。DIMA通过将硬件资源分成几个较小的单元,分布在整个飞机上,降低了综合模块化航电系统中央处理模块的尺寸、重量和冷却要求,并通过安全关键型通信系统连接,提供了更大的灵活性[2]。从航空电子系统和机载网络的发展过程可以看出,机载电子系统的数据交互需求越来越大,导致网络拥堵、线路间干扰和线缆重量等问题越来越严重,传统的通信网络已经不能满足航电系统的需求[3-5]。

时间触发以太网(TTE,time-triggered Ethernet)以太网是一种实时通信协议,它为分布式实时系统提供确定性实时通信服务,相比于集中式网络系统的优点在于:成本低,性能高[6]。IEEE标准委员会于 2002年提出了一种新的高精度时间同步标准,专门针对测试和测量、工业自动化、军事系统、制造系统、电力公用系统等应用领域测量和控制的需求,其时钟同步精度可达亚微秒级别[7-9]。国外研究机构和企业都致力于TTE技术研究和产品应用,但这些核心技术基本上都掌握在TTTech公司手中,用作轿车、飞机和航天航空系统中关键的传输控制信号[10]。国内对于时间触发网络的相关技术研究在各大航天科学院、研究所、高校科研项目中仍处于研究探索阶段。

本文针对确定性机载网络通信系统实时性强、可靠性高的需求,使用IEEE 1588时间同步协议设计了一种基于MicroBlaze的TTE终端的实现方案并进行了实验测试。文章主要分为5个部分:第一部分介绍了TTE终端设计的整体结构;第二部分介绍了实现时间同步的方法;第三部分介绍了四余度机制的可靠性设计;第四部分进行测试和验证;第五部分进行总结和展望。

1 TTE终端整体结构

新一代综合航电系统对机载网络通信系统的实时性、可靠性和确定性等方面的性能需求较高,然而嵌入式系统有内核占比小,实时性高,专用性能强,响应快等特点,适合实时和多任务体系的要求[11]。在嵌入式系统中使用FPGA内部的通用逻辑资源实现的 MicroBlaze软核作为嵌入式处理器,外部搭建需要的相关IP核,可以实现可编程片上系统的设计。

1.1 硬件平台选择

硬件平台以MicroBlaze为控制核心,主要由以下几个模块组成:电源模块、时钟模块、定时器模块、串口模块、千兆以太网子系统通信模块和片上搭载的外部存储器DDR3 模块,其功能如图1所示。

图1 硬件功能框图

光通信功能由千兆以太网子系统通信模块联合光纤收发器完成,千兆以太网通信模块在GTP的基础上封装以太网协议,而光纤收发器作为与外部设备连接的物理接口,内部与GTP模块相连,实现硬件平台与上位机的数据交互。串口模块基于Xilinx的UART IP 核完成,在外部使用USB转串口模式与上位机相连,用于软件程序debug。定时器模块使用Timer IP核,主要用于记录时间和实现定时器中断,是完成时间同步的主要模块。数据缓存模块使用DDR3 IP核驱动核心板上的外部存储器DDR3,用于数据写入和读取。

相比于普通的网络接口,使用“光纤接口 + SFP光模块”设计适配性好,抗干扰能力强,因此使用此模式实现硬件系统与上位机之间的通信。

硬件平台与上位机之间的数据交互使用串行千兆介质传输协议(SGMII)。光纤收发器集成了光电转换电路和电光转换电路,可以同时完成信号的接收和发送,避免用独立原件搭建电路带来的困难。SFP光电转换模块是可热插拔的小封装模块,其体积是传统的千兆位接口转换器模块的一半[12]。使用光纤收发器和SFP光电转换模块作为光纤通信的基础硬件,可以提高系统的适配性,保证系统性能。

1.2 四通道千兆以太网光通信硬件平台的设计

MicroBlaze软核处理器通过四路光纤接口与四台上位机通信的功能实现,其系统平台如图2所示。

图2 四通道网络系统平台框图

在硬件平台中使用单核MicroBlaze和4个以太网子系统IP核分别驱动四路SFP光通道,通过千兆 RJ45网线与4个PC端相连,完成千兆以太网光通信硬件总体设计。PC端通过串口与硬件平台相连,查看debug数据。其中,4个以太网子系统IP核需要通过配置共享逻辑功能实现硬件平台的开发[13]。

2 时间同步功能设计

时间同步是时间触发通信的基础。对于时间触发网络,包含时间触发网络控制器、以太网控制器、TTE交换机和TTE交换机终端设备。TTE交换机终端与TTE交换机上的不同端口相接用做数据备份。

2.1 时间同步硬件设计

时间同步网络系统是在四光口网络基础上加入了时间同步机制,系统框图与四光口系统结构大致相同。

本文采用的是端对端时钟同步方案,主机与从机之间通过光口进行数据交换,在 SFP光口中插入光电转换模块,用千兆以太网 RJ45 网线相连。时间同步过程严格按照 IEEE 1588 协议主从式同步方案,最后由从机计算出时间同步延时和偏差。从机使用串口通信模块与 PC 端相连,可以将时间同步结果通过串口发送给 PC 端,在PC端看到时间延时和时间偏差数据,硬件系统如图3所示。

图3 时间同步硬件系统框图

在时间同步硬件系统中,主从节点的时钟都是由定时器模块产生。通过使用定时器模块的定时中断功能设计时钟。

2.2 时间同步协议报文

IEEE-1588精密时间协议(PTP,precision time protocol)可以封装为两层协议或四层协议,具体的格式大致分为两类:1)Ethernet+PTP;2)Ethernet+IPv4+UDP+PTP[14]。

二层以太网PTP报文不需要进行IP报文和UDP报文封装,直接将PTP报文加入到以太网帧的数据段中。这样做的好处是链路中解析数据需要的时间减少了,可以提高时间的同步精度。缺点也很明显,在整个以太网数据帧传输过程中,只进行了一次CRC数据校验,如果数据出错,就没有一个数据容错机制检验数据的可靠性。虽然在通信链路中,四层以太网 PTP 报文的复杂度高,数据解析时间相对较慢,时间同步精度会降低,但是保障了数据的可靠性和完整性,所以本文采用四层以太网 PTP 报文协议。时间同步协议帧格式如图4所示。

图4 四层以太网 PTP 报文

其中的 PTP 报文包含3个部分:报文头部、报文主体和报文扩展[15]。其中,报文头部长度为 34 字节,本文主要按照报文类型字段进行判断,其余不用字节填充为 0x00;报文主体主要用于承载 PTP 报文时间戳,长度可变,本文设计长度为 7 字节;报文扩展是可选部分,可以不做填充。

采用主从同步方式,PTP 事件报文可以不用携带时间戳,将 PTP 事件报文定义为 34 个字节,PTP 通用报文定义为 41 个字节。在 PTP 报文头部定义类型字段,主机发送 PTP 消息,从机根据报文类型(messageType)字段来判断 PTP 报文类型,将4种报文类型字段分别定义为以下格式:

1)同步报文类型:0x00。

2)跟随报文类型:0x08。

3)延迟请求报文类型:0x01。

4)延迟请求应答报文类型:0x09。

2.3 时间同步软件功能设计

在嵌入式网络设备中,由于硬件资源的限制,采用 LWIP(Lightweight IP)[16-17]轻量级 TCP/IP 协议栈实现千兆以太网 UDP 通信。在使用 UDP 通信过程中,由于一个通道设置一个 MAC 地址、 IP 地址和端口号。即在建立四光口通信时,需要设置4个不同的 MAC 地址、 IP 地址和端口号,加入4个通信网络和4个互不相关的 UDP 接收回调函数,以便可以接收到4个端口同时发送过来的数据,减少数据丢失现象,设计流程步骤如图5所示。

图5 UDP通信设计流程

主要分为以下5个步骤。

1)主函数中设置4个不同的 MAC 地址和 IP 地址。

2)调用 xemac_add()函数。 xemac_add()函数是 LWIP 中 netif_add()函数的封装,其功能是将网络接口加入网络列表中。需要使用此函数把4个网口的网络接口参数输入网络中。

3)在中断初始化函数中,使用启动中断函数,将4个以太网子系统中断 Id 写入函数中。调用此函数后,将出现中断 Id 的任何从属控制器挂起,用于响应中断函数。

4)对于启动应用程序 start_application()函数,建立4个 UDP 端口和 UDP连接。使用 udp_new()函数,创建 UDP PCB 结构,用于UDP通信;udp_bind()函数,将PCB与本地地址绑定;udp_connect()函数,使UDP PCB与远程地址相关联。

5)在接收数据方面,需要为UDP PCB设置接收回调函数。建立4个不同的udp_recv()回调函数,防止在一个端口接收处理数据时占据所有进程,使其余端口出现数据丢失的情况。当接收pcb的数据报时,将会调用此回调函数。

本文通过定时器中断设计时钟,将时钟划分为:时、分、秒、毫秒和微秒5个部分。时间同步流程如图6所示。

图6 时间同步流程图

其大致步骤为:

1)主节点向从节点发送同步报文并记录发送时间t1,从节点收到报文并判断报文类型是否为同步报文。如果是同步报文,记录报文到达时间为t2;如果不是,则丢弃数据并重新接收下一组数据。

2)主节点将时间t1加入到跟随报文的时间戳中并发送给从节点,从节点收到报文并判断报文类型是否为跟随报文。如果是跟随报文,从节点提取时间戳得到时间t1并向主节点发送延时请求报文,记录发送时间t3;如果不是,则丢弃数据并重新接收下一组数据。

3)主节点收到报文并判断是否为延时请求报文。如果是,则记录报文到达时间t4,并将时间t4加入到延时请求响应报文中,然后发送给从节点;如果不是,则将数据丢弃并重新进行时间同步流程。

4)从节点接收到报文后判断是否为延时请求响应报文。如果是,则提取时间戳得到时间t4,并根据得到的4个时间计算出时间同步延时和偏差,修正从节点时钟;如果不是,则将数据丢弃并重新进行时间同步流程。

3 可靠性设计

机载网络作为航空电子系统的互联通道,其可靠性直接影响航电系统的正常工作乃至飞行器的安全[12]。为保证整个网络通信系统的任务可靠性,通常采用高可靠的设计方案以及有效的容错机制,保证在子系统出现故障时不会导致整个系统无法工作。本文在传输层采用 MD5(Message-Digest Algorithm 5)数据加密算法保证了数据的完整性,并采用四余度表决机制设计了一个容错通信层保证通信系统的可靠性。

3.1 传输层可靠性

MD5数据加密算法用于提供消息的完整性保护,其基本原理是将数据信息压缩成 128 位的 2 进制数,并且产生信息摘要[18]。根据 MD5 算法计算方式,不可能生成具有相同消息摘要的两条消息。虽然现在此算法被已有碰撞攻击破解了不可逆性,但是由于其在32位机器上计算速度快和易压缩性,作为嵌入式数据加密还是很有必要的。发送端程序设计流程如图7所示。

图7 发送端 MD5 数据加密设计流程图

将开源的C语言MD5算法移植进网络中,发送端程序流程设计步骤如下:

1)需要发送的数据作为 MD5 算法输入。

2)经过 MD5 计算后得到32位16进制数据。

3)将 MD5 加密数据加入到发送数据帧帧尾。

4)发送数据帧。

在接收端需要将传输数据进行解析,提取数据帧后 32 位校验数据,再将剩余数据经过 MD5 计算后得到的加密数据与提取的 32 位校验数据进行对比,判断整个数据帧的完整性和有效性。程序设计流程如图8所示。

图8 接收端 MD5 数据校验设计流程图

接收端程序流程设计步骤如下:

1)首先判断接收到的数据包是否为空。

2)如果为空,将数据包丢弃,并释放 pbuf 空间;不为空,将数据先提取出来放入数组缓存中。

3)提取数组的后32位16进制数据,放入校验数组中。

4)将提取后的数据作为 MD5 算法输入。

5)得到的输出数据与之前放入校验数组的数据进行逐一对比,判断两组数据是否一致。如果相同,则数据正确;如果不同,就是数据出错,将数据丢弃,清空数组缓存,准备接收下一组数据帧。

3.2 容错层可靠性

容错通信层在通信系统的传输层和用户服务程序的应用层之间,为了提高系统可靠性,机载网络通信系统中采用了多余度的设计方案,避免单通道系统故障后无法保证系统安全工作[19]。多个余度同时工作时,如果多个信息来源的数据一致,直接将数据提交给上层服务程序即可;如果不一致,就需要进行余度表决,再将表决模块得到的输出数据传送给上层服务程序[20]。

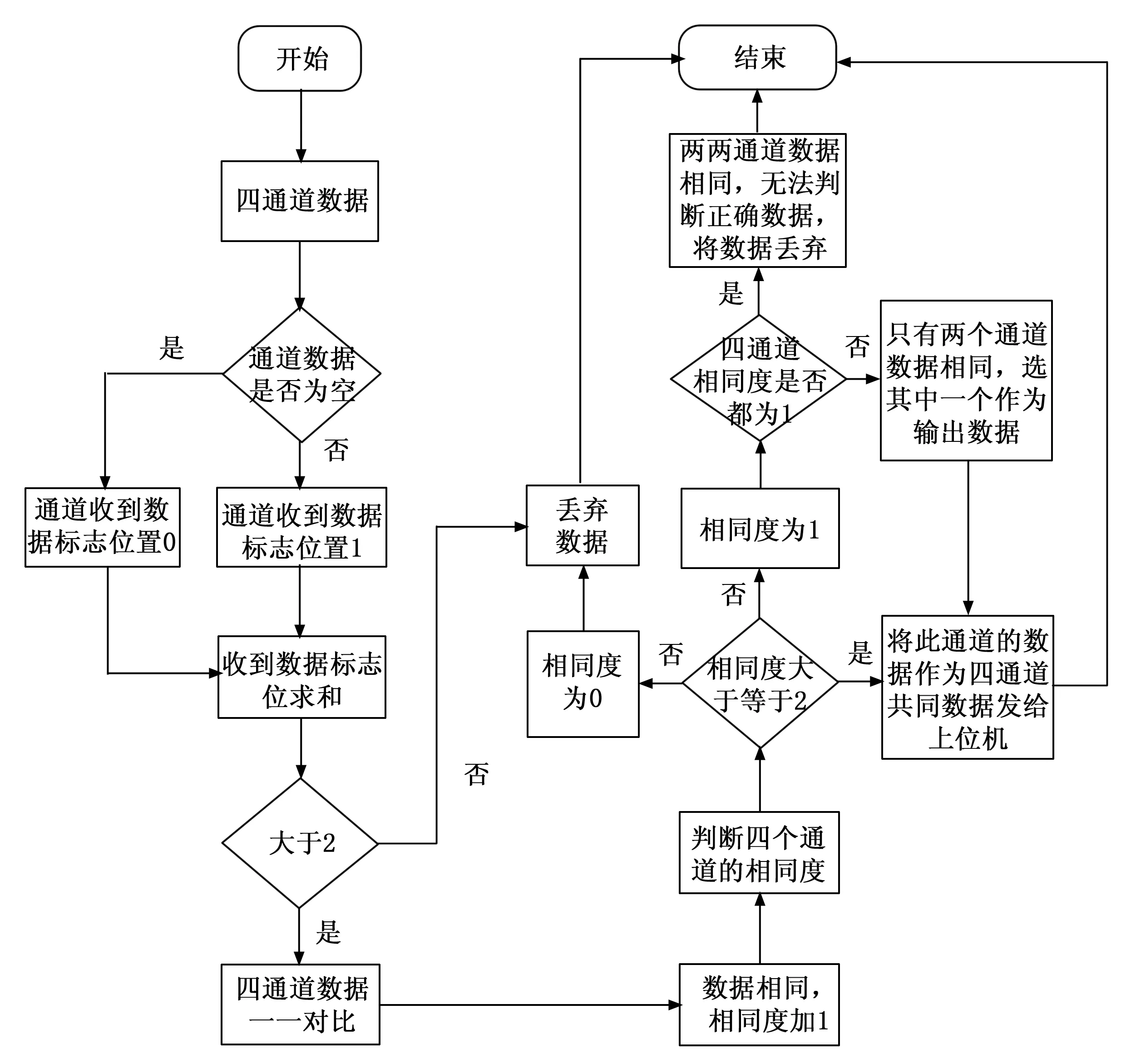

四余度表决控制系统的输入是上一层MD5数据校验层的输出数据。单通道系统经过数据校验层后还需通过四余度表决层进行余度表决输出,得到的最终数据便是正确传输数据,程序设计流程如图9所示。

图9 四余度表决系统设计流程图

四余度表决设计步骤如下:

1)4个通道分别判断是否有数据传输进来,如果有数据传输,将接收此数据的通道数据标志位置为1;如果没有数据传输,则通道数据标志位置为0。

2)把得到的4个通道的数据标志位相加,判断其总和。如果总和值大于2,则采用比较表决,将各个通道的数据一一对比;如果总和值小于等于2,则说明通道数据不在同一时刻发送,或者在数据传输过程中出现丢包情况,此时将数据丢弃。

3)在数据对比过程中,定义4个相似度标志位。若通道数据相同,相似度标志位加一;若通道数据不同,相似度标志位加零。此标志位用来对各个通道的传输数据相同性和完整性判断。

4)对相似度标志位判断,如果此通道的相似度数值最大且大于等于2,则把此通道的数据作为正确数据存入 DDR 中。或者设置回环,把正确数据作为4个通道的发送数据,发送给上位机,在上位机中观察此接收数据与上位机发送给硬件平台的数据是否相同。如果此通道的相似度数值等于1,会出现两种情况。一是只有两个通道的数据相等且这两个通道相似度为1,其余通道数据都不相同,则正确数据选择相似度为1的通道数据;二是所有的通道相似度都为1,代表4个数据通道两两相同,无法判断正确数据是哪条通道的,则将所有通道的数据丢弃,重新接收下一组数据。如果相似度等于0,则说明数据出现错误,需要把所有通道的数据丢弃,重新接收下一组数据。

4 系统测试

4.1 硬件平台速率测试

硬件平台采用 Xilinx 公司生产的AX7101 FPGA 开发板,其型号为 XC7A100T-2FGG484I,选用的 FPGA 芯片为 Xilinx 公司 Artix-7 系列的 XC7A100T。在通信接口方面,4 个 GTP 收发器连接了最高可达 6.6 Gb/s,用于光纤通信,带宽为1 Gbps,满足高速数据传输和交换的要求。硬件开发平台为 Xilinx 公司设计的软件 Vivado 2017.4,软件驱动开发平台为 Xilinx SDK 2017.4。本软件开发中使用 C/C++ 进行开发。

将光电转换模块插入 SFP 光口中,通过 RJ45 千兆以太网网线把硬件平台与 PC 端相连。在 PC 端设置以太网本地连接适配器,将本地主机 IPv4 地址设置为:192.168.1.100,与硬件平台同一网段。打开网络调试助手,配置本地主机端口号为:5101。远程主机地址设置为:192.168.1.10,端口号为:5001。本地主机向远程主机发送 20 个字节的十六进制数:0x68,0x74,0x74,0x70,0x3A,0x2F,0x2F,0x77,0x77,0x77,0x2E,0x63,0x6D,0x73,0x6F,0x66,0x74,0x2E,0x63,0x6E。PC 向硬件平台发送数据,硬件平台收到数据后将数据再发还给上位机,完成一个回环测试,通过数据日志可以看到发送数据与接收数据一致,硬件平台与上位机可以正常通信。

使用 iperf 软件测试连接速率,输入命令“iperf-c 192.168.1.10-u-b1000M-t 60-I 5-l 64k-p5001”,指定 iperf 以客户端启动,使用 UDP 连接到 IPv4 地址为:192.168.1.10 ,端口号为:5001 的服务器上,传输带宽为 1 000 M,缓冲区大小为 64 kB,测试时间为 60 s,每隔 5 s 打印输出测试结果。如图10所示。

图10 UDP连接性能测试

Interval 是测试时间段,Transfer 表示该时间段内传输的数据总量,Bandwidth 为该时间段内的平均带宽。从测试结果可以看出,UDP 连接在 5 s 内的传输数据总量在 346~387 Mbytes,5 s 内平均传输数据量约为 370.3 Mbytes,平均每秒传输数据量约为 74 Mbytes/s。虽然达不到理论上千兆以太网每秒传输数据的要求,但也远远高于百兆以太网的每秒传输数据量标准。其每分钟传输数据总量可达4.34 GB,在这段时间内带宽稳定在 600 Mbits/s 以上,平均带宽约为 621 Mbits/s。

4.2 时间同步测试

在硬件平台间采用端对端的测试。从节点采用的是 AX7101 FPGA 通信板卡,主节点采用的是米联客的 MA704FA-200T 开发板。此开发板的核心板使用 Xilinx Artix-7 FPGA 芯片,型号为 XC7A200T-2FBG676I。在通信接口方面,开发板上有 2 路 SFP 光口,速度高达 6.6 Gb/s。测试结果通过串口发送给 PC 端。两个硬件平台通过光纤接口插上 SFP 光电转化模块相连,通信链路采用 RJ45 千兆网线。从机将测试数据计算结果通过 UART 发送给上位机,上位机在串口调试助手中观察测试数据。

将时间同步周期设置为 1 s,测试 10 次时间同步后的链路传输延时,延时数据如图11所示。

经过 10 次时间同步,其延时数据首先呈明显下降然后平稳的趋势。由于定时器定时中断时间是 100 μs 触发一次,所以时钟的最小单位是 100 μs。根据时间同步算法和得到的延时数据可以推算出延时区间在 150~250 μs,误差区间在 100 μs。由于无法得到更精确的延时数值,且时间同步精度达到了微秒级,所以误差仍在可容受范围。

4.3 可靠性测试

将4个通道的本地主机 IPv4 地址分别设置为:192.168.1.100、192.168.2.100、192.168.3.100、192.168.4.100。主机端口号修改至空闲端口,分别为:31777、32777、33777、34777。远程主机 IPv4 地址分别设置为:192.168.1.10、192.168.2.10、192.168.3.10、192.168.4.10。远程主机端口号分别设置为:317、32769、33769、34769。使用网络调试助手进行测试。

首先使用MD5校验工具将测试数据进行计算,得到的MD5加密数据为32位16进制数:0xC20AD4D76FE97759AA27A0C99BFF6710,测试数据为4位16进制数(0x31,0x32),发送数据为测试数据加上MD5加密数据。

为了测试设计的四余度表决机制和 MD5 数据校验的可靠性,对整个系统进行了3个方面的测试:

1)发送相同的测试数据和 MD5 校验值,测试了工程的完整性和准确性。

2)修改 MD5 加密数据,测试了传输层数据校验的可靠性。

3)对四余度表决系统进行测试:首先对双通道发送两个不同的数据,其余通道数据与其中一个通道数据相同,测试余度表决机制符合设计。其次,对三通道发送不同数据,剩余通道与其中一个通道数据相同,分析了测试结果符合设计。最后,将四通道分成两组,两组数据不同但组内通道数据相同。经过测试,得到的结果符合设计,如图12所示。

图12 最终测试结果图

5 结束语

本文设计了一种基于 MicroBlaze 的时间触发光以太网终端的方案,可以满足航电系统的高带宽、强实时、高可靠的要求。实现了以单核 MicroBlaze为核心的四光口千兆以太网光通信方案,提出了一种使用 MicroBlaze 实现时间同步功能方法。针对机载网络的可靠性问题,在传输层使用 MD5 数据加密算法,提高数据的完整性。设计了一种四余度表决机制解决数据一致性问题,提高机载网络系统可靠性。但仍有许多不足之处,由于在时间同步过程中没有设计合适的时间补偿机制,时间同步误差区间仍然不小,需要设计时间补偿机制增加时间同步精度。