基于FPGA的千兆网络端系统数据传输设计

2023-04-06孟开元唐君妍曹庆年楼晓强

孟开元 唐君妍 曹庆年 楼晓强

关键词:FPFA;千兆AFDX;端系统;PCIe接口;可靠性

0 引言

随着数据流和多媒体服务的增加,具有高功率、快速和多功能模块的高性能网络产品的市场容量也不断增加。以太网在数据中心网络中发挥着重要作用,在移动网络、汽车、航空和制造业中有许多新的用武之地。尤其是在航空网络领域,通常需要对各种飞行试验过程中的关键数据进行接收和存储,对不同电子设备间高集成度、高效率、低成本、大容量的数据传输有着很广泛的需求。

AFDX网络是一种双余度网络,提高了传输速率,并且通过在AFDX网络端系统中引入虚拟链路、冗余管理等概念,不断优化以太网网络结构,使网络中的数据传输拥有更高的实时性、可靠性和确定性。目前,AFDX网络在航空电子领域中大多采用百兆级别的速率[1],为了满足传输网络中更高更严格的速率要求,需要研究千兆级别的AFDX网络时突破设备瓶颈的着力点。

本设计给主机配置4线的PCIe2.0接口,以太网内部连接选用RGMII接口连接模式,通过FPGA对发送和接收进行逻辑控制来实现传输网络中的可靠性数据传输功能,更适合需要千兆以太网的高速传输场合。

1 AFDX 端系统介绍

1.1 AFDX 端系统架构

AFDX端系统主要实现网络体系结构模型中的物理层、数据链路层、网络层和传输层的功能[2]。

物理层根据AFDX端系统中的两路PHY芯片来实现,每个PHY芯片都能提供一路以太网通信的接口。数据链路层的协议功能够通过FPGA逻辑来实现,负责完成端系统的虚拟链路调度功能和数据的冗余管理功能。网络层和传输层的相应协议完成对传输数据的封装、拆解、分片、重组等。

AFDX端系统在传输时还需保障数据的安全性和可靠性[3]。通过对端口和虚拟链路的相关配置,保障数据传输的安全性和准确性,有效避免传输过程中以数据帧发生冲突;采用两个独立的冗余网络进行传输,避免数据在传输过程中发生丢失,进一步提高了数据传输的效率,保障了网络传输的高可靠性。

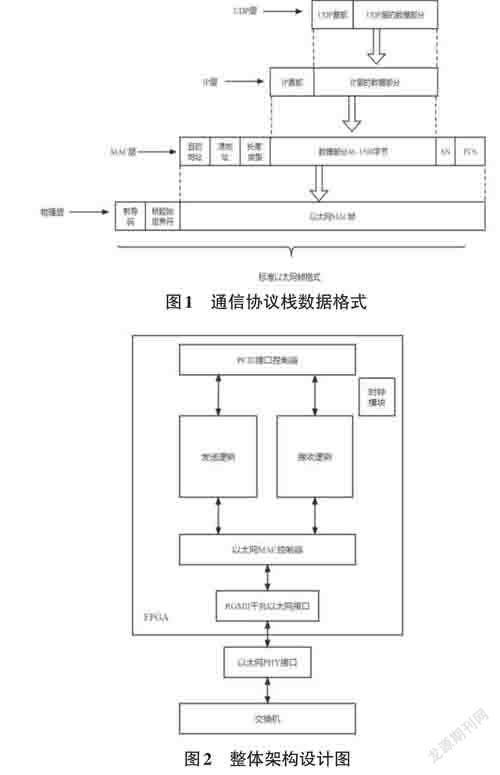

1.2 通信协议栈数据格式

本文通过硬件描述语言实现UDP/IP协议栈,根据项目中对数据传输协议的实际功能需求,只实现UDP和IP协议,就能满足高速以太网传输数据的稳定和高速传输。

在进行数据传输时,消息数据会经过每一层的协议栈,按照该层协议的数据包格式要求,逐层进行封装、打包。数据每经过一层协议,都会在数据包的首部添加相应包头的信息,然后进入下一层协议栈再重新封装和打包。本设计首先在用户数据前添加UDP 首部信息组成UDP数据报,UDP数据报再传至网络层,添加IP数据报的首部信息封装成IP数据报,然后传至以太网MAC 层封装成以太网的标准数据帧格式,最后送到物理层进行发送处理。以太网有效数据封装为标准格式之后才能进行传输,具体的UDP/IP 协议栈格式如图1所示。

2 系统设计

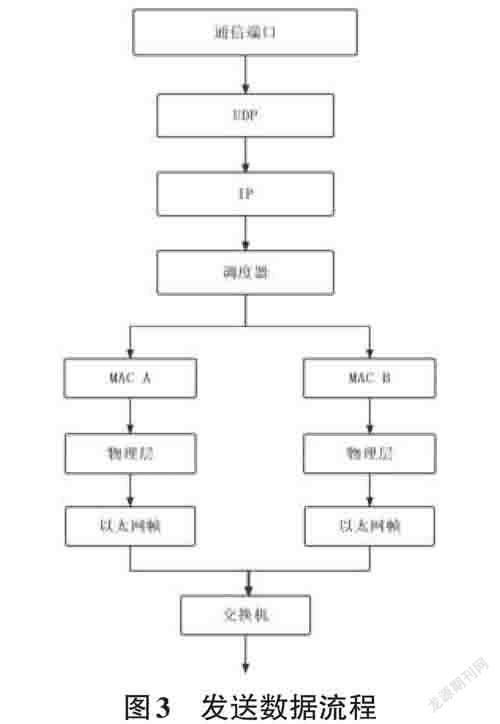

2.1 整体架构设计

整个设计的模块结构主要划分为主机PCIe接口、发送逻辑、接收逻辑、以太网接口和时钟模块。主机通过PCIe接口将创建的消息发出,经过发送逻辑的控制,从以太网接口发出数据帧给交换机,再发往其他设备;数据帧从以太网接口传来,经过接收逻辑的控制,再从PCIe接口传入主机接收。系统整体架构设计如图2所示,图中黑框部分需要通过FPGA逻辑来实现具体功能。

2.2 时钟设计

1) 系统时钟

2.3 接口设计

1) PCIe接口设计

PCIe接口包括PCIe_DMA(由PCIe协议处理模块和DMA模块两部分组成)、DMA_AHB模块、寄存器模块和时钟复位模块。PCIe协议处理模块可以支持端点、根端口的工作模式;DMA模块可以支持包DMA或块DMA的工作模式[4]。

MAC(媒体访问控制)协议应用于OSI参考模型中的数据链路层中,完成的功能是控制与连接物理层的物理介质。PHY(端口物理层)属于OSI协议中的物理层[6]。PHY与MAC控制器之间有多种连接接口可以选择:十兆和百兆以太网通常采用MII、RMII接口;千兆以太网中通常采用GMII、RGMII等接口。相对于GMII与PHY接口连接,RGMII接口减少了接口管脚的数量,数据信号和控制信号减少,同时发送接收数据采用双沿驱动,可以明显地减少FPGA的I/O端口数量的占用,因此本设计采用RGMII接口。在1000M的传输速率下,使用125MHz的时钟频率。

2.4 发送逻辑设计

发送数据的具体流程如图3所示:

发送数据时,外部CPU在内存中创建消息,通过主机PCIe接口访问内部寄存器,将消息的地址和长度等信息填入相关寄存器。系统按序自主完成通信协议栈中的UDP层、IP层、MAC层数据的封装,最终组装成标准的以太网数据帧后发送至以太网接口进行传输。两路网络中复制相同的数据帧进制进行发送。

虚链路是AFDX端系统通信的核心部分[7],虚链路之间需要实现逻辑独立,这一要求通过对带宽分配间隙进行限制的方法来实现。当端系统中需要完成多个发送任务时,调度器就会依据BAG进行流量控制来防止数据帧在传输时发送冲突。AFDX端系统的这一功能是在数据链路层通过FPGA逻辑实现的。

2.5 接收逻辑设计

接收数据的具体流程如图4所示:

系统首先对从以太网接收的数据帧进行冗余管理操作,采用“先到先有效”的算法,即第一个带着有效顺序号(Sequence Number,SN) 的数据帧将被系统网络接收,并向上传输,通过协议栈的层层数据拆解将信息送达接收端口。但当带有相同顺序号的第二个数据帧被传进网络时,该帧将被丢弃,不能被网络所接收。通过余度管理的检测后,当数据帧的目的寻址信息与系统配置的MAC接收地址相匹配时,才可以从以太网帧中删除MAC头部信息。移除MAC首部的帧为IP数据报,系统处理IP数据报报头中包含的地址和控制信息,当地址和控制信息与系统配置值相匹配时,系统才可以从IP数据报中删除IP报头。删除IP报头后,剩下的是UDP数据报,系统处理UDP数据报的地址和校验和的值,当地址与系统配置的值相匹配且校验和的值为0时,才可以从UDP数据报中删除UDP报头信息并将有效负载存储起来等待端口接收。

3 系统测试结果

为了验证在千兆以太网中的数据传输功能,使用Xilinx的ZYNQ7000系列的开发板进行测试[8],板卡与主机PCIe接口相连,并通过Wireshark软件进行抓包来观察实验结果。为了方便观察,将系统的发送和接收端口设置为同一个,即源地址和目的地址相同、源端口号和目的端口号相同。系统最终抓包测试结果如图5、图6所示。

从测试结果图可以看出,设计的系统可以进行正常的数据报的收发,即可完成网络数据传输的功能。

4 结论

本文通过对AFDX端系统技术进行分析和研究,在原有百兆AFDX 网络的基础上,提出一种基于FPGA 的千兆网络端系统的设计方案,通过对千兆AFDX端系统结构设计和数据传输逻辑设计的改进,实现了系统的数据传输功能,可以满足更高可靠性、更高确定性和更高速率的大体量数据传输要求。经过测试,数据传输模块也能在以太网中正确收发千兆速率的网络数据,可以很好地应对当下航空网络系统的高速率、大容量的數据传输需求,也具有较好的应用前景和开发意义。