大带宽数字信道化接收及重构系统的实现

2023-03-29罗加钰赵忠凯

罗加钰,赵忠凯

(哈尔滨工程大学信息与通信工程学院,黑龙江 哈尔滨 150001)

0 引言

基于多相滤波的数字信道化系统具有大动态范围、多信号处理能力、高灵敏度以及大瞬时带宽的优点[1]。传统接收重构系统处理射频信号需经射频模拟电路处理后才能进行数字化处理,结构复杂且体积大[2]。随着高速模/数(ADC)以及数/模转换芯片(DAC)技术的发展,国内已经具备生产吉赫兹量级芯片的能力[3],可支持中频采样甚至直接进行射频采样,有助于降低相关硬件的体积和功耗,从而满足导弹、无人机等对载重、功耗有严格限制的平台的需要[4]。针对上述平台需求,本文设计了一种大带宽数字信道化接收及重构系统。该系统在射频采样的基础上,利用正交镜像滤波器实现接收和重构滤波器组的设计,减少信号失真;同时根据实信号信道化处理后信号的共轭特性,在基带数据处理时仅对一半信道输出数据进行处理,节省FPGA 逻辑资源;最后在搭载了处理速率为9 GHz 的国产ADC/DAC 的平台上进行了验证,实测结果与仿真结果基本一致,验证了方案的合理性。该系统可处理多个同时到达信号,具有较高的工程应用价值。

1 信道化接收及重构模型

在实际的宽带接收及重构系统中,输入信号往往为实信号,本文讨论内容为实信号的数字信道化接收及重构模型,框图如图1 所示。实信号经ADC 芯片采样后进入高效数字信道化接收结构,可获得并行基带信号;在基带信号处理中利用接收结构输出的共轭性,只处理其中一半数据,并使用开关组达到通信号阻杂波的效果,提高整体信噪比,经过开关组后的信号直接按共轭性质进行还原,并输入数字信道化重构结构;还原后的并行基带数据先进入高效数字信道化重构结构得到重构信号,最终经DAC 芯片处理变成模拟信号。此模型具有以下优点:一是射频采样的数字信号直接进入信道化模块,省去了传统信道化处理中数字下变频等步骤;二是数字信号处理模块内只处理一半并行基带信号,数字处理部分越复杂,节约的FPGA 资源越多。

图1 实信号数字信道化接收及重构框图

1.1 实信号信道化接收模型

本设计接收部分采用的是文献[5]中的均匀滤波器组信道化结构,具体结构如图2 所示。

图2 均匀多相滤波器组信道化结构

系统设置总信道数为K,抽取倍数为M,x[n]为ADC 芯片采样处理后得到的数字域输入信号,为信道化接收结构最终的并行输出信号。为了使相邻信道不发生混叠,要求满足等式F=K M≥2,在本设计中取F=2,因此有多相分量为:

式中,p=[N/K],N为总数据点数。多项分量El[z2]表示将每个支路的多向滤波器系数需要2 倍插0 值。在F=2 时,用于正交解调的指数乘积项为:

而e-jkπn满足:

最后将IDFT 运算用快速算法IFFT 替换,可得到高效数字信道化接收结构,结构如图3 所示。图3中,到是K路信道化输出,除第0 路和第M路为实数外,其余信道输出均为复数。并且和输出值相同,和(1 ≤l≤K2-1)输出值互为共轭。后续信号处理仅需对一半输出信号进行处理,节省FPGA逻辑资源。

图3 高效数字信道化接收结构

1.2 滤波器组优化

信号重构效果主要取决于接收及重构滤波器组的设计,本文采用正交镜像滤波器代替原型滤波器,接收滤波器组与重构滤波器组参数相同,以此来达到优化重构信号的目的。滤波器组的频谱H(ω)需满足式(4)和式(5)的条件,才能消除重构信号的幅度失真。

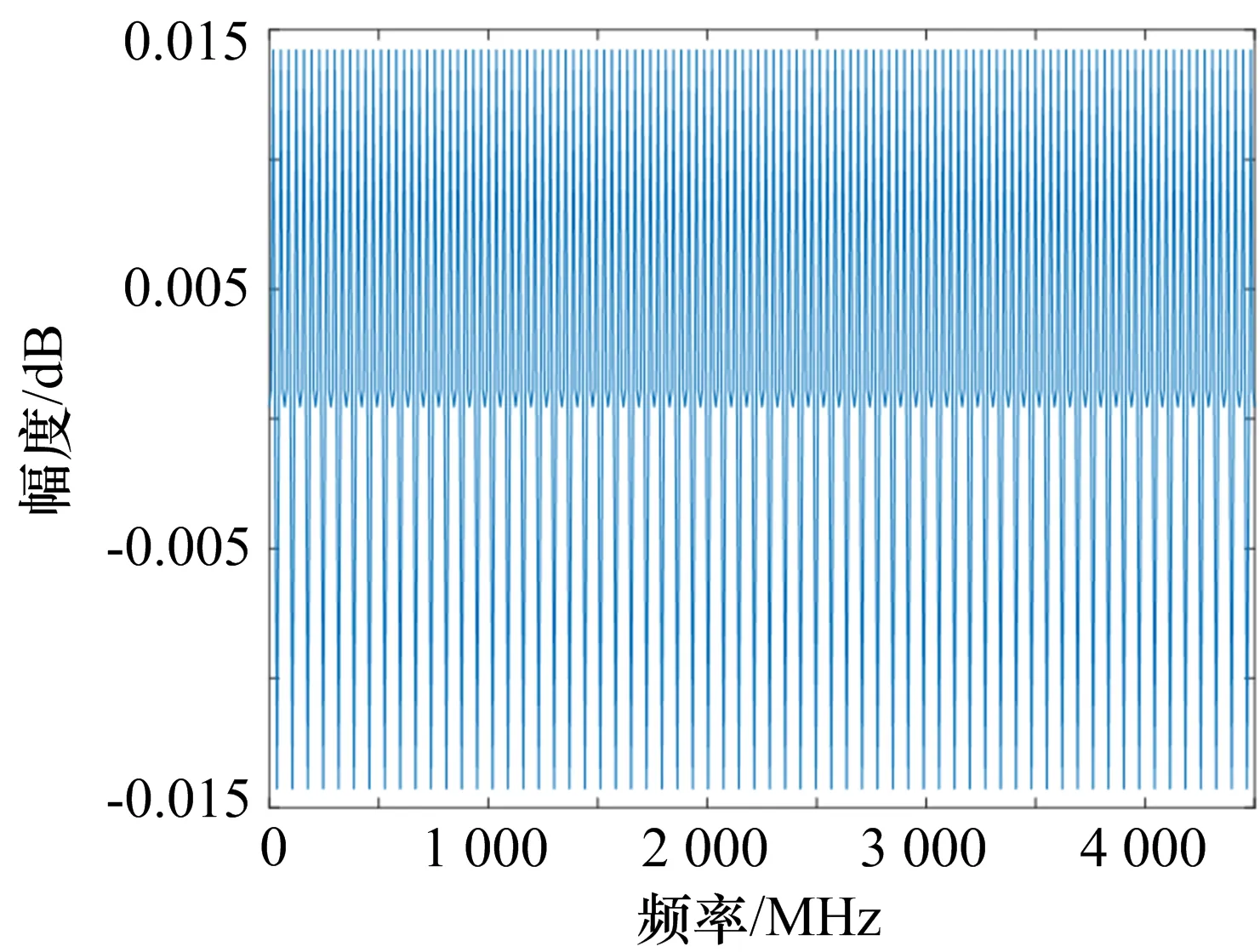

本文正交镜像滤波器组的设计思路参考文献[6-7],通过不断缩小通带频率的选择范围,找到满足式(6)计算误差φ的通带频率,得到最优滤波器组。本文归一化误差φ选取0.004,设计完成的正交镜像滤波器的幅频响应如图4 所示,频带内幅度失真如图5所示。设计的滤波器相关参数为:信道化数128,采样频率9 GHz,通带频率26.367 2 MHz,阻带频率70.312 5 MHz,阶数767,阻带衰减85 dB,最大幅度失真0.015 dB,满足数字信道化接收重构系统要求。

图4 正交镜像滤波器幅频响应

图5 正交镜像滤波器组幅度失真

1.3 实信号信道化重构模型

信道化重构结构与接收结构互为逆结构,在一般的信道化重构结构中,是对输入信号先进行M倍内插,再经过滤波器组及上变频处理。此方法内插在滤波之前,导致待处理数据量多了M倍,且大量数据在处理后将被舍弃。本文采用信道化重构高效结构,如图6 所示,使用与信道化接收结构相同的并行滤波器组,将M倍内插后移,相比一般信道化重构结构,数据的处理量下降到1/M,提高了计算效率,有效节省了实现成本[8]。采用FFT 快速算法代替DFT,提升了信道化重构高效结构的实时处理能力,更利于FPGA 实现。

图6 信道化重构高效结构

仿真参数按照实际硬件环境配置:采样速率为9 GHz,信号量化位数为6 bit;输入信号为单频信号和LFM 信号,其中单频信号频率为1 160 MHz,LFM信号的中心频率为1 020 MHz,带宽80 MHz,处于2信道交界处;信号功率为0 dBm,信噪比为40 dB。输入信号与重构信号的频谱如图7 所示。通过仿真结果可以看出,无论对于单频信号,还是跨信道LFM 信号,利用本文设计的信道化重构结构,都能够实现相应信号的重构,且重构误差较小,与理论分析一致。

图7 数字信道化系统重构信号

2 硬件实现及性能分析

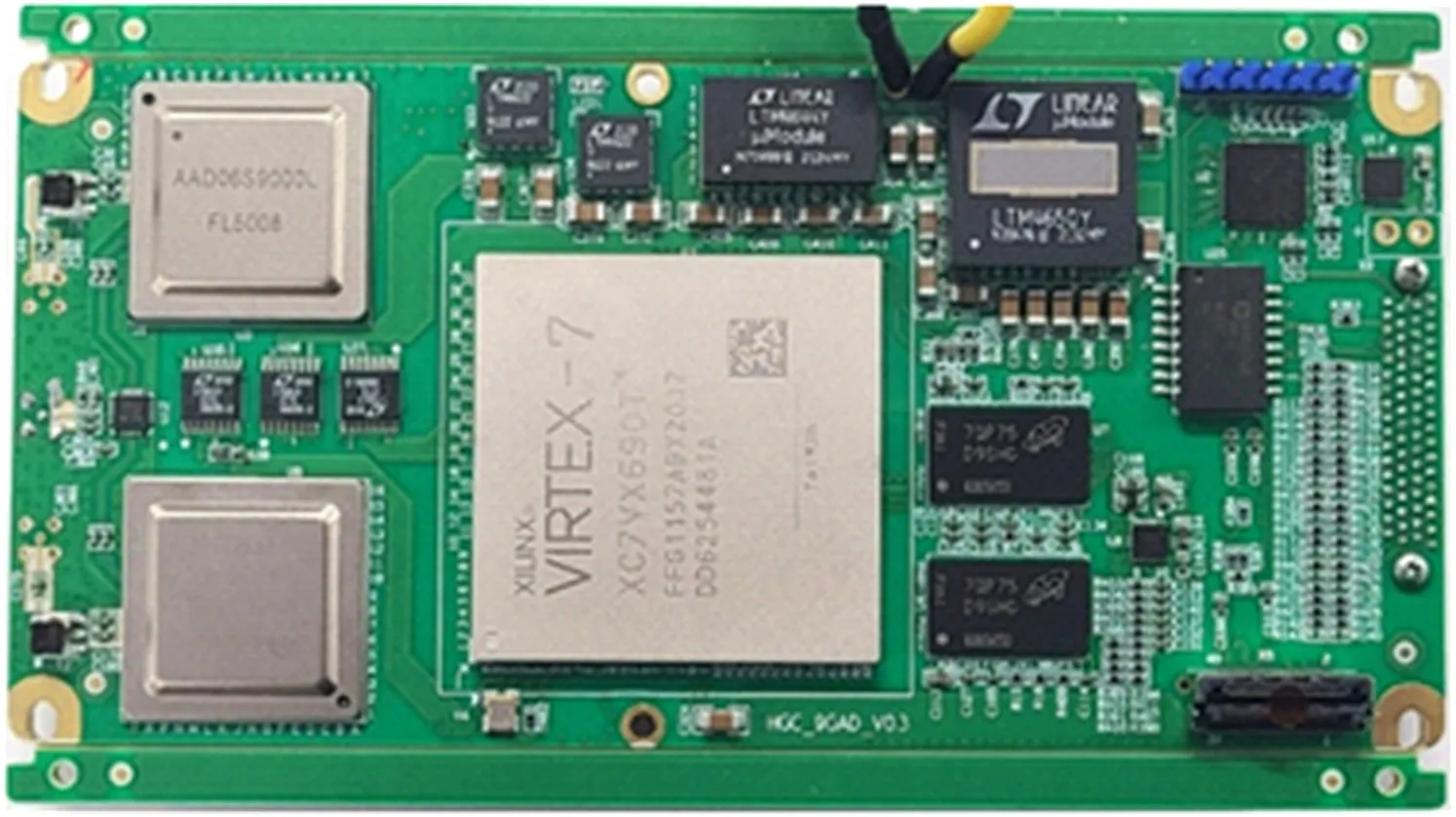

本设计硬件测试平台如图8 所示。其中,高速国产化ADC 和DAC 芯片选用苏州迅芯公司生产的AAD06S9000L 和ADA06S9000L,数据转换速率均为9 GSPS,精度为6 bit,FPGA芯片选用XILINX公司VIRTEX-7系列芯片。程序测试工作均在该平台完成。

图8 硬件测试平台

2.1 FPGA 实现

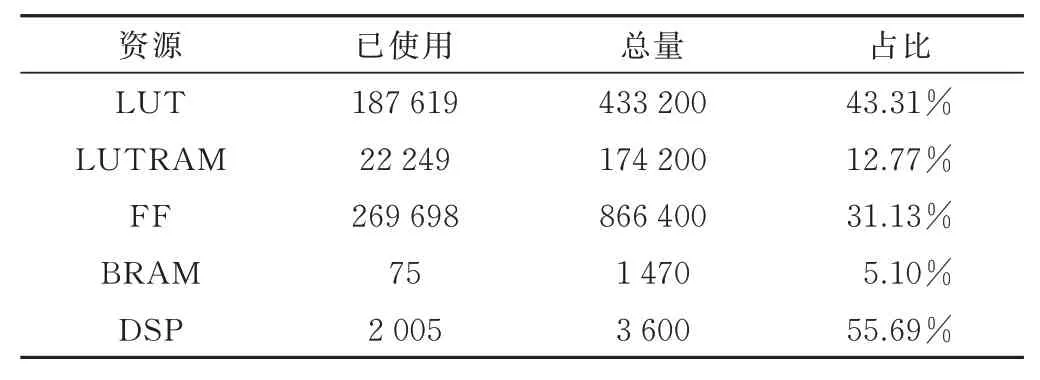

FPGA 实现内容为数字信道化接收、基带信号处理以及数字信道化重构三部分,其中包括并行滤波器组、并行IFFT/FFT、开关组等模块。主控芯片选用Xilinx 公司VIRTEX-7 系列的XC7VX690T-2FFG1927I,设计资源消耗如表1所示。

表1 FPGA 资源消耗图

2.2 硬件测试

硬件测试平台搭建完成后,对国产化高速ADC 和DAC 芯片性能进行了测试。利用信号源产生不同频率的单频信号,经ADC 采集后对数据进行频率分析,同时将ADC 采集数据直通送至DAC 芯片,产生对应的模拟信号,利用频谱分析仪对频谱进行观察。输入频率为1 003 MHz、功率为0 dBm 的单频信号时,ADC采集数据频谱和DAC 产生模拟信号的频谱如图9 所示。经分析确认,采集数据全频带的SFDR 高于30 dB,ENOB 高于4.5 bit,输出中频信号全频带SFDR 高于30 dB,芯片性能达到了设计指标。

图9 ADC/DAC 性能测试图

在数字信道化接收重构系统实测过程中,输入信号为单频信号和LFM 信号,其中LFM 信号功率为2 dBm,单频信号功率为-4 dBm,其余设置与1.3 节仿真信号相同;输入信号经ADC 采集频谱图、输入DAC 前重构信号频谱图如图10 所示;输入信号的频谱图、数字信道化接收重构系统输出频谱图如图11 所示。对比实测结果及仿真结果,实测信道化重构信号与仿真结果基本一致,且无杂散动态范围高于30 dB,与芯片参数相吻合,测试结果良好。

图10 实测ADC 采样及对应重构输出频谱对比图

图11 实测信号源及接收重构系统输出频谱对比图

3 结束语

本文设计并实现了一种大带宽数字信道化接收及重构系统。该系统利用高性能数据采集芯片直接进行射频采样,获得大瞬时带宽的同时优化了传统信道化处理步骤;使用了正交镜像滤波器,实现了信号的精确重构。该系统可实现多雷达信号同时收发,具有较高的工程应用价值。■