浅谈信号完整性之对称的重要性

2023-03-22周敏杰

周敏杰

关键词:信号;完整性;对称性

开发过USB4 连接器的同仁一定会发现个问题,按照TPYEC GEN2 的方式去开发无法线性到10GHz,最后在4 个电源pin 每个增加10 nF 电容才满足信号要求;设计高速PCB 时,差分对旁边的地线断开,那么测试出来的共模信号就会很大;设计连接器的转接板时,如果有一高速信号旁边的地线PIN 不直接接到,那么信号完整性测试就无法通过。

本文基于以上这些情况,逐个讨论,突出高速信号返回地的对称性设计的重要性,给信号完整性工程师以及PCB 设计工程师提供下参考。

1 回流路径(返回地)

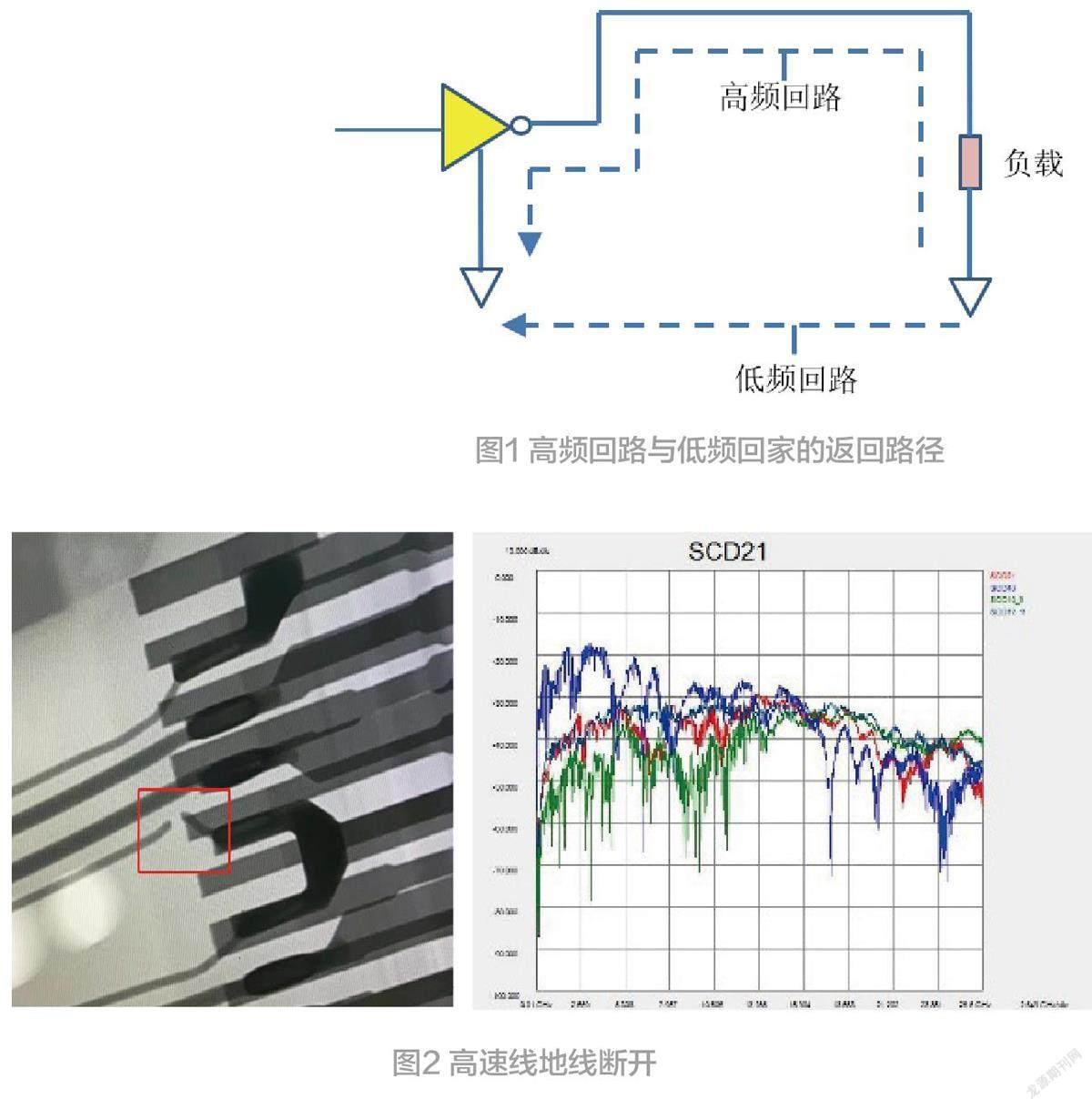

电路信号基本可分两类,低速信号和高速信号,任何信号都会有对应的回流路径,低速信号对应的是低频回路,高速信号对应的是高频回路。这两者的回流路径有巨大的差异,低速信号的低频回路可以沿着实际的连接线返回,而高速信号的高频回路则完全不同,它会沿着的高速信号传输的路径,在附近的平面或者地线形成自己的回流路径,不以实际的连接线返回。[1] 这时候,为了保证信号传输的完整性,就要设计出与回流路径重合的地平面,这里本文将此地平面称为返回地,如图1。

2 PCB一高速差分信号的一侧返回地不连续与连续实测结果对比

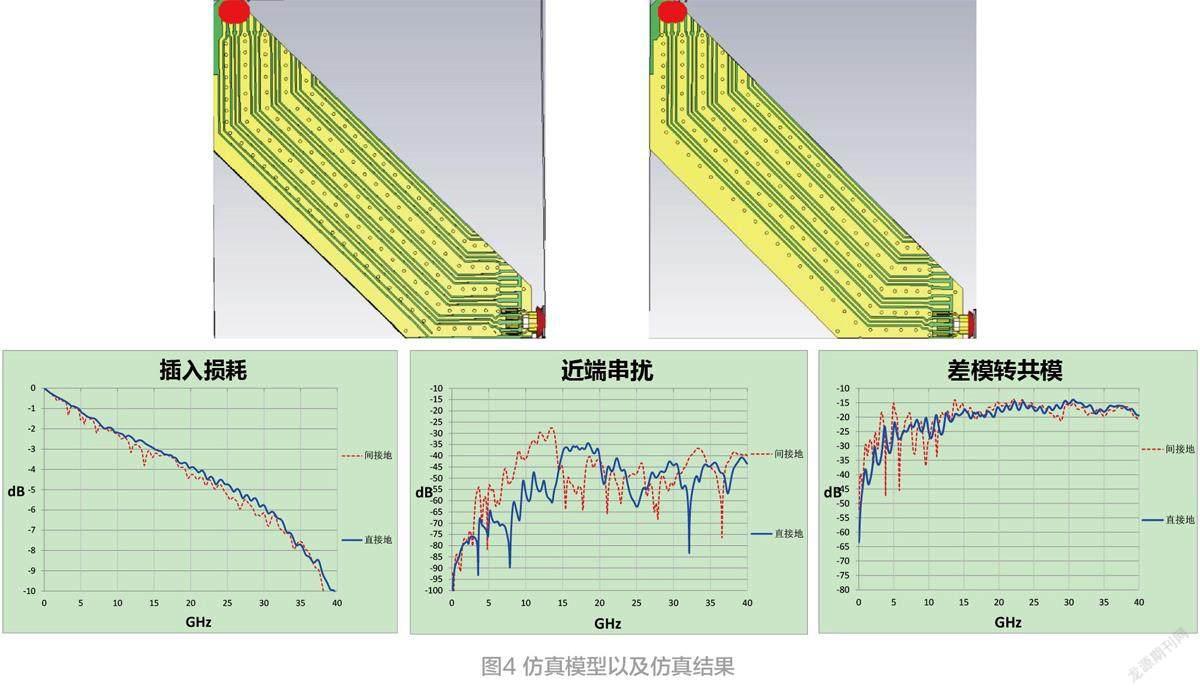

实际项目中碰到一案例,即第一排PCB 最左侧的1对差分线的一侧返回地不直接接地,而是通过焊盘焊接线缆后间接接地,类似跳线做法接地(如图3 所示),与之对照的下方PCB 的最左侧的那对差分线,则是做成两侧对称的设计,两个PCB 焊接同样的高速线缆,对配同样的板端连接器,结果发现返回地不对称设计的高速线缆近端串扰发生异常,在频率10 GHz 以内有明显的多个凸起的干扰信号出现,对比下面对称设计的线缆,整个频段无异常杂信出现;且除了近端串扰差异大,差模转共模信号差异也特别大,在高频回路中,共模信号属干扰信号,作为设计者,要尽可能的阻止共模信号过大,差模转共模更是要抑制住。[2-3] 从实际的测试结果中,可发现返回地的不对称设计是造成共模信号的来源之一,而对称性的返回地设计刚好是解决差模转共模的有效方法。

总结对比结果,不对称性返回地的设计会导致串扰大,共模抑制差,设计中返回地的设计要尽可能做到左右对称,切记不可为了兼容低频信号而放弃对称原则,这将会给高速链路带来极大的坏的影响,甚至可能就因此无法通过系统测试。

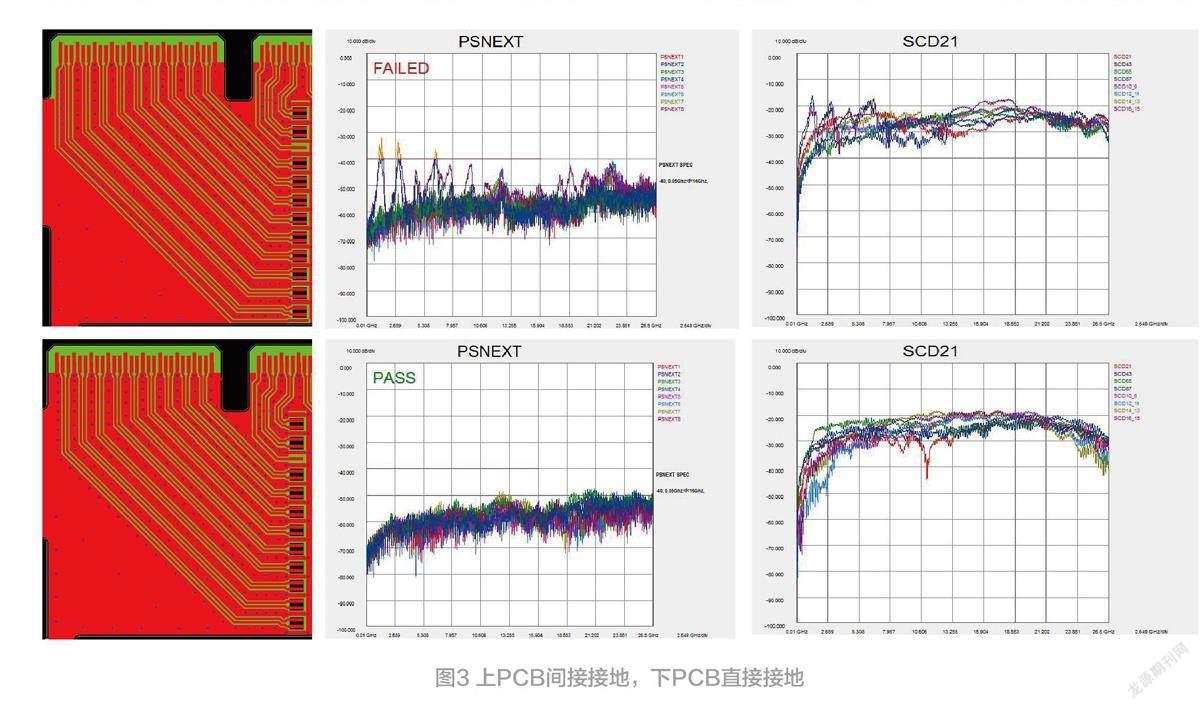

3 高速线缆返回地线断开

现特意找到某案例(如图2 所示),在焊接制作中,将一侧的地线断掉,从低频视角来看,地线虽然断开,但是可通过PCB 的过孔,高速线缆的铝箔可以将该地线间接连接起来,所以用万用表或者开短路测试仪器都是无法测试出开路情况的;然而从高频视角来看,这差异就大了,高速回流信号走到断线的地方无法通过时,就会通过绕路或者辐射来形成新的回流路径,这样差分对的一根信号线有顺畅的回路,而另一根信号线却没有,不对称凸显,共模噪声产生。从实测结果也可以看到,返回地断开,差模转共模噪声会明显高于其他正常信号。这一结果,进一步佐证返回地对称性设计的重要,万万不可以低频信号回路的视角来判定高频信号回路。

4 仿真验证

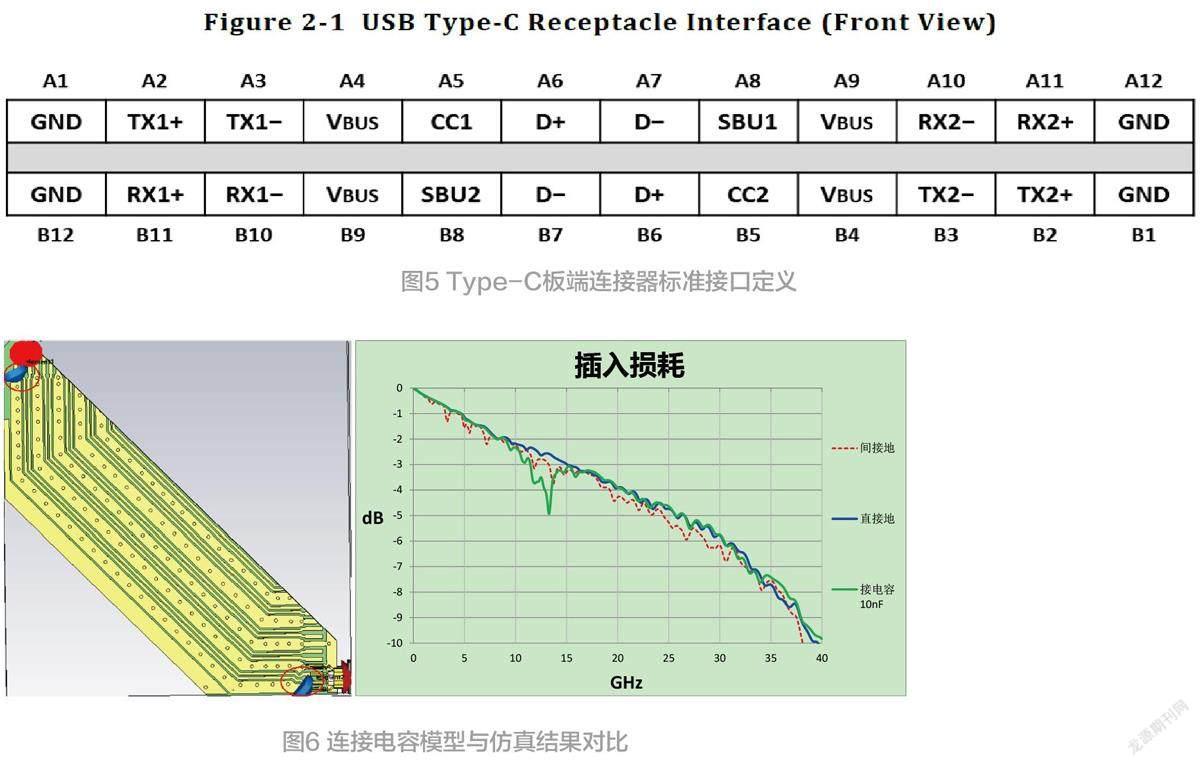

为了验证理论上的可行性,特意建了两个PCB 模型进行模拟仿真,左侧PCB 最边上的地线不直接接地,二是通过末端高速线缆的铝箔来达成接地,而右边则是做成对称性设计,直接接地。为了同时验证插入损耗、近端串扰、差模转共模,特设置8 个端口,选择PCB上下对应的两组差分线对。其他诸如仿真的网格数、PCB 材质、导体特征、端口类型等都设置成一样。如图4 所示,(左)间接地,(右)直接地。仿真频率宽度设置成40 GHz,这里将红色虚线结果来表达左侧模型间接地的仿真结果,将蓝色实线结果来表达右侧模型直接地的仿真结果。

先来看插入损耗的仿真结果对比,任何高速链路,插入损耗都是最重要的参数之一,从频域上看,插入损耗线越小,越平滑,整个链路的性能就会越好,仿真结果显示具体有对称性返回地设计的模型插入损耗要小,且波动小,而间接地的那个模型则明显有掉沟,波动较大。

再看近端串扰的性能,差异也很明显,间接地的模型在(0~15)GHz 频段明显高于直接地的模型,从结果来看间接地的设计只能满足PCIE GEN3 性能,而直接地的设计可满足PCIE GEN5 的要求。差别甚大。

最后来看差模转共模,这是一个噪声信号,越小越好,仿真结果显示,间接地的模型,差模转共模明显比直接地模型大,跟实测结果对比,仿真结果与实测非常吻合。这进一步证实,返回地的不对称性设计是造成共模噪声的一大因素。

引言中有提到USB4 的连接器信号处理方式,即用四颗10 nF 的电容来缓解信号完整性问题。要讲清楚这个,我们必须得了解Type-C 连接器的pin 定义如图5 所示,高速信号对旁边看起来不对称,一侧是GND 一侧是VBUS,按照上面的仿真结果和实测数据,TYPE-C 连接器的信号完整性肯定有问题,满足不了规范要求,如果要满足,那就的想办法做成对称设计,怎样将一侧电源一侧地完美地平衡呢?这时候电容的作用就体现出来了,它可以将高频回流信号通过电容,借电源平面完成回流,这样的处理,也从另一层面实现了返回地的对称性。这里同样也安排了此种情况下的仿真,即基于图4 左边那个不对称的模型,增加10 nF 电容,进行仿真,结果显示高速信号虽然比直接接地的情况要差点,但谐振点已经拉到10 GHz 以外了,而10 GHz以内的信号平稳、波动小,已经满足规范要求了,如图6 所示。

5 结束语

本文通过案例的方式,在信号完整性性能方面,将返回地不对称与返回地对称进行对比,最明显的差异就是近端串扰和差模转共模的噪声大;再通过模擬仿真的方式,将这两种模型进行对比,同时观察插入损耗、近端串扰和差模转共模,仿真的结果与实测一致。这给我们在高速链路设计中,要以对称性为原则,让返回地尽可能设计成直接地的情况,如果实在条件不允许,则可以考虑添加合适的电容来解决跨层问题,缓解非对称问题。本文结论可给信号完整性工程师以及PCB 设计工程师对高速信号线的处理方式提供1 个设计上的参考,不要以常规电路的方式来看来高速电路,要以高频回路的理念来处理高速链路可能存在的风险,如本文介绍的返回地线断开或者不直接接地,用万用表去量测,他们都是导通的,但涉及到高频回路,回流路径就完全不一样了,从而产生出信号完整性方面的一系列问题。总之,高速电路要讲究对称,特别是返回地的处理。