弹地高速传输系统优化设计

2023-03-14赵冬青袁小康

赵冬青,辛 艳,袁小康

(中北大学 电子测量技术国家重点实验室,山西 太原 030051)

0 引 言

随着技术的逐渐发展,对弹地设备的传输距离和传输数据的可靠性逐渐有更高的要求。因此,大量学者对于弹上数据的采集、传输、存储进行研究,文献[1]中对弹上图像数据的采集通道进行优化;文献[2]设计的模∕数混合采集系统是为了满足弹上的采集模拟量和图像数字量的需求。本文设计一种弹地高速传输系统,对采编存储器和测控台之间的硬件传输链路和软件逻辑层进行优化设计。在硬件电路中,根据不同指令选用不同传输链路,提高物理层的传输性能;在软件方面,运用FPGA平台对数据进行处理。FPGA相比传统的单片机对数据的处理速度更快,适应于长距离数据传输的设计。

1 系统总体设计

地面设备(包括测试台)与采编存储器通过RS 422链路和LVDS链路实现指令发送、状态监测和数据下载的功能。采编存储器采集模拟量信号、语音数据、图像数据,将采集的数据编帧后存入存储器,上位机软件将测控台回读的数据进行处理和分析。测控台和采编存储器板卡之间通过双绞线电缆和配套连接器连接[3]。为实现数据的高速传输,其中地面设备使用RS 422链路向采编器发送指令,采编存储器通过LVDS高速数据接口[4]进行事后下载。弹地高速传输系统总体设计图如图1所示。

图1 弹地高速传输系统总体设计图

2 硬件电路设计

2.1 链路信号衰减分析

传输链路产生的噪声通常以电容耦合、电感耦合的形式对信号产生影响,使接收端接收的信号波形出现毛刺或波形混乱,无法识别正确信号。双绞线电缆的使用可有效抑制共模干扰[5],并且其扭转结构可以使磁场环境中的互感相互抵消,清除感应耦合的影响。信号在信道上传输会产生多种损耗,如插入损耗、反射损耗等。信号衰减的程度不仅与传输速率的大小有关,还与传输距离有关,随着传输距离增加,损耗越严重;随着传输频率的增加,高频分量的损耗增大[6]。本文在电路中增加均衡器、驱动器来提高信号质量,减少信号衰减,增强信道传输能力;并在芯片周围添加匹配电阻和匹配电容削弱信号反射造成的干扰。

2.2 链路传输优化

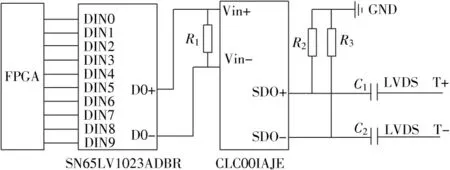

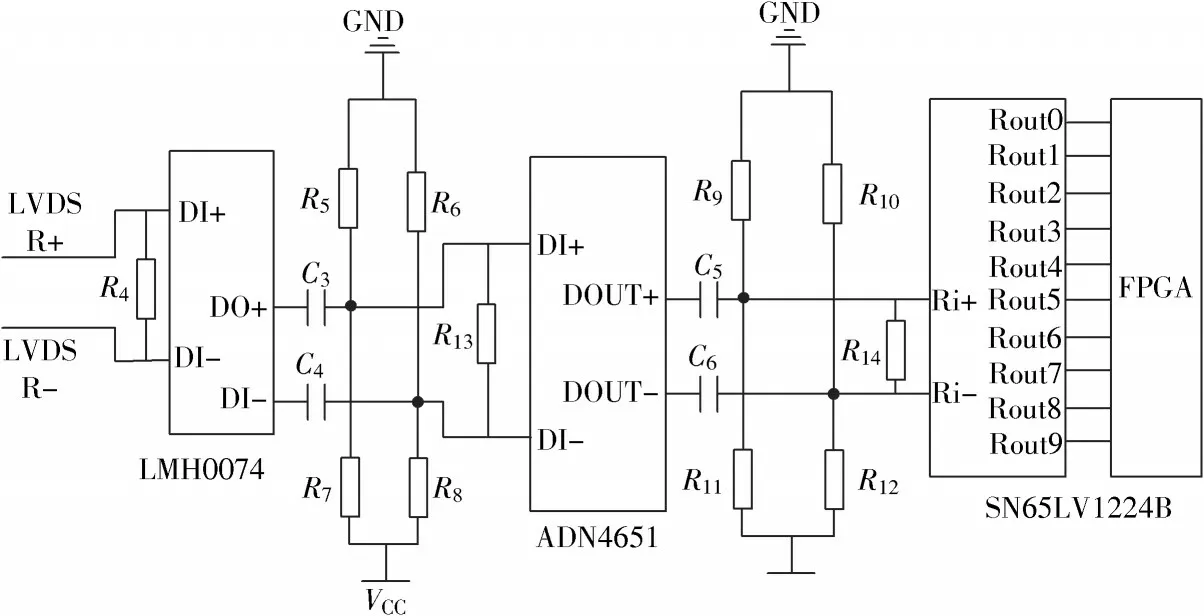

LVDS链路传输选择TI公司的高速差分数据流串化器SN65LV1023ADBR芯片和解化器SN65LV1224BDBR芯片。发送端数据在FPGA的作用下,通过串化器将并行数据转化成串行码。由于SN65LV1023芯片的输出信号压差很小,仅有200 mV,无法满足弹地之间的长距离传输要求,因此在发送端进行预加重处理,添加一个电缆串行驱动器CLC001芯片,该芯片通过时域加重处理增大信号的发送幅度,延长发送距离。接收端将串行数据转换为并行数据并发送至FPGA[7]。由于传输链路为双绞线,虽然可以抵消部分耦合,但随着传输速率增加,传输距离延长,传输线引起的损耗依旧存在。在接收端加入自适应均衡器LMH0074芯片,它可自动均衡不同长度的双绞线,补偿传输频率为125~540 Mb∕s的信号在传输线上的衰减。在驱动器芯片和接收器芯片之间加入一个LVDS隔离器ADN4651芯片,对驱动器和解化器进行电流隔离,实现LVDS弹地传输链路的直接隔离。LVDS发送端和接收端电路图如图2、图3所示。

图2 LVDS发送端电路图

图3 LVDS接收端电路图

本文在链路设计中不仅使用预加重、均衡技术缓解信号的衰减,还通过阻抗匹配的方式[8]将传输链路中产生的反射干扰的影响降低。发送端电阻R1为100Ω,作为终端匹配电阻匹配双绞线的阻抗,有效地避免在传输过程中引起的反射;其并联在串化器的D0+、D0-引脚上,使得输出的差分电压信号值在CLC001芯片的接收范围内。接收端在均衡器和隔离器接收数据之前添加较大容值的隔直电容C3,C4,C5,C6,用来减少损耗。R4,R13,R14的作用同R1类似,作为源端匹配电阻。

3 软件逻辑设计

本文软件逻辑设计图如图4所示,通过乒乓缓存模式替代单流水线结构,提高传输速率[9]。为了保证链路长线传输时的可靠性,在乒乓缓存的基础上,添加8 B∕10 B编码技术,使已优化的数据降低链路上的码间干扰[10],使得数据中的1和0数量均衡[11],从而保持电流平衡。另外,通过RS 422指令识别是发送数据指令还是数据重传指令。

图4 软件总体设计图

3.1 LVDS接口协议优化

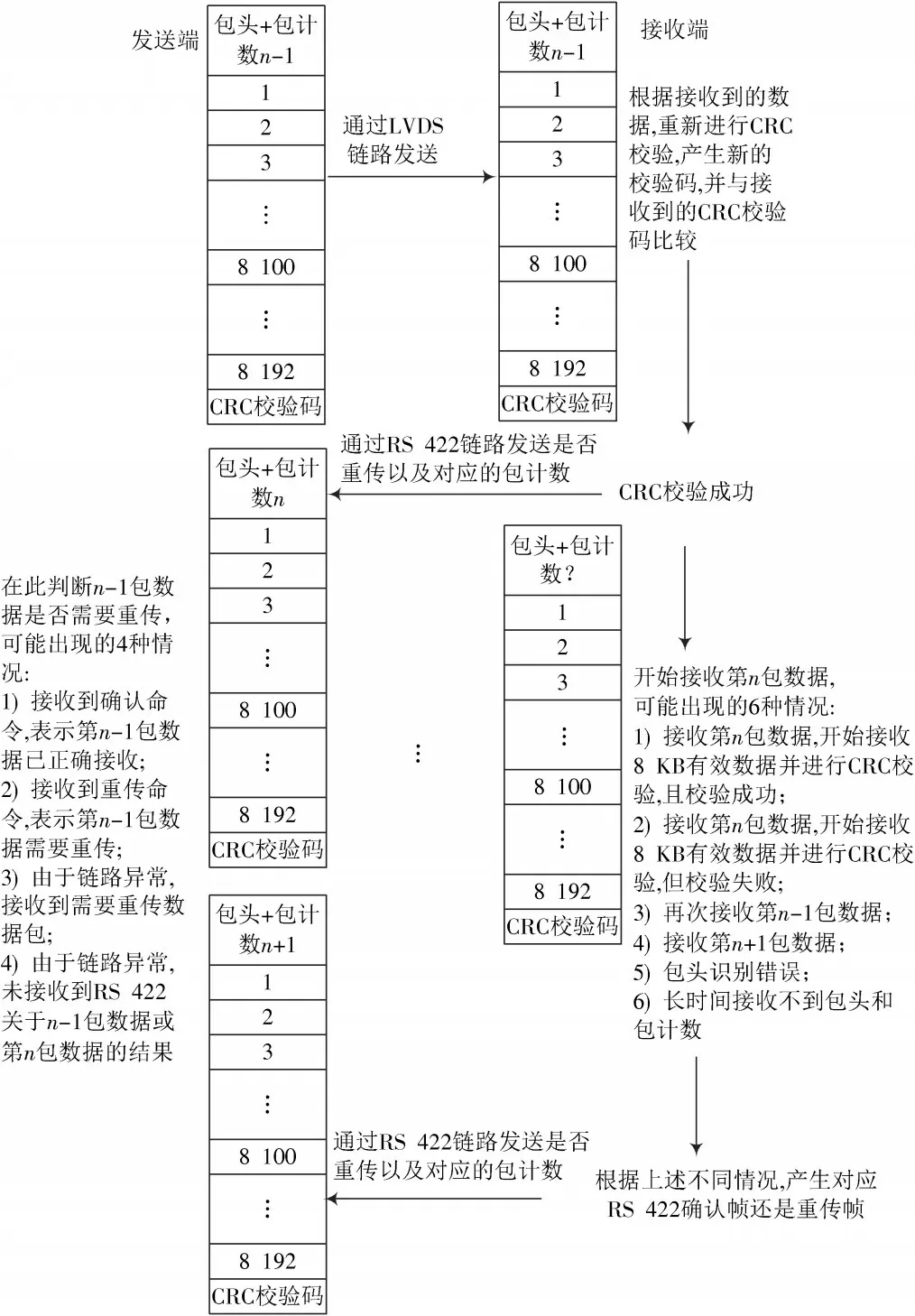

采编存储器的原始数据进入FPGA之后,在FPGA内部添加4 B包头并对8 192 B数据进行CRC运算,将运算结果的校验字续写在数据后面[12],形成一个新的8 200 B的数据包,打包的格式为0x5A54+包计数(0x00~0xFF)+帧类型(重传帧为0x00,非重传帧为0x01)+8 192 B有效数据+4 B CRC校验值,如图5所示。采编存储器通过优化后的LVDS链路将数据发送给测控台。当测控台接收到数据解码后会重新计算8 192 B数据的校验字,将计算结果和接收的校验字进行对比[13],如果对比结果一致,表明数据接收正确;否则接收错误并丢弃数据[14],随后通过RS 422接口发送包含有重传包计数的重传指令,连续发送3条。

图5 收发协议示意图

3.2 数据传输优化过程

采编控制器将准备好的第n-1包数据发送至测控台,随后发送第n包数据,当发送完第n包数据的8 100个字节后,检测第n-1包数据是否发送成功的标志。当识别到重传指令,且包计数为n-1,则停止发送第n包数据,重新发送第n-1包数据;当识别到确认指令,且包计数为n-1,则继续发送第n包数据。随后再发送第n+1包数据,当检测到为确认指令,包计数为n-2,则停止发送第n包数据,重新发送第n-1包数据;当检测到为重传指令,包计数为n,则停止发送当前数据,从当前数据包n的第0个数据开始重新发送当前数据包至测控台。

接收端每接收一包数据时,先识别数据包头和包计数,假设当前应该接收包数据为n,若包头正确,包计数为n-1,则向采编控制器发送n-1包数据的确认指令,之后重新检测数据包头;若包头正确,包计数为n+1,则向采编控制器发送n包的重传指令;若包头正确,同时包计数为n则接收数据,并进行CRC数据校验;若包头错误,则向采编控制器发送n包的重传指令;若包头长时间未接收到,则向采编器发送n包数据的重传指令,并重新开始接收数据。数据传输会出现7种情况,如图6所示。

图6 优化后数据包传输示意图

在采编控制器和测控台之间添加了握手机制,通过包计数的识别减少传输中丢包现象的发生,通过重传次数判断传输链路的好坏。

3.3 重传时间

当测控台发送重传指令时,采编存储器最快获取指令的时间为60/ 62 500=96μs,最慢获取指令的数据为(60+70+60+70+60)/625 000=512μs。此时采编存储器发送第2帧数据到7 680 B(根据时间512μs,速度15 MB∕s计算),采编存储器发送完第2帧数据,即可响应第1帧数据的重传。采编存储器采用DDR3大小为256 MB,此时DDR3缓存未溢出,第1帧数据还在,可以响应重传数据。

4 试验验证及分析

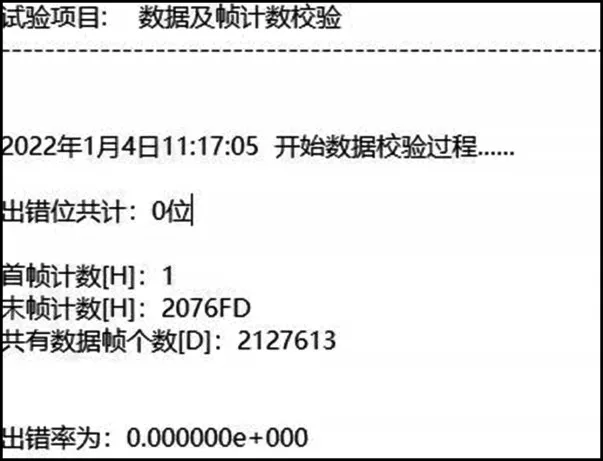

利用采编存储器、地面测试台和上位机软件搭建系统,对数据传输的可靠性进行测试。上位机的校验结果分析包括传输的误码个数和误码率[15]。连接好设备,采编存储器将数据发送给测控台,测控台接收正确数据,缓存到DDR3中;当DDR3缓存到一定数据时,将数据通过总线发送给上位机,上位机软件将数据写入硬盘[16]。当收到下载停止指令结束接收数据,点击数据解析,上位机软件就可提取出有效数据,并生成分析结果。测试时采用的有效数据是递增数据,方便解析时判断数据是否误码和丢帧。

测试试验验证结果如图7、图8所示,可以直观地看出传输数据的帧计数一直连续没有丢帧现象的出现。CRC校验结果可以看出,校验出错位为0位,出错率为0,数据传输正确。表明在软件逻辑中增加CRC校验重传机制虽然增加了一定的传输带宽,但是降低了误码率,保证了传输的可靠性。

图7 递增数据

图8 校验分析报告

5 结 论

本文系统将软件和硬件共同优化,通过硬件传输链路优化弥补信号传输距离短的短板,通过预加重和均衡技术缓解信号链路的衰减和干扰,为数据延长距离传输提供一个相对稳定的环境。经过CRC校验和反馈重传机制可以及时地发现有效数据在传输中出现的误码,并在有错时及时重传,提高传输数据的正确率。通过实验验证测试台下载数据并通过上位机软件进行结果分析,得出本文设计的弹地系统误码率为0,可实现数据的可靠传输。