Rapid IO交换芯片的静态时序约束设计

2023-02-19沈剑良李沛杰

张 丽,沈剑良,李沛杰

(中国人民解放军战略支援部队信息工程大学 信息技术研究所,河南 郑州 450002)

0 引 言

随着片上系统的发展,出现了数千万门级的ASIC电路,针对如此大规模的电路,有效准确的验证变得尤为重要。功能验证和时序验证是保证芯片功能符合设计需求的重要手段。20世纪90年代中期,静态时序分析(Static Timing Analysis,STA)的概念被提出,其通过分析电路拓扑来静态计算电路中不同信号的时间,以判断是否满足时序要求[1-4]。静态时序分析依赖于时序约束文件,好的时序约束设计可以正确体现芯片的设计需求,最终实现芯片的正常通信功能。

RapidIO互连技术是一种高性能、低引脚数、基于报文交换的互连体系结构,是唯一的嵌入式系统互连的国际标准[5-7]。2009年发布的RapidIO 2.1规范中,单通道最高速率支持到6.25 Gbaud,端口支持1x、2x、4x通道绑定;2014年发布RapidIO 3.1规范,单通道最高速率[8]支持到10.312 5 Gbaud;2016年发布RapidIO 4.0规范,单通道最高速率[9]支持到25.781 25 Gbaud。随着RapidIO互连技术的发展,单通道支持的速率越来越高,意味着高速通道的正常通信在RapidIO交换芯片设计中需要重点关注。RapidIO交换芯片作为嵌入式RapidIO设备的核心芯片,其时序验证的准确性直接影响芯片的PVT(Production Verification Test)一致性及高速信号传输的可靠性。

针对异步时钟域设计中的CDC(Clock Domain Crossing)信号,文献[10]提出了一种CDC信号滑动窗口时序分析方法;文献[11]在导航基带芯片中设计了多异步时钟域的时序约束方法;文献[12]针对数字电路中提高工作频率的方法,介绍了通过消耗逻辑资源提高工作频率的设计思路。32通道RapidIO交换芯片是一款满足RapidIO v2.1协议的、低延迟、高带宽的交换芯片,具有高速通道的高速时钟频率特征,存在多时钟域、多通道绑定下的时钟同步,及较多的跨异步时钟处理的特点和问题。对此,本文提出并设计了一种多分组全芯片的时序约束设计,优化解决了静态时序分析中的时序违例,最终满足芯片在全PVT下的时序要求。

1 概念及基本原理

1.1 静态时序分析

静态时序分析的工作原理是通过套用特定的时序模型,针对特定电路分析其是否违反设计者给定的时序约束。其中,时序模型依赖于特定工艺中的标准组件库;时序约束由设计者给定,正确反映电路设计的时序需求。静态时序分析策略包括基于模块的方式和基于路径的方式。基于路径的时序分析方式[13]以路径为单位,找出电路设计中所有的时序路径,按照特定模型精确地计算每条时序路径的延迟信息,以判断是否满足时序要求。每一条时序路径都存在一个始发点和一个终止点[1,14]。始发点分为两种:组合逻辑单元的数据输入端口和时序单元的时钟输入端口。终止点也分为两种:组合逻辑单元的数据输出端口和时序单元的数据输入端口。根据始发点和终止点的不同可分为4种类型的时序路径:

1)触发器到触发器;

2)触发器到输出端;

3)输入端到触发器;

4)输入端到输出端。对时序路径的建立时间(Setup time)和保持时间(Hold time)进行分析是静态时序分析的主要工作。

1.2 时序约束

时序约束由设计者结合芯片结构及需求分析要求给出准确的定义。时序约束通常以SDC(Synopsys Design Constraints)格式来描述电路的时序、面积等信息。时序约束设计属于芯片功能的一个重要组成部分,包括时钟约束、I/O的输入输出约束等。时钟是最重要的一项时序约束,时钟特性包括波形、延迟、时钟不确定性。其中,网络延迟和时钟不确定性在布局布线前可用来预估时钟信号的延迟时间,在布局布线后,则要根据实际的寄生电阻电容计算得到。

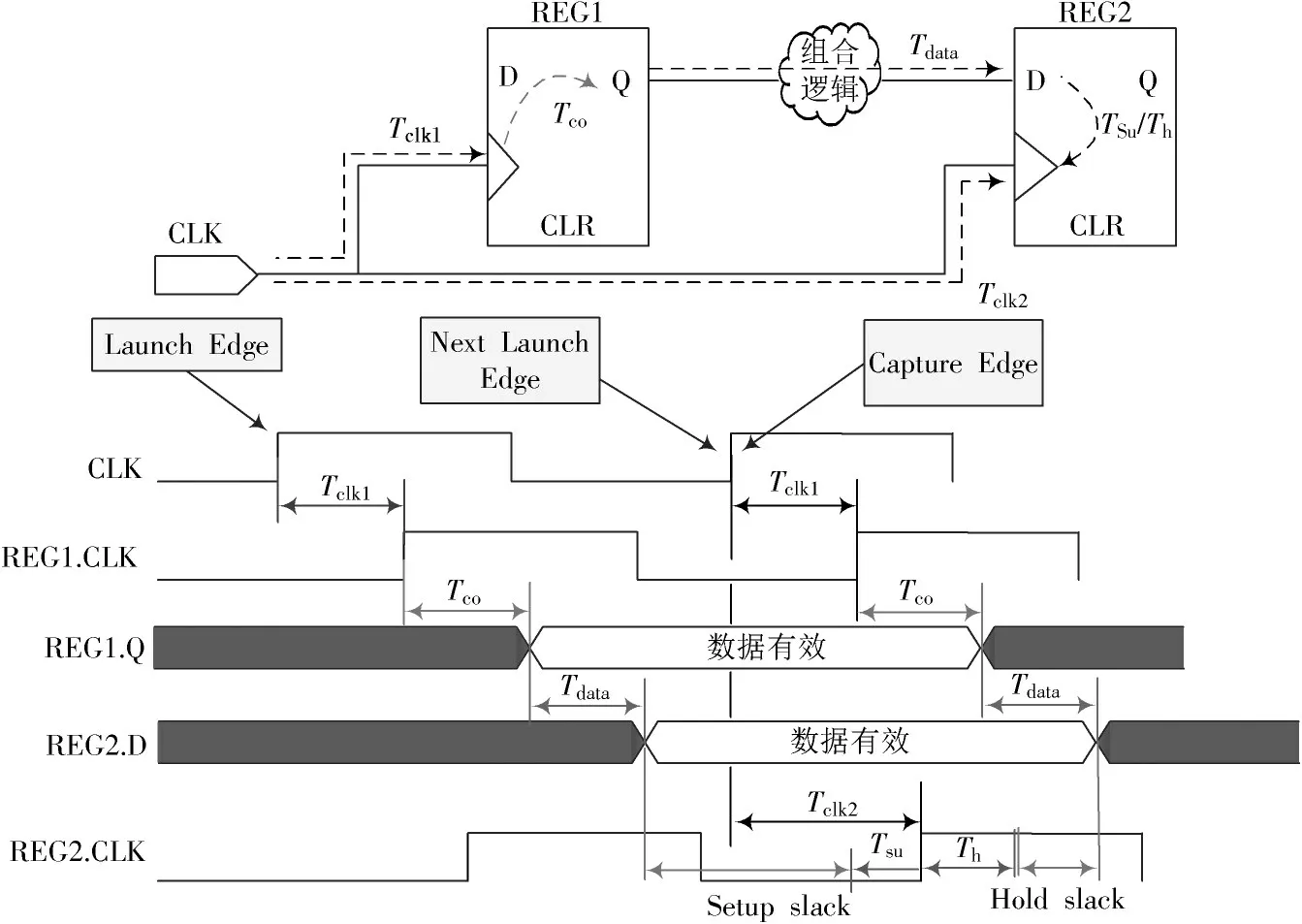

在此以触发器到触发器的时序路径为例介绍静态时序分析原理,如图1所示。

图1 Setup time/Hold time时序分析

Setup check,数据到达REG2的D端的时间,计算公式如下:

式中:Tco为REG1时钟端到Q端的延迟;Tdata为REG1的Q端到REG2的D端间组合逻辑的延迟。时钟到达REG2的时间计算公式为:

数据被锁存在REG2需要的最小时间计算公式为:

若在REG2正确捕获到从REG1发出的数据,则需Data Arrival Time<Data Required Time,两者差值称为Setup slack。slack为正值表示时序满足,否则发生时序违例。

Hold check要求当前数据不会被下一个数据所覆盖,Data Arrival Time为下一个数据到达REG2的D端的时间,如式(4)所示;数据被锁存在REG2需要的最小时间,如式(5)所示;Hold slack由下一个数据的到达时间减去当前数据的捕获时间,计算公式如式(6)所示。

因此时序分析时,既要利用时序模型的信息,如单元延迟Tsu,Thold等,又要利用时序约束信息如时钟周期信息等,最终计算路径的延迟信息,以判断是否满足时序要求。

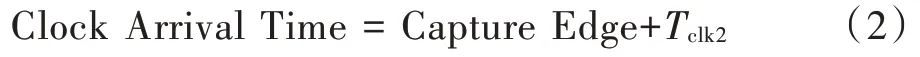

2 Rapid IO交换芯片时序分析

32通道RapidIO交换芯片主要由32个高速通道、14个端口、全交叉核心交换、I2C接口等组成。对外通道主要是32个高速通道,以及I2C接口、JTAG接口;时钟主要涉及交换时钟、端口时钟、Serdes时钟、配置时钟及JTAG、I2C模块时钟。该交换芯片支持一路参考时钟输入,即REF_CLKP/N时钟管脚为参考时钟源;有一个独立于Serdes的核PLL,是芯片核心时钟源;在12个PMA的发送/接收端反馈时钟在Serdes模拟部分进行门控时钟设计;支持从PMA到SRIO的时钟映射功能;JTAG时钟作为接口随路时钟。具体的时钟信息如图2、表1、表2所示。

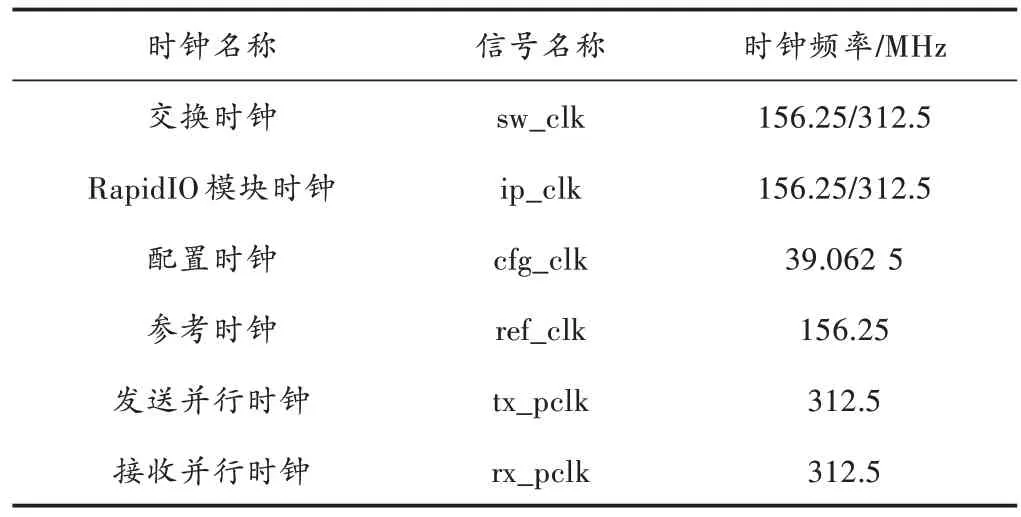

表2 内部时钟信息

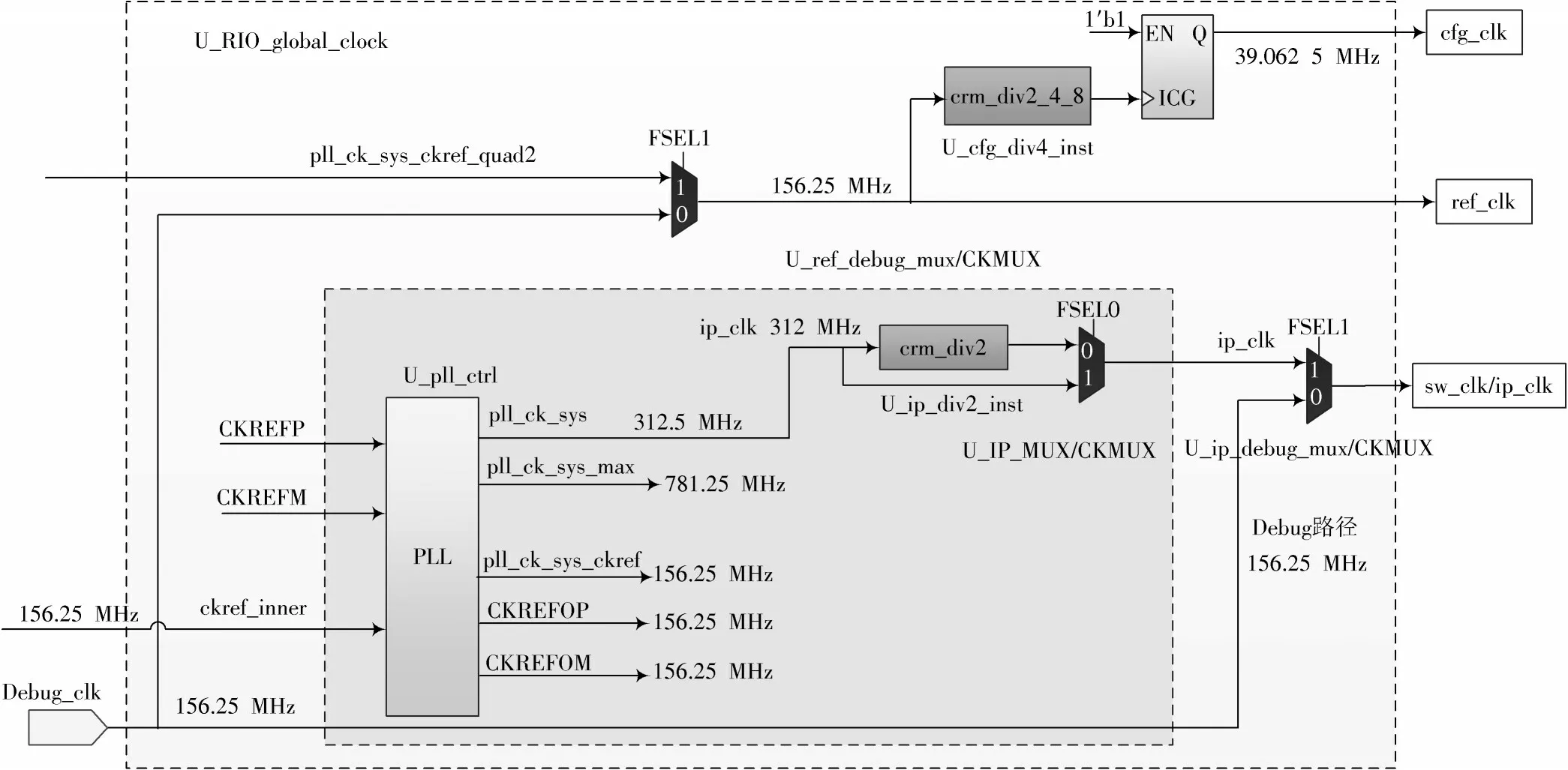

图2 Rapid IO交换芯片PLL时钟结构图

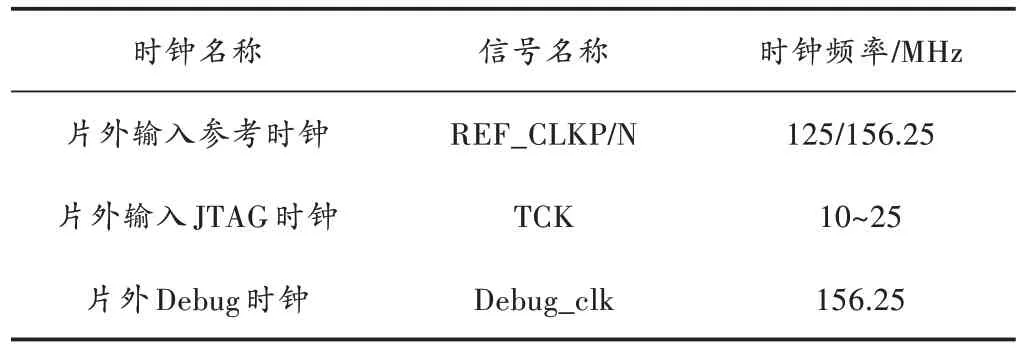

表1 片外输入时钟信息

片外输入时钟由晶振产生的1组差分时钟提供,在板级解决了12个Serdes级联问题。芯片内部包含13个PLL。12个Serdes的时钟模块各包含1个PLL,核时钟处理包含1个PLL。核时钟PLL经倍频分频处理输出一个312.5 MHz的单端时钟pll_ck_sys,该时钟经2分频产生156.25 MHz时钟,后根据外部管脚FSEL0的配置,产生交换模块所采用的功能时钟sw_clk及12个RapidIO控制器采用的功能时钟ip_clk;全芯片配置网络采用的配置时钟cfg_clk为差分转单端后的单端时钟的4分频时钟。

由以上分析可知,32通道RapidIO交换芯片在时序方面具有如下特点:

1)多时钟域划分。由表1、表2可以看出,该交换芯片存在如主时钟sw_clk、高速Serdes的发送和接收时钟、配置时钟cfg_clk等较多的时钟域划分。

2)高速时钟频率需求。主时钟sw_clk和Serdes时钟需要满足312.5 MHz的高速频率需求,参考时钟ref_clk需要满足156.25 MHz的高速频率需求。

3)Nx模式下N个lane的时钟必须为同一速率。对于PMA的收发时钟在不同模式下其频率输出需进行路径切换,且保证Nx模式下N个lane的时钟必须为同一速率,如4x模式下其4个lane的时钟必须为同一速率。需考虑Nx模式下的时钟同步问题。

4)较多的跨异步时钟。由于存在多时钟域,不同的时钟域之间的数据交互需考虑跨异步处理问题。

3 Rapid IO交换芯片时序约束设计

3.1 时序约束设计

3.1.1 时钟约束的设计

1)时钟和生成时钟定义

芯片的片外输入时钟(见表1)的SDC指令为create_clock[1-3],对REF_CLKP/N等时钟分别定义,包含其时钟周期、时钟源、时钟名称、占空比等。

create_clock-name REF_CLKP-period 6.4[get_ports REF_CLKP]

create_clock-name REF_CLKN-period 6.4[get_ports REF_CLKN]

create_clock-name TCK-period 40[get_ports TCK]

create_clock-name Debug_clk-period 6.4[get_ports Debug_clk]

以上时钟定义其时钟源点直接来自于时钟端口。逻辑综合阶段根据负载模型的类型进行过约以留有余量,方便后端物理实现。通常针对ZERO RC采取将时钟周期过约30%的方法实现余量。

内部时钟由时钟PLL倍频分频产生,需要对PLL的输出时钟进行定义,如下:

create_clock-name PLL_sys_clk-period 3.2[get_pins PLL/pll_ck_sys]

PLL输出时钟pll_ck_sys经过2分频产生156.25 MHz时钟,后经过选择器输出到交换模块和端口模块,根据不同的工作模式选择不同的时钟,定义如下:

create_generated_clock-name GCK_ip_div2[get_pins U_ip_div2_inst/div2_ff_reg/Q]-edges{1 3 5}-master PLL_sys_clk-source[get_pins PLL/pll_ck_sys]

create_generated_clock-name GCK_ip156[get_pins U_IP_MUX/CKMUX2/Z]-edges{1 2 3}-master GCK_ip_div2-source[get_pins U_ip_div2_inst/div2_ff_reg/Q]-add

create_generated_clock -name GCK_ip312 [get_pins U_IP_MUX/CKMUX2/Z]-edges{1 2 3}-master PLL_sys_clk-source[get_pins PLL/pll_ck_sys]-add-combinational

GCK_ip_div2为核时钟经2分频后的时钟。GCK_ip156和GCK_ip312对应选择器CKMUX后的输出时钟,以上时钟定义点均为逻辑单元的pin脚。由于GCK_ip312时钟从其源引脚到生成时钟的路径不仅有纯组合电路(pll_ck_sysàCKMUX),同时存在时序电路(pll_ck_sysàcrm_div2àCKMUX),因 此 在 定 义GCK_ip312时钟时必须加上-combinational选项,以阻隔时序电路,让组合电路始终有效;否则GCK_ip312时钟定义会失效,引起异常时序路径。

Serdes模块的PLL的输出时钟tx_pclk、rx_pclk也需要进行时钟定义,即4个象限,每个象限含3个serdes,每个serdes含4条lane,每条lane对应一组tx/rx_pck时钟,定义如下:

for{set n 0}{$n<4}{incr n}

{for{set j 0}{$<3}{incr j}

{for{set i 0}{$i<4}{incr i}{

create_clock-name quad${n}serdes${j}_tx${i}_pclkperiod 3.2[get_pins quad${n}/serdes${j}/PLL/tx_pclk]

create_clock-name quad${n}serdes${j}_rx${i}_pclkperiod 3.2[get_pins quad${n}/serdes${j}/PLL/rx_pclk]}}}

2)时钟组定义

交换芯片的时钟属于不同时钟域,有同步时钟和异步时钟两类。异步时钟不共享固定的相位关系,时序分析时,这类异步时序路径不需要进行时序分析或串扰分析。为避免工具在满足这类路径的时序要求时造成无谓的时间开销,通常采用set_clock_groups指令[1-3]定义不同的时钟分组,对于没有相位关系的多个时钟,定为-asynchronous。上述时钟,除GCK_ip_div2、GCK_ip156、GCK_ip312为PLL_sys_clk的生成时钟,需定义到一个group,其他时钟均为异步时钟,分属不同的group,定义如下:

set_clock_groups-asynchronous-name ASYNGRP

-group[get_clocks“REF_CLKP”]

-group[get_clocks“REF_CLKN”]

-group[get_clocks“TCK”]

-group[get_clocks“Debug_clk”]

-group[get_clocks“PLL_sys_clk GCK_ip_div2 GCK_ip156 GCK_ip312”]

-group[get_clocks“quad0serdes0_tx0_pclk”]

-group[get_clocks“quad0serdes0_rx0_pclk”]

…

时钟GCK_ip156和GCK_ip312在实际电路中不存在两个时钟共存的情况,即物理上是独立的,定义为:

set_clock_groups-physically_exclusive-name IPGRP-group“GCK_ip156”-group“GCK_ip312”

3)其他时钟特性定义

由于时钟本身存在时钟抖动、时钟偏斜、时钟延迟等不确定特性,需定义clock_uncertainty加以考虑,定义如下:

set_clock_uncertainty-setup 0.15[all_clocks]set_clock_uncertainty-hold 0.1[all_clocks]

3.1.2 端口约束的设计

1)端口延迟

对于除寄存器到寄存器之外的三种时序路径,需要对外部IO的延迟进行时序约束。RapidIO交换芯片的IO多数为静态信号,不需要考虑IO延迟;而与JTAG相关的端口信号则必须定义端口延迟,如数据端口TDI、TDO,复位信号TRST,模式选择信号TMS,定义如下:

set_input_delay-max 15-clock[get_clocks TCK][get_ports“TRST TDI TMS”]-clock_fall-add

set_input_delay-min 1-clock[get_clocks TCK][get_ports“TRST TDI TMS”]-clock_fall-add

set_output_delay-max 11-clock[get_clocks TCK][get_ports“TDO”]-add

set_output_delay-min 0-clock[get_clocks TCK][get_ports“TDO”]-add

2)其他端口约束

通过设置输入、输出端口信号的外部输入驱动能力和输出负载信息,将板级布线引入的不确定加以考虑,指导工具进行更符合实际情况的环境建模约束,对I2C接口和JTAG接口定义如下:

set_input_transition-max 4[get_ports“TDI TMS TRST SCL SDA”]

set_input_transition-min 1[get_ports“TDI TMS TRST SCL SDA”]set_load-max 15[get_ports“TDO SCL SDA”]set_load-min 5[get_ports“TDO SCL SDA”]

3.1.3 时序例外的设计

对于不需要进行时序分析的路径,或不是单时钟周期的路径,通过定义时序例外来指导工具对这些特殊路径做出正确分析。不需要做时序分析的路径采用set_false_path指令[1-3]定义伪路径来移除该路径上的约束,则工具对该路径停止时序分析。静态端口信号由于上电后信号值是确定的,将这些端口信号关联的路径指定为伪路径。对于有些单元不需要进行门控时钟的检查,可设置屏蔽时序弧,定义如下:

set_false_path -from [get_ports“RST_N FSEL0 FSEL1 fifo_bypass”]

set_false_path -to [get_ports“RST_N FSEL0 FSEL1 fifo_bypass”]

set_disable_clock_gating_check global_clock/u_test_sel/Ux

3.1.4 其他时序约束设计

除上述的时序约束定义外,对于工作条件、线负载模型等也可以进行设置,交换芯片在逻辑综合阶段通过设置负载模型以预估互连线延迟的信息,设置如下:

set_wire_load_modl-name wl0-lib u055ls*set_wire_load_mode top

3.2 时序约束检查

上述时序约束设计完成后,在Prime Time(PT)工具中通过check_timing等命令以检查约束的正确性和完整性。存在如“register clock pins with no clock”信息等,需要设计人员确认,以确保约束设计无误。

4 静态时序分析及结果

32通道RapidIO交换芯片使用Synopsys的综合工具Design Compiler,在UMC 55 nm的标准单元库下进行电路逻辑综合;采用Synopsys的静态时序分析工具PT进行静态时序验证。

综合阶段主要关注建立时间的时序检查,出现时序违例,根据其严重程度进行不同的优化改进。较小的时序违例通过工具优化等手段解决,如设置don′t_use列表,将负载过大的单元器件屏蔽掉;较大或严重的时序违例,则可能是代码设计或约束设计的不合理造成的,需要修改设计代码或者约束文件,重新进行综合及静态时序分析。如路径中组合逻辑级数过长导致Setup time不满足,在设计允许的条件下,通过插入触发器将组合逻辑路径打断,以解决组合逻辑延迟过长的问题。布局布线阶段主要关注保持时间的时序检查,通过插入缓冲器单元、改变单元的大小、删除缓冲器单元等手段,以优化保持时间,且需反复迭代多轮,最终满足时序要求。

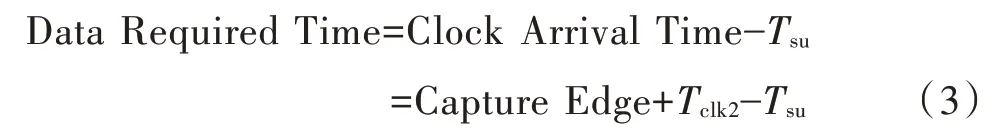

PT通过穷举法提取整个电路中所有的时序路径,以检查电路的时序是否满足要求。这里以一条触发器到触发器的时序路径的Setup check为例,查看其综合后的时序报告report_timing,如图3所示。工具分析方法同第1.2节的原理,将时序报告分成Data Arrival Time、Data Required Time、slack部 分。从 触 发 器timebase_ack_time_base_reg的时钟端口CK开始(综合后STA,从时钟源CLK_ip_clk到该触发器的CK端的网络延迟为0),从CK到Q的延迟为0.151 ns,再经过一系列组合逻辑电路,到达触发器port_capt_3_csr_reg_0__14的D端,Data Arrival Time为1.833 ns;CLK_ip_clk的时钟周期为2.08 ns(实际周期为3.2 ns,过约35%),计算Data Required Time为1.882 ns,slack为-0.011 ns,时序违例。由于约束过约35%,该违例在综合阶段可忽略,后端STA,若slack为正值,表明该时序路径满足时序要求。

图3 report_timing报告

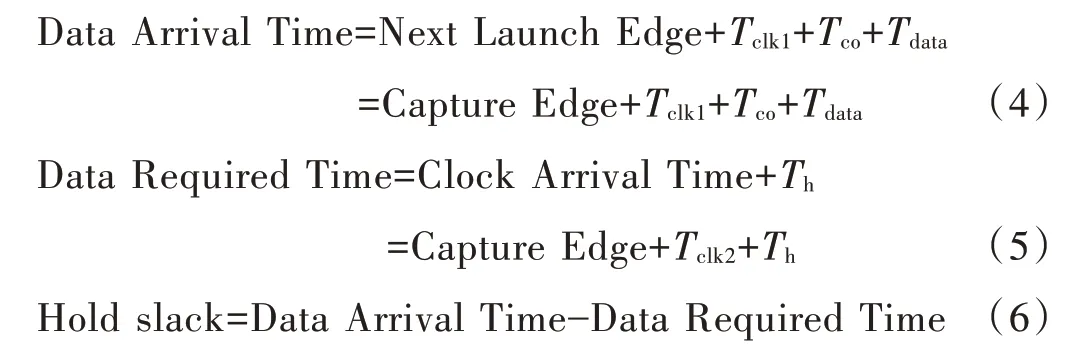

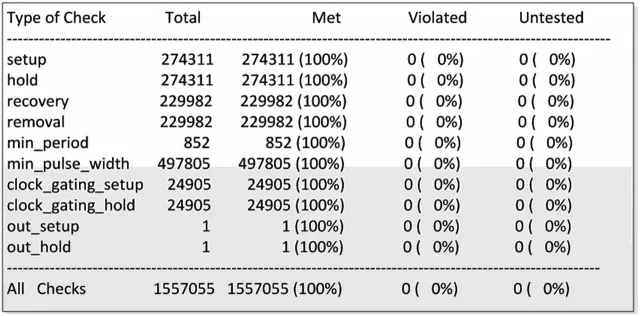

交换芯片中所有路径的时序分析结果如图4所示,电路约束覆盖率100%,所有类型check的slack均大于0,无时序违例,满足时序要求。后续芯片流片后进行了PVT测试,验证了芯片的时序正确性。

图4 analysis_coverage报告

5 结 语

静态时序分析是目前业界通用的芯片时序验证的重要手段,PT也是业界认可的时序sign-off工具。32通道RapidIO交换芯片采用静态时序分析和关键路径的动态仿真相结合的时序验证方法,通过设置芯片的时钟定义、端口定义及时序例外定义等时序约束设计,正确表述了芯片的时序设计要求,经过时序约束检查及时序优化手段,最终实现了所有路径均通过时序约束检查,确保了芯片在时序上满足设计要求,并顺利通过芯片PVT测试。