基于EMIF 总线接口的桥芯片设计

2023-02-14陶青平强小燕

沈 婧,陶青平,强小燕

(中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

0 引言

DSP 是固件系统重要的核心技术,又加之嵌入式的基础技术,使其再次成为了现代电子应用技术的重要核心技术之一。

TMS320VC5510 是常用的高性能低功耗定点数字信号处理器电路(下文简称C55x DSP),片上EMIF 接口是一个并行存储接口,设计初衷是实现DSP 与不同类型的外部扩展存储之间的连接[1]。为了使得DSP 资源得到最大的扩展,本文利用EMIF 总线接口设计了一款ASIC桥芯片。该芯片将EMIF 时序转换为片内AMBA 总线的AHB/APB 时序,从而实现DSP 对ASIC 片内资源的访问[2]。

1 桥芯片设计方案

1.1 总体设计方案

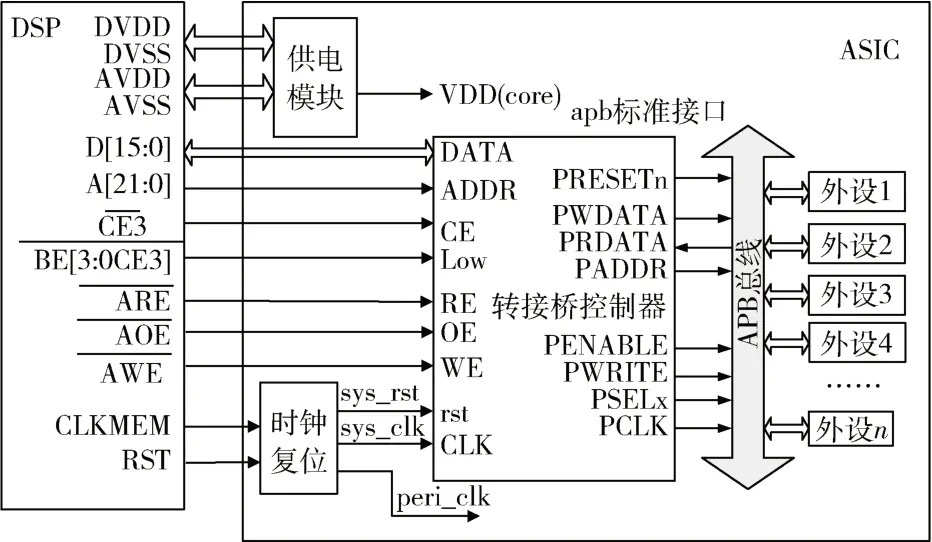

方案设计时考虑硬件资源的可复用性[3],C55x DSP与ASIC 桥芯片共用电源、地以及复位,并且通过C55x DSP 电路对EMIF 接口模式、数据地址位宽、时钟频率及读写控制信号进行配置,完成与EMIF 外部存储空间即ASIC 桥芯片的数据通信,实现C55x DSP 对ASIC 桥芯片上的资源访问。

ASIC 桥芯片的设计原理图如图1 所示,图中还展示出了ASIC 桥芯片与C55x DSP 的硬件连接关系,正是通过DSP 的EMIF 总线接口实现两个芯片之间的通信。

从图1 中可以看出,ASIC 桥芯片包含了丰富的外设模块,为了实现C55x DSP 对这些外设资源的访问,转接桥控制器、供电以及时钟复位这3 个主要模块的设计是必不可少的。

图1 ASIC 设计原理框图

转接桥控制器是本设计的关键,DSP 是否能够实现与ASIC 之间的数据通信,该控制器模块至关重要,它实现了EMIF 数据接口与APB 总线之间的时序转换,完成了DSP 与ASIC 之间的数据读写操作以及ASIC 地址空间的分配。

供电模块是ASIC 桥芯片工作的必要条件,如图1 中所示,ASIC 桥芯片的供电与C55x DSP 采用同样的外部电源,供电模块中集成了一个LDO,实现ASIC 芯片内核1.2 V 供电。

时钟复位模块采用EMIF 的时钟CLKMEM 作为ASIC 时钟输入,经过时钟同步、使能以及分频,作为ASIC 片上外设资源的时钟。复位信号则硬件上与C55x DSP 相连,同步复位。

下面将详细介绍这3 个模块的设计和实现方式。

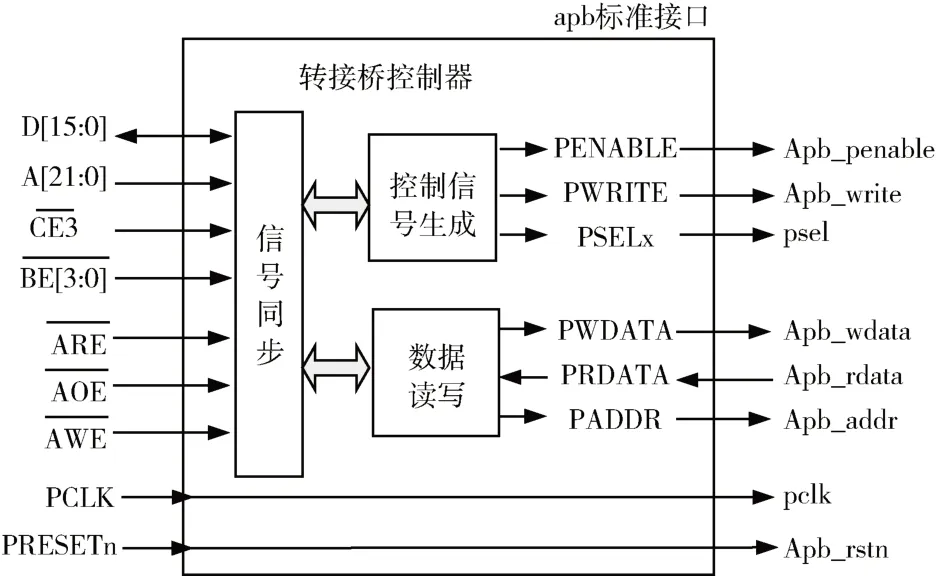

1.2 转接桥控制器设计

如图1 中所示,本设计中C55x DSP 的EMIF 接口采用的是异步通信接口,可通过配置EMIF 来进行外部异步存储的访问。而ASIC 桥芯片是一款同步电路,片内外设资源均是基于APB 总线同步设计。为了能够通过EMIF 异步接口顺利访问ASIC 片上外设资源,本设计中转接桥控制器模块的设计就显得尤为重要,模块设计原理图如图2 所示。该控制器模块不仅仅完成总线、控制信号、时钟复位信号时序的转换,数据读写过程中位宽的设计也是该模块的重要一部分。

图2 转接桥控制器设计原理图

如上文所述,EMIF 异步接口信号进入ASIC 桥芯片后,需要经过时钟同步处理后方可使用,而同步的时钟采用的正是EMIF 的输出时钟CLKMEM,该时钟可由DSP 配置为主频时钟或1/2 主频时钟,本设计配置为主频时钟。

1.2.1 控制信号设计

C55x DSP 的EMIF 异步接口有3 个CE 空间,本设计选用了EMIF 的CE2 外部空间,CE2 所对应的外部地址空间为0x800000-0xC00000,当该空间使能信号--------CE2 为低电平时,此地址空间可以进行读写访问。因此在进行ASIC 桥芯片设计时需将作为芯片使能,并将该信号与控制总线和地址总线联合译码,当该信号使能后,芯片才进入正常工作状态。

以EMIF 异步写操作为例,详细讲述控制信号的设计方法。EMIF 异步写时序和APB 写操作时序图分别如图3[4]和图4[5]所示。图3 中的信号在上文中已经详细介绍过,图4 为标准的APB 写操作时序,下面介绍APB 信号的实现方法。

图3 DSP EMIF 异步写时序

PWRITE 信号为APB 总线的写控制信号,当该信号为“1”时代表一次写入,当该信号为“0”时代表一次读出。该信号的生成需要分为读和写两部分,当写入时可由同步后的----------AWE 和--------CE2 共同生成,当这两个信号同时为低电平时,则PWRITE 为“1”,写使能打开;当读出时由同步后的--------AOE、--------ARE 和--------CE2 共同生成,当这三个信号同时为低电平时,则PWRITE 为“0”,读使能打开。

PSEL 是各APB 从机的选择信号,当PSEL 信号为“1”时代表外设模块被选中,该信号使用高位地址位来进行译码生成,生成方式如图5 所示。

图5 PSELx 信号译码逻辑

根据图4 的时序设计,PENABLE 信号需在PSEL 有效后使能,并保持一个周期的有效时间,该信号可用时钟将PSEL 信号延迟一拍得到。

图4 ASIC(APB)写操作时序图

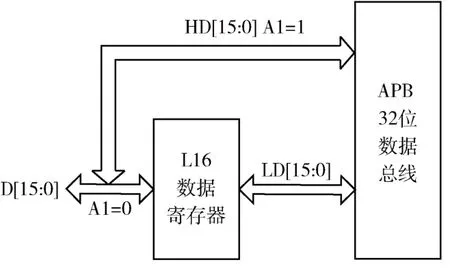

1.2.2 数据设计

C55x DSP 的EMIF 数据总线支持8、16、32 位数据位宽,而地址引脚的使用取决于数据的宽度,其对应关系如表1 所示。而ASIC 桥芯片的外设资源采用的是32 位数据访问,为了减少ASIC 芯片IO 引脚的数量,同时考虑数据传输的效率,综合考虑后将EMIF 配置为16 位数据位宽,根据表1 的对应关系得出地址引脚A[21:1]为有效位。

表1 地址引脚与数据位宽对应关系

正如上文所述,C55x DSP 与ASIC 桥芯片之间通信的数据是需要经过位宽处理的,数据位宽处理在ASIC桥芯片中完成,32 位APB 数据总线的设计如图6 所示。C55x DSP 的EMIF 配置为16 位数据访问后,当需要进行32 位数据传输的话,数据会分成2 次传输,每次传输16位,而地址信号A1 可作数据传输高/低的判断信号。

图6 APB 数据总线设计

以写入数据为例,若32 位数据从EMIF 写入ASIC 桥芯片,数据会分两拍分别输出低16 位数据和高16 位数据,当A1=0 时,EMIF 与ASIC 之间传输低16 位数据,当A1=1 时,传输高16 位数据。L16 数据寄存器用来存储EMIF 第一拍发送过来的低16 位数据,等EMIF 第二拍发送来的高16 位数据到达,即A1 为1 后,再一起发送给APB 总线。读数据的过程类似,EMIF 先接收APB 低16位数据,其次是高16 位,当检测到A1=1 时,代表EMIF读操作完成。

1.3 时钟复位设计

ASIC 电路的时钟输入为CLKMEM,该时钟具有较强的可配置性,可由DSP 芯片灵活配置。

CLKMEM 时钟进入ASIC 芯片后经过时钟同步单元生成系统时钟sys_clk,RST 信号经过sys_clk 同步生成系统复位信号。

如图7 所示,sys_clk 经过使能后直接送给各外设模块,除了ADC 模拟部分电路,该部分电路设计时会加入分频电路,满足ADCCLK 的设计需求。

图7 时钟复位设计框图

1.4 供电设计

ASIC 电路与DSP 共用数字/模拟电源和地,如图1所示,ADC 直接由DSP 的3.3 V 模拟电源AVDD 和模拟地AVSS 提供power,而3.3 V 数字电源DVDD 经过LDO进行电平转换,生成1.2 V 内核供电VDD,为数字外设供电,最大负载可达120 mA。

2 版图设计

本设计版图设计布局如图8 所示,图中标出了模拟IP 的物理位置,版图的大小由I/O 布局决定,版图面积为19.48 mm2。

图8 ASIC 版图示意图

3 测试结果

本设计测试分为两个阶段,首先是在tapeout 之前进行的FPGA 原型验证,其次是ASIC 芯片回片后的实装测试。

3.1 FPGA 原型验证

FPGA 原型验证已是当前原型验证的主流且成熟的芯片验证方法——设计通过将RTL 移植到现场可编程门阵列(FPGA)来验证ASIC 的功能。设计使用Xlinx 公司K7 系列FPGA,验证流程如下:

(1)设计输入

采用EDA 仿真工具NC-Verilog 对RTL 设计进行充分仿真,检验设计的功能是否正确。

(2)FPGA 综合

采用综合工具Synplify 将RTL 代码翻译成FPGA 网表,并根据约束条件优化所生成的门级逻辑连接,输出edf 和edn 等文件。

(3)布局布线

采用FPGA 厂商提供的工具Vivado 进行布局布线,进行ASIC 芯片内部功能单元的实际连接和映射。

(4)板级调试

在完成以上步骤后,会生成BIT 文件进行板级调试。

主控软件运行在DSP 芯片中,完成各个控制信号和配置数据的产生、数据格式转换以及配置时序的控制等工作[3]。通过EMIF 控制寄存器设置数据总线为16 位位宽,使能--------CE2 外部地址空间,并配置如图3 中所示的Setup、Strobe 以及hold 时间。外部输入时钟使C55X DSP 工作在50 MHz 频率下,即CLKMEM 频率为50 MHz。

当DSP 主控和ASIC 桥芯片完成所有配置后,C55X DSP 就可以启动对ASIC 片上资源的访问。图9 展现了ASIC 桥芯片在C55X DSP 的主控下完成的UART 数据发送功能。当ASIC 芯片工作后,使能UART 模块,通过DSP 主控对UART 寄存器进行数据写操作,配置UART为发送模式,并先后完成UART 数据(0x23h、0x55h、0x120h)的发送。

3.2 实装测试

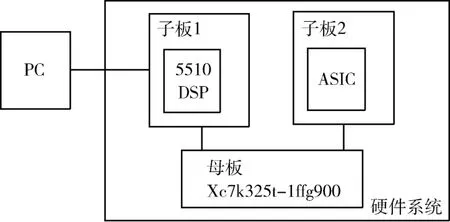

在芯片出带到回片的这段时间里,FPGA 验证为实装测试做好了充分的准备,测试程序开发均采用CCS 软件设计平台,程序不需要进行环境的移植;硬件系统以FPGA 为验证平台,采用母板加子板的总体结构[5],FPGA 既可以将ASIC 网表与DSP 连接验证,也可以作为载体将DSP 与ASIC 芯片连接进行实装测试。

本设计的实装测试硬件平台如图10 所示,母板FPGA 将DSP 5510 的EMIF 异步接口、时钟复位以及电源、地与ASIC 芯片连接,子板上则集成了其他外设辅以ASIC 和DSP 完成相应的调试功能。

图10 实装测试硬件平台

在设计中,采用DSP 集成开发环境CCS[7]对ASIC 芯片进行实测。使用FPGA 原型验证阶段开发的验证程序完成ASIC 各功能模块的测试,并与FPGA 原型验证的结果进行了比较,发现除模拟模块无法进行FPGA 原型验证外,其他外设测试结果与原型验证结果一致。

4 结论

本文基于TI 55 系列DSP 电路的EMIF 接口实现了桥芯片ASIC 的设计,该方法实现了DSP 电路的外设功能扩展。该ASIC 芯片集成了串行、并行数据接口以及模拟模块等,经过FPGA 原型验证后于某工艺线流片,并通过与DSP 的实装测试验证了ASIC 芯片中的各模块均可与DSP 成功通信,这增加了SoC 设计的灵活度。在实际应用时,可考虑将ASIC 和DSP 进行叠片封装设计,实现SoC 芯片的功能。