基于ZYNQ-7020的CAN总线节点接口设计与实现

2023-02-08方海伊豆海利

方海伊,豆海利,冯 源

(1.中国航空工业集团公司西安航空计算技术研究所,陕西 西安 710119;2.空军工程大学 基础部,陕西 西安 710051)

0 引 言

控制器局域网(Controller Area Network, CAN)作为一种现场总线,具有良好的通信速率和开放性,采用简单的控制方式即可扩展总线并连接多个设备。目前CAN总线凭借其良好的性能优势已在汽车电子、工业控制以及航空航天等领域得到了广泛应用。

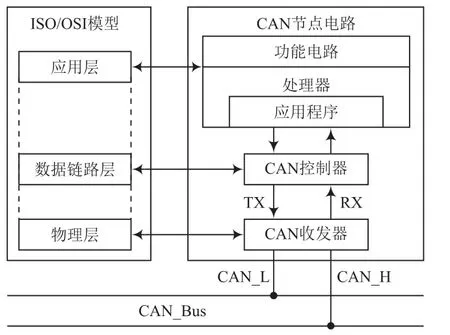

CAN总线是一种总线型结构的通信网络,总线上各个不同的CAN节点具有特定的功能,比如实现传感器数据采集、设备控制、数据显示等,但所有的CAN节点都具有大致相同的硬件接口和软件结构,如图1所示;并且总线上的所有节点均通过CAN接口电路连接到同一个通信电缆上。CAN节点接口通常由CAN总线收发器、CAN总线控制器以及接口控制器组成。这种结构实现的CAN控制可以采用不同的节点控制器,具有较强的灵活性,但是外围系统组成较为复杂,通常需要配合DSP、CPLD等芯片实现通信功能[1],外围电路控制过程也较为复杂。另外CAN节点接口还可以将CAN总线控制器集成于节点控制器中,利用节点控制器不仅实现了节点的应用程序,还实现了总线收发器控制的功能,这种结构的控制过程以及外围电路组成较为简单,减少了成本,但是对于控制器本身的功能、性能要求较高,且需要具有较好的通用性。

图1 CAN节点结构

ZYNQ-7000系列芯片是一种由Xilinx公司研发,在市场上具有代表性的Soc芯片,该系列芯片采用ARM+FPGA结构,将FPGA可编程逻辑和双核ARM Cortex-A9集成在一颗芯片上。芯片的PS (Processing System)系统集成了两个 ARM处理器、内部存储器、外部存储器接口和大量外设,可以实现总线节点设备的连接以及总线节点接口的控制功能;芯片的PL(Programmable Logic)系统则具有大量逻辑门电路、查找表以及触发器,并配有诸多数字信号处理单元,大大提高了数据并行处理能力。芯片中高带宽的AXI总线实现了PS与PL系统的互连。芯片的PS和PL可分开编程[2-3],均可独立运行,并在上电或复位下启动。同时为了方便用户开发,Xilinx 向用户提供了许多集成的IP核,方便用户快速开发使用,但是许多集成的IP核不能完全满足用户的多样需求,因此在FPGA上还可以通过自定义IP核,即模块化的设计方法实现用户需求[4]。与使用ARM配合 FPGA的传统系统[5]相比,使用ZYNQ-7000作为系统控制器,不仅可以有效降低开发成本,提高开发效率,还可以实现更好的性能和更高的集成度。

本文在Vivado开发平台上基于ZYNQ-7020芯片进行系统设计。通过调用ZYNQ-7020中的PS系统、PS系统复位、AXI互连、PL系统IP核完成系统级建模。随后,在ZYNQ-7020上PL系统中利用Verilog HDL完成模块化设计,实现CAN总线控制器功能,并利用AXI IP核实现与PS之间的数据交互。基于以上设计,在ZYNQ-7020芯片的PS系统中可以设计完成CAN总线接口和串行通信接口的创建,使用SDK软件编写CAN总线驱动程序[6],实现系统应用层运行。

1 基于ZYNQ的CAN总线节点接口硬件设计方法

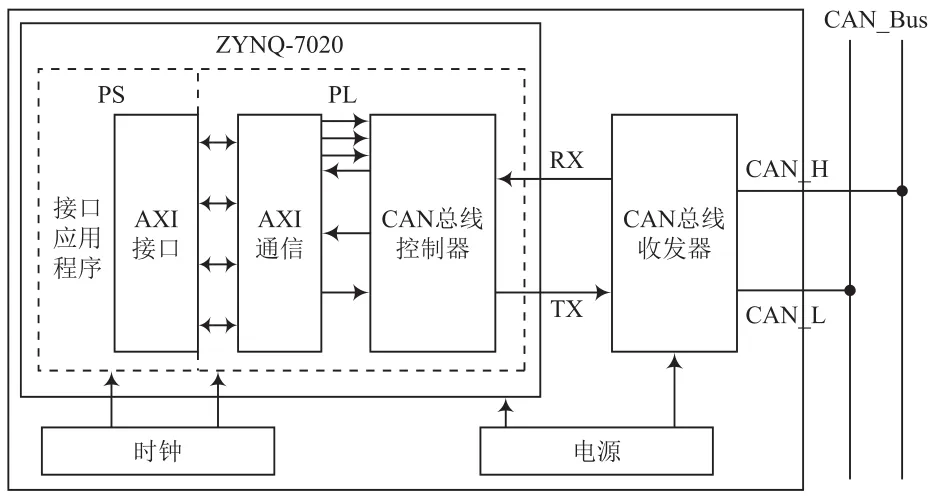

本文提出了一种基于ZYNQ-7000系列芯片的CAN总线节点接口的设计方案,在设计中采用ZYNQ-7020作为主控制器,利用其PS系统和PL系统协同工作并配合CAN总线收发器来实现CAN节点接口的控制。基于ZYNQ-7000系列芯片的CAN总线节点接口的整体设计结构如图2所示,总线节点接口主要由电源电路、时钟电路、ZYNQ-7020外围电路、CAN总线收发电路以及其他辅助电路组成。

图2 基于ZYNQ-7020的CAN节点接口硬件结构

(1)电源电路主要由外部供电电路以及电压转换电路组成,采用开关电源实现外部高电压转换为低电压,具有电源防抖、转换效率高的特点。针对ZYNQ-7020芯片上PS系统以及PL系统电源单独工作的特点,为其分别配置1.0 V、1.8 V、3.3 V供电电源实现内核供电、RAM供电、IO BANK供电。配合电源芯片的输入端电源转换启动控制管脚以及输出端状态指示管脚,实现ZYNQ-7020芯片对于PS、PL的上电顺序要求[7]。

(2)时钟电路分别采用33.3 MHz和50 MHz的有源晶振为ZYNQ-7020芯片的PS系统和PL系统提供时钟源。虽然PL系统的时钟源也可以通过PS系统的PLL产生,但是为了实现PS系统与PL系统的独立控制,向PL系统提供了单独的时钟源。

(3)ZYNQ电路主要由ZYNQ-7020芯片、配置电路以及外设组成。由图2可知,ZYNQ-7020芯片作为主要的功能芯片,主要包括PS系统和PL系统两部分:在PL中建立CAN总线控制器模块,用于CAN收发器逻辑电平收发以及CAN协议解析,并利用AXI模块实现与PS的通信,在PS中实现CAN总线驱动程序,利用AXI总线进行PL的控制和CAN总线数据的传输,具有集成度高、功能多样、处理速度快的特点。ZYNQ-7020芯片配有QSPI FLASH芯片作为启动设备存储系统的启动镜像文件,包括PL的bit文件、ARM的应用程序代码、用户存储数据等,并且采用DDR3存储直接连接ZYNQ-7020芯片的PS系统,为系统提供高速外部存储设备。

(4)CAN总线收发电路的主要功能是采用CAN收发器芯片将CAN总线差分电平转换为CAN控制器的逻辑电平,采用具有电气隔离和电源隔离的收发模块,具有体积小、隔离功能强、使用方便的特点。

从图2中可以看出,ZYNQ-7020芯片是本次节点接口设计中的主要功能实现部件,主要包含的逻辑实现功能为:节点接口的CAN总线控制器功能、AXI通信模块功能以及在PS系统中建立AXI通信功能。在PS系统中根据总线节点设备要求移植Linux操作系统、使用SDK软件设计编写CAN总线驱动软件接口,作为驱动开发重点内容,不在本文中进行论述。

2 AXI总线控制设计

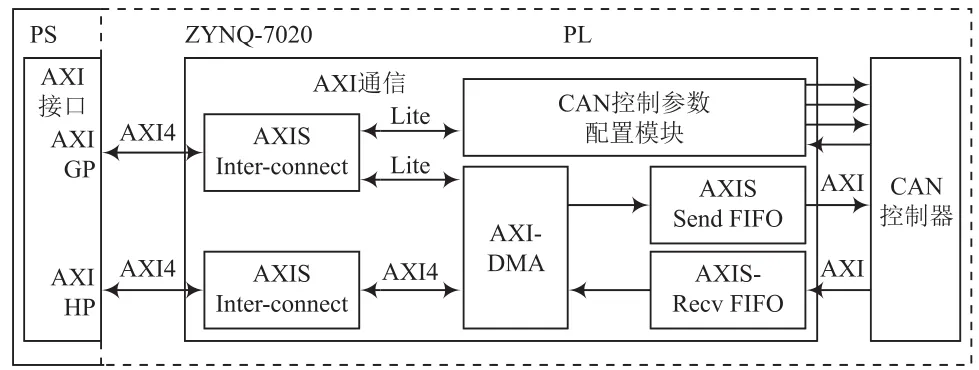

基于ZYNQ-7020的CAN节点设计中,AXI通信通路作为CAN总线数据链路层与应用层交互的主要途径,是本次设计中的重要内容。AXI通信实现了PS系统与PL系统之间的通信功能,如图3所示的设计框架,AXI通信主要用于CAN总线数据访问、PL系统的控制即CAN总线控制器模块的功能控制。

图3 ZYNQ-7020上PS和PL系统通信方案设计框图

AXI通信功能在PL设计中由AXI Interconnect模块、AXI-DMA模块[8]、AXIS-Data FIFO以及CAN控制参数配置模块组合实现[9]。AXI Interconnect模块主要用于主设备管理多个从设备,通过AXI Interconnect模块可以扩展多个AXI-Lite总线接口,然后将多个从设备模块分别与AXI-Lite总线接口连接,通过为这些模块分配不同的偏移地址,主设备可以控制从设备。AXI-DMA是一种用于实现DMA功能的IP核,具有读DDR存储器和写DDR存储器两个通道,当需要读取数据时,AXI-4总线从PS的DDR内存中读取数据,AXI流总线将数据传输到PL的FIFO缓冲区;在写入DDR存储器的过程中,PL设备通过AXI流总线将数据发送到AXI-DMA,通过AXI-4总线将数据传输到PS。AXI-DMA IP核内部的寄存器可以通过AXI-Lite总线进行读写。AXIS-Data FIFO为AXI流总线的接口,用于数据存储。CAN控制参数配置模块的主要作用是将PS发送过来的命令和参数传递给PL的CAN控制器,同时关注PL中CAN控制器状态以方便PS读取。

当AXI通信用于PS对PL即CAN控制的逻辑功能控制时,这部分信号的控制不涉及高速数据传输,因此在PS中采用AXI-GP接口实现,通过AXI4总线传输至PL的AXI Interconnect模块,将信号通过AXI-Lite总线写入CAN控制参数配置模块,从而进行FIFO控制、CAN控制器逻辑控制和复位、CAN总线数据接收和错误等信号的检测。

另外,当AXI通信被用于CAN总线数据访问时主要是通过调用ZYNQ的AXI-DMA IP核来实现的[10]。当PL接收到CAN总线数据后缓存在AXIS-Send FIFO中,将数据通过AXI流总线写入AXI-DMA模块,该IP核产生中断信号通知PS处理器接收数据,PS响应中断并通过AXI-HP接口将数据写入PS的DDR。当PS向CAN总线发送数据时,PS处理器通过AXI-Lite总线将数据的信息写入AXI-DMA IP,该IP核读取DDR中的数据并将数据写入AXIS-Recv FIFO中,再通过CAN总线控制器发送数据。

3 CAN总线控制器功能设计

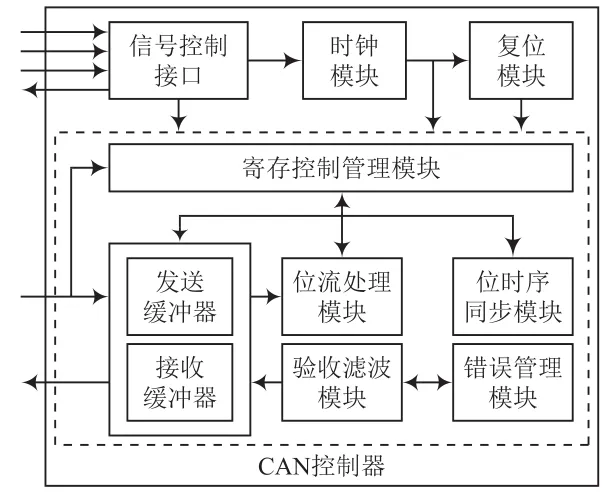

CAN节点接口的总线控制器是通过ZYNQ-7020芯片上的PL逻辑实现,利用Verilog HDL完成模块化设计,图4所示为PL系统上CAN总线控制器的设计框图。从图4可以看出,该逻辑主要包括信号控制接口、时钟模块、复位模块、寄存控制管理、位时序同步、位流处理、错误管理、验收滤波和收发缓冲等功能模块组成。其中信号控制接口实现PS控制信号的接收和解析,并将控制信号下发给CAN总线控制器模块。时钟模块和复位模块根据PL系统中不同模块控制性能产生相应的时钟信号,并响应各类复位信号。参考SJA1000 CAN控制器功能将本次设计中CAN控制器的主要功能模块再分为:寄存控制管理、位时序同步、位流处理、错误管理、验收滤波和收发缓冲等模块。

图4 ZYNQ-7020上CAN总线控制器设计框图

(1)寄存控制管理模块:在CAN控制器中大量的工作需要通过寄存器实现,例如命令下发、逻辑状态判断、中断信号标记、中断使能、屏蔽掩码记录、错误计数等功能。因此在FPGA中根据有无、同步/异步复位方式的不同来定义四种寄存器的实现方式[11],并根据不同功能要求在寄存器控制模块中进行每个寄存器的类型定义。在该模块中配合以上寄存器实现CAN控制器的各模块工作状态管理和控制。

(2)位时序同步模块:CAN总线作为一种异步串行通信总线,缺少时钟线,因此在位流接收和处理中,控制器需要实时观察总线状态,必须在接收到总线信号后立即产生位流同步信号,减小与总线的时钟误差以消除漏拍、错拍现象,并且对于总线数据流的位填充位也进行时钟信号软同步。

(3)位流处理模块:位流处理器是缓冲区与位时序同步模块之间的控制数据流的模块,根据位时序同步信号按时钟节拍进行有效数据流采集和传输,根据CAN2.0协议执行标志位检测填充、位填充、仲裁、数据和信息提取填充,并检测处理错误。对于没有位填充错误、格式错误和CRC校验错误的帧数据产生ACK响应字,并判断接收节点是否产生ACK响应。

(4)错误管理模块:该模块中最重要的功能是实现CAN控制中采用的CRC循环冗余校验方法。CRC校验利用位流处理结果在发送数据时根据发送内容计算出CRC段数据并传输至位流处理模块进行位填充和发送;对于接收到的位流数据,根据接收内容计算出一个CRC值并与接收的CRC段数据进行比较。若存在传输错误时,则向寄存器和总线通报错误消息并进行错误计数;同时该模块根据其他模块工作发生的格式错误、应答错误、位填充错误、位发送错误、CRC校验错误等进行CAN错误帧管理。

(5)验收滤波模块:该模块根据寄存器的屏蔽掩码和验收代码设置,判断CRC校验正确的数据帧是否接收并存入接收缓冲器中。

(6)接收、发送缓冲模块:两模块中分别存储需要接收和发送的CAN总线数据,遵循FIFO的先入先出原则,并且通过AXI总线连接PS系统实现应用层CAN数据总线控制。

通过以上模块设计实现CAN总线控制的功能逻辑,配合时钟模块以及控制信号完成CAN总线协议的解析和数据收发。完成所有设计后,通过 Vivado完成编译并集成 CAN控制器IP核模块。该模块利用大量逻辑门电路实现,具有一定的通用性,可移植性好。

4 结 语

本文基于ZYNQ-7020芯片的ARM+FPGA架构进行CAN总线节点接口电路的设计实现。主要在Vivado开发平台下调用ZYNQ-7020芯片的PL系统和PS系统实现CAN节点接口的数据链路层功能以及与应用层的交互。PL系统中利用逻辑器件完成CAN总线控制器的功能开发,具有CAN总线协议解析以及数据收发能力。在PL系统和PS系统中分别设计开发了AXI通信功能,用于PL系统与PS系统的CAN总线数据访问、PL系统中CAN总线控制器功能控制。通过有效地利用ZYNQ-7020芯片的PS系统建立Linux系统,可运行多种CAN总线驱动接口软件,实现与多种CAN节点设备的连接,具有一定的应用价值。本文提出的节点接口设计具有可扩展性良好、模块体积较小且外围接口丰富的特点,可满足CAN节点用户的个性化需求。