应用于时间数字转换器的补偿校准算法及电路

2023-01-05童纪昀张孟翟赵发展

赵 捷, 赵 野, 童纪昀, 王 莎, 张孟翟, 赵发展

(1.中国科学院 微电子研究所,北京 100029; 2.中国科学院大学,北京 100029; 3.中国科学院 硅器件技术重点实验室,北京 100029)

目前,较大动态范围的时间数字转换器(time-to-digital converter,TDC)需依赖计数器实现粗量化[1-2],同时又依赖于细计数实现高精度,如基于延时链或多相位内插的 Coarse-Fine 型 TDC、门控环形振荡器型 TDC、结合 2-D Vernier 延时链的多级内插型 TDC 等。与此同时, PVT(process, voltage and temperature)影响及时钟抖动的因素也给 TDC 的线性与稳定性带来了严峻挑战[3-4]。

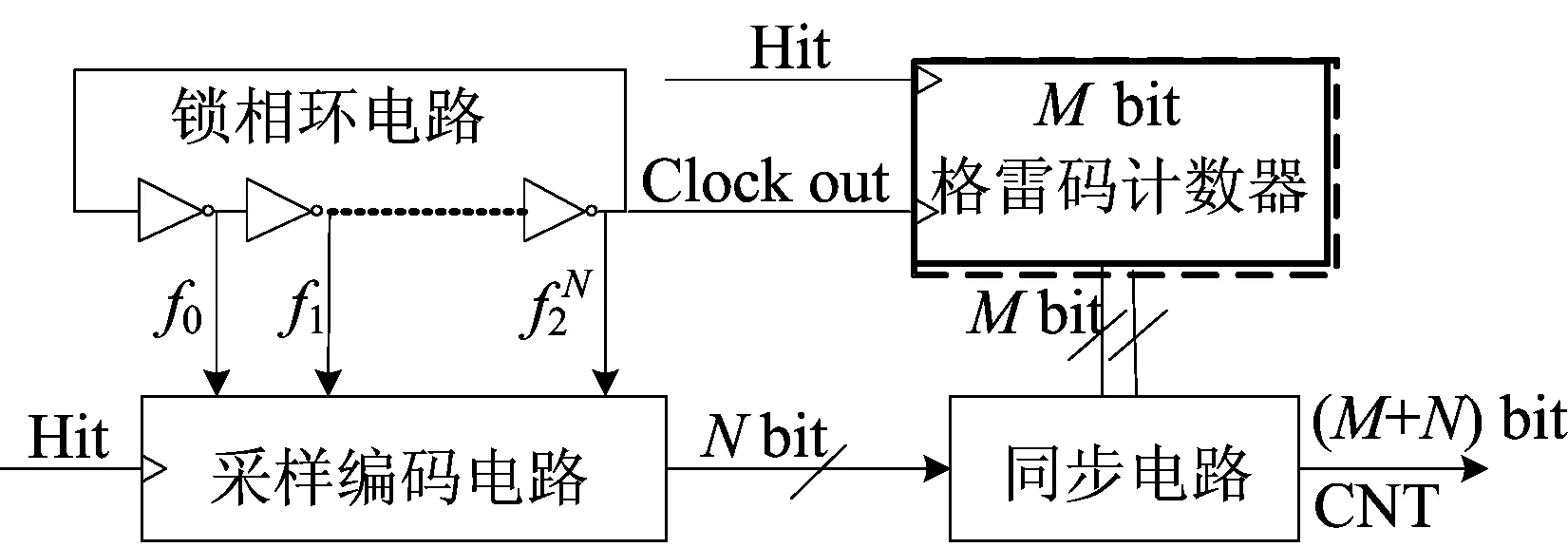

一种传统相位内插型粗细计数TDC 结构如图1所示。图1中,时钟相位电路能够产生多相位时钟信号(f0,f1,…,f2N),并在编码模块进行编码产生Nbit 细编码值PHASE,与此同时粗计数器产生出Mbit 粗编码值,并在同步后产生(M+N)bit的 二进制编码,最终输出值 CNT 信号保存输入脉冲信号对应的时刻信息。

图1 传统相位内插型粗细计数TDC结构

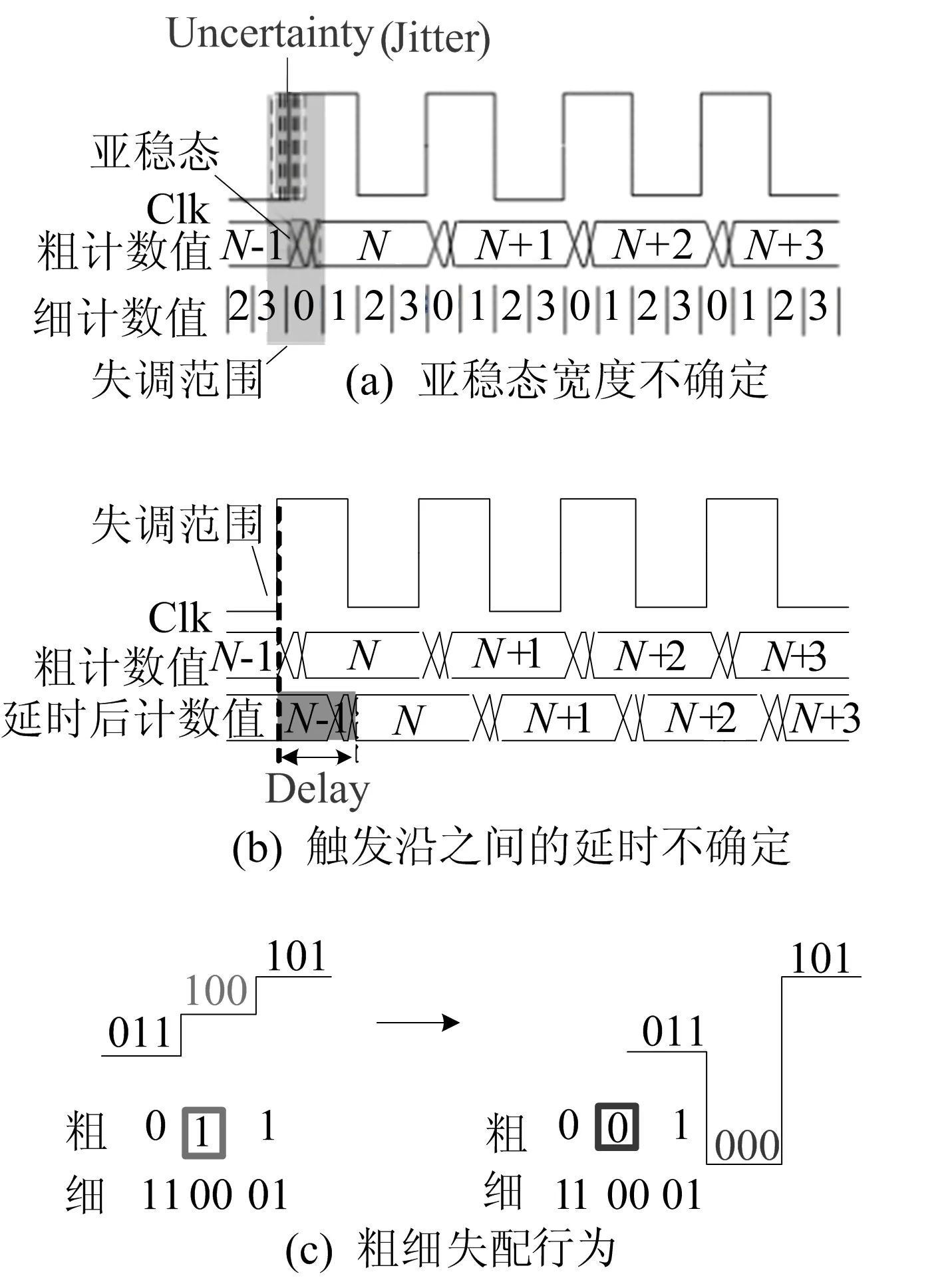

在理想情况下,粗计数和细计数应该同时进行,但由于 PVT 因素以及器件本身建立时间产生较大的不确定时延的影响,计数器会出现错误的采样,导致整个 TDC 码产生失级失配的问题,严重损害了 TDC 的线性度与可靠性。传统的 Coarse-Fine 型 TDC在非理想条件下发生的粗细失配行为如图2所示。

图2 传统Coarse-Fine 型 TDC 非理想条件下发生的粗细失配行为

现有的方法还不能完全解决因时钟抖动、亚稳态、数据延时等多重不确定性对 TDC 的线性和稳定性带来的影响[5-11]。因此本文提出一种新型的补偿校准算法及电路(select compensation algorithm and calibration circuit,SEC),通过增加延时提取电路和2个细计数延时单元,利用选取编码表及配套的算法可以消除时钟抖动和亚稳态带来的误差。相比前人的研究工作,本文提出的全数字校准电路结构简单,算法复杂度低,不需要基于统计学的复杂算法实现,并且支持多通道的扩展应用。

1 新型补偿算法及校准电路

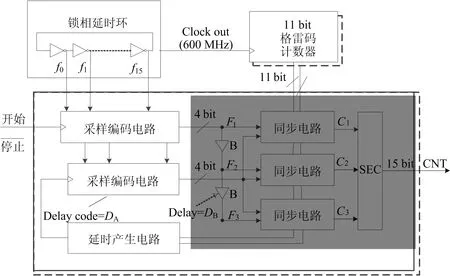

本文提出的带有新型补偿算法及校准电路TDC结构如图 3 所示。

图3 带有补偿算法及校准电路的粗细计数型TDC结构

利用延时采样电路动态提取出粗计数器在传输过程中的延时值,在同步模块前加入2个延时缓冲器以调整细编码,配合粗采样编码、细采样编码以及延时编码的校准补偿算法,在同步之后将3组数据导入SEC选取规则模块中进行选取调整,实现对PVT、时钟抖动及传输延时带来的亚稳态问题。

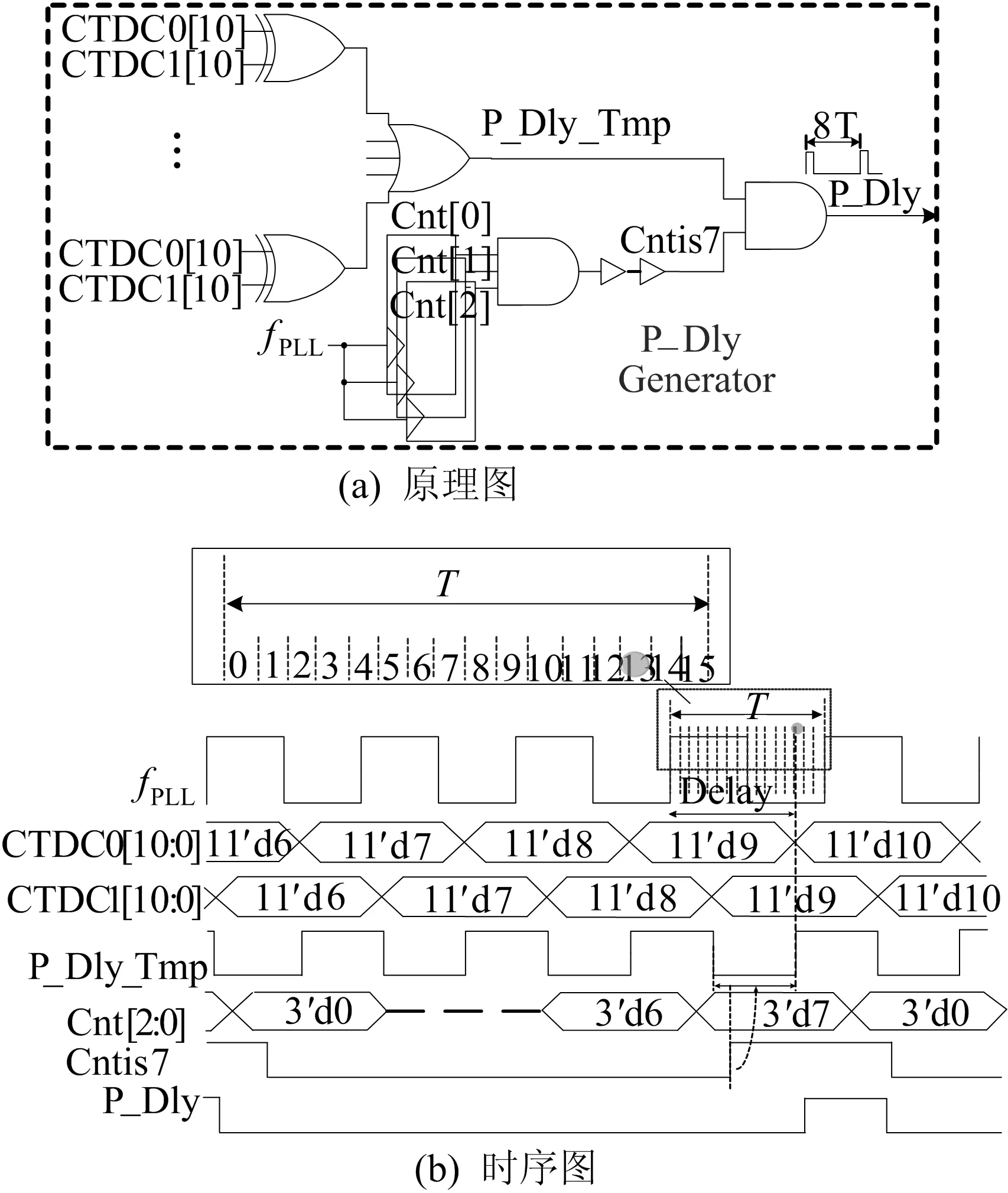

1.1 延时提取电路

延时提取电路的原理图和时序图如图 4 所示。首先将采用的双边沿格雷码计数器 CTDC 0 与 CTDC 1 的11 bit 数据进行按位异或;然后通过或门得到信号 P-Dly-Tmp(图4b),该信号上升沿与时钟上升沿之间的间隔就是上升沿计数器 CTDC 0 相对于时钟的延时值;最后通过计数器生成的门控信号 Cntis 7 与 P-Dly-Tmp 信号相与,得到 P-Dly 信号即为提取出的延时触发信号。并且通过门控可以有效地控制该信号刷新的频率,节约资源。

图4 延时提取电路原理图和时序图

在该设计电路中,核心电路部分尽可能地采用门单元而非寄存器单元,使得新结构不引入新的延时,并且提取出的触发信号 P-Dly 可以类似于输入的脉冲时间信号进行采样处理,编码后得到的数字码就可以动态地表示传输延时。在后仿真分析中,可以发现在不同工艺节点下,未改善之前电路引入的延时值会随着温度、电压等因素的不同而变化,而采用了延时提取电路后,可以很好地补偿该延时带来的误差。

1.2 补偿算法及时序原理

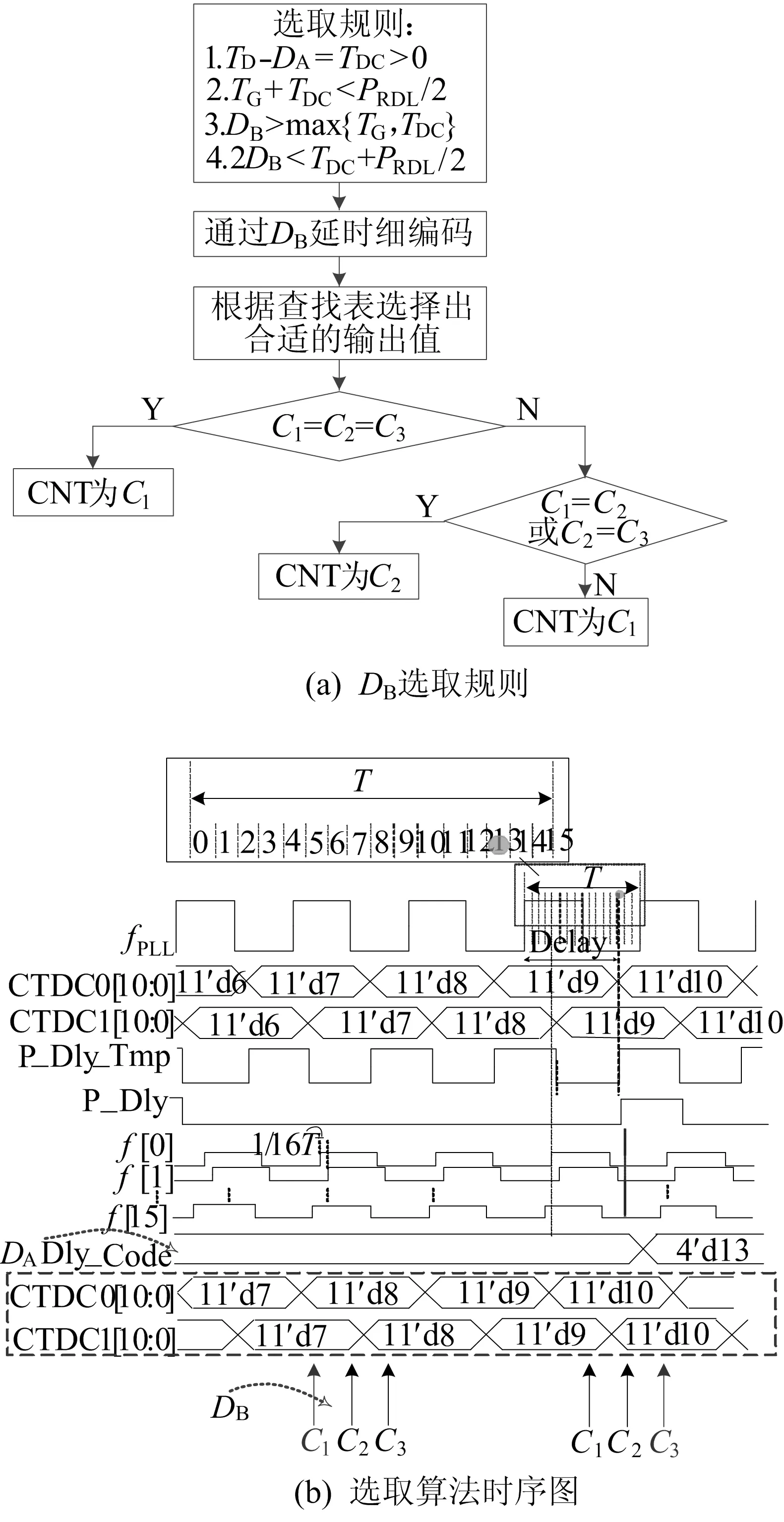

DB选取规则和选取算法时序图如图5所示。

假设延时同步后生成的3组输出分别为C1、C2、C3,它们之间的时间间隔就是DB延时值的物理含义。定义粗计数器本身延时为TD,延时提取电路提取的延时值为DA,亚稳态区间为TG,一个时钟周期的时间值为PRDL,则DB的选取必须满足以下3个条件:①DB的值应该大于等于TG,这样3个样本至多只有一个会落入亚稳态区间;②DB应当同时大于TDC和TG,以便可以观察C1是否处于TDC区域;③ 满足图5a中的第4条原则,使得第1个采样点C1在上升沿计数器周期时,最后的采样点C3不会超出下降沿计数器周期。在这些条件下,可以选取出最合适的DB值(在0.110 μm工艺中,选择DB对应为300 ps延时)。因此按照算法选取流程即可得到正确的输出值CNT。

图5 DB选取规则和选取算法时序图

从图5b可以看出,本文使用的算法校准思路时序原理经过延时采样电路后,通过组合逻辑提取出P-Dly信号并编码生成延时信息DA,将延时补偿到电路中后得到的双级粗计数器如图5b虚线框中所示。但是在该过程中会引入新的传输延时(远小于寄存器受 PVT 影响的延时),因此需要进一步对细编码进行相应补偿以便于选取出正确的值。通过增加延时采样电路和2个细编码延时值DB,就可以消除任何采样错误,给出最终的3组输出编码C1、C2、C3。通过该时序原理可以看出,如果其中某个值有可能发生采样错误,那么另外2个值经过延时选择合适的粗计数器即可避免采样错误。

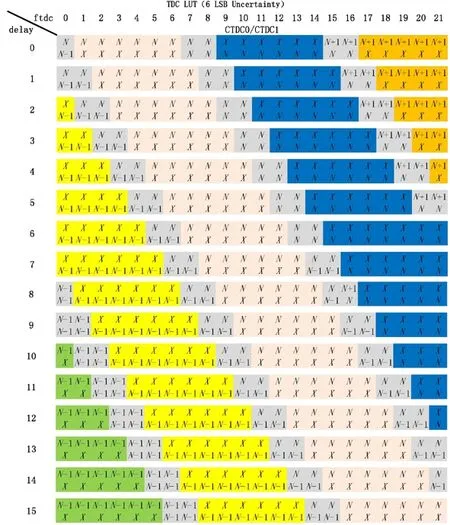

1.3 选取规则查找表

定义的选取规则查找表如图6所示。因为本文采用的是双边沿粗计数器,所以在校准补偿选取规则模块中,本质上是通过延迟编码值调节,由3个细采样的值选择出2个粗采样的值。按照表6中的不同区域,根据延迟 Delay 编码和细计数编码值 FTDC 的取值,选择出粗编码 CTDC 的值。查找表中每一格单元的2个数字分别表示在该延时情况下的 CTDC 0 与 CTDC 1 的值,为了确保输出结果良好的一致性,若在该条件下有可能落入亚稳态区间,则设置为X;否则设置为N或在其基础上加减1。另外,原本 FTDC 的取值范围为 0~15,但是由于经过了2次DB的延时(每一次为3),因此设置了虚拟的采样范围16~21,用于补充查找表。如当延迟码为3,FTDC 码为12~17时,应当选择 CTDC 1 的值N进行同步,并输出对应的最终值CNT。

图6 选取规则查找表

从图6可以看出,在CTDC 0 和 CTDC 1 的切换边界,总是有至少连续的3个相同值,即在考虑了大范围时钟、数据不确定性的前提下,即使 FTDC 发生抖动,CTDC 值依然可以保持稳定,避免了 TDC 跳码的发生。并且从电路本身,新增加的电路模块不需要大量的数据采集,仅在原有的基础上新增1组延时编码值以及2组细采样值,不需要大量的数据处理,仅通过简单的算法选取模块即可获得最终稳定的输出,因此该查找表具有如下特征:① 最大可容忍6 LSB 的时钟抖动、亚稳态等造成的不确定性;② 至少可容忍 FTDC 左右1 LSB 的漂移,这保证了进位边界条件下 CTDC 值不会发生跳变;③ 至少可容忍Delay左右1 LSB 的漂移,保证了延时采样有误差的情况下,CTDC 值不会发生跳变。

2 仿真分析

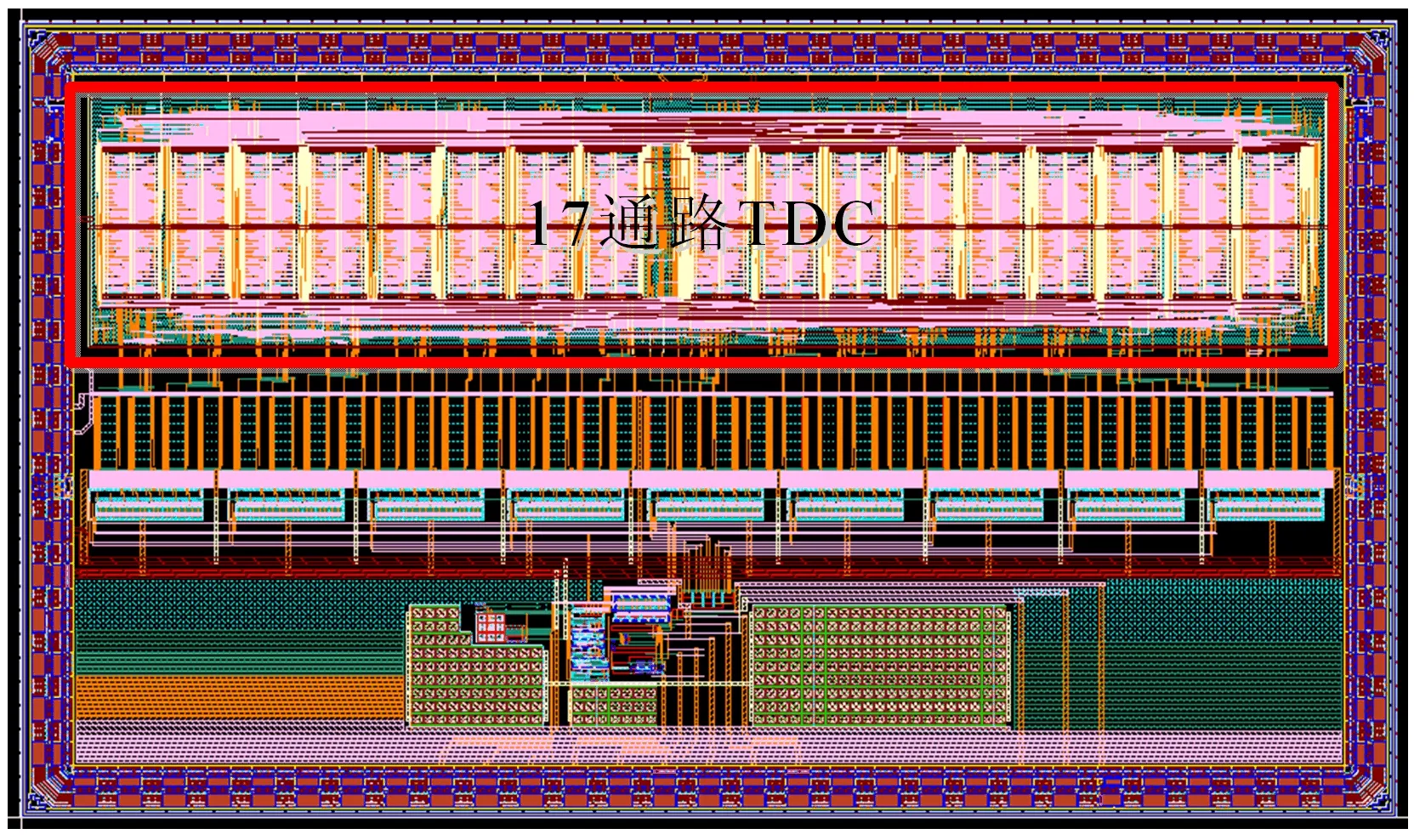

TDC的版图基于Synopsis IC Compiler 实现,流片采用的整体版图如图7所示。

图7 整体流片版图

图7中包括用于提供时钟与相位的PLL、ILO电路以及包含有校准补偿算法电路的17通路TDC系统,整体版图面积为3 600×2 000 μm2,功耗为188.8 mW。其中单个TDC电路面积仅为380×140 μm2,在1.2 V电源下功耗4.2 mW。

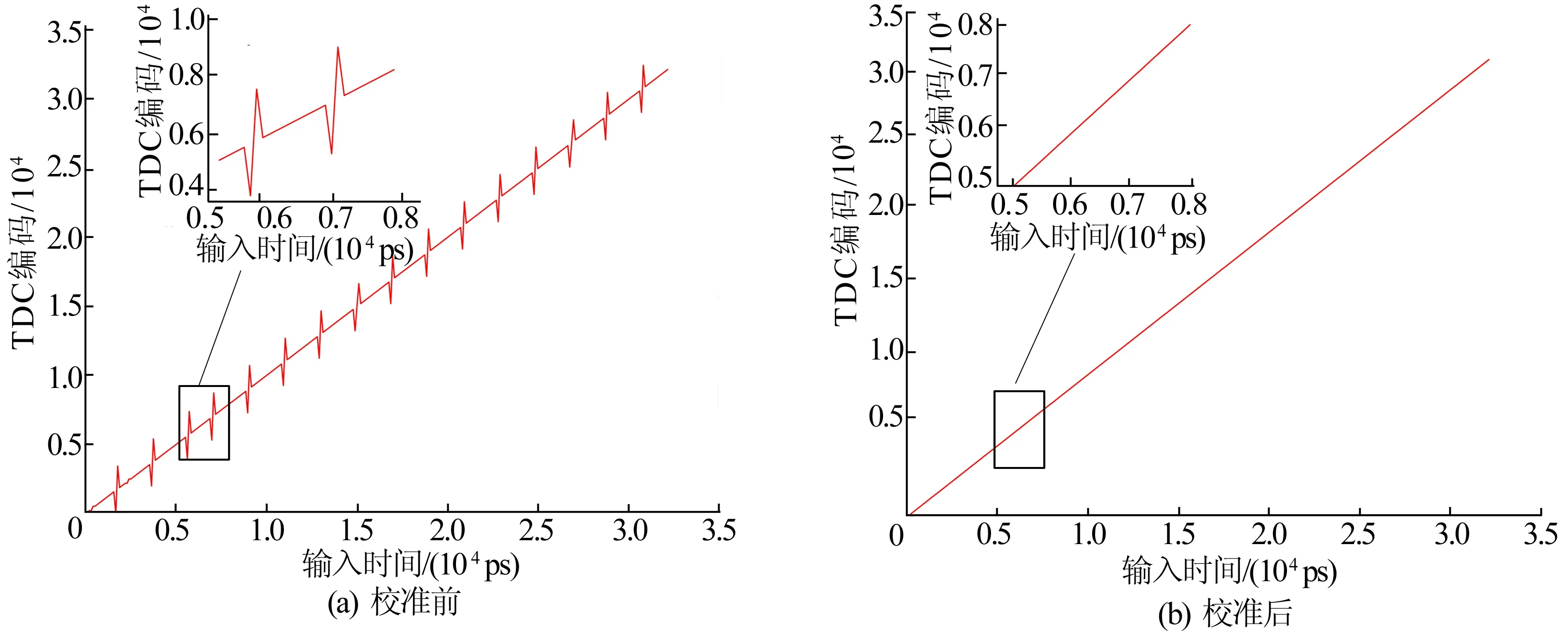

未经过延时采样和相关校准补偿与经过了延时采样及校准补偿后的TDC输入、输出特性如图8所示。设置的扫描时间为104 ps,每1.6 ns跳一个时钟周期。由此可见,经校准补偿后的TDC可有效解决跳码、失码等问题。

图8 校准前、后的TDC输入输出特性

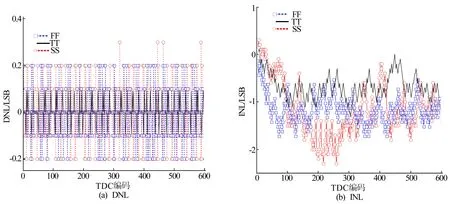

微分非线性(differential nonlinearity,DNL)和积分非线性(integral nonlinearity,INL)是衡量 TDC 线性度的重要指标,其中,DNL不超过1 LSB, 即表明不会发生失码与误码。基于3种不同的工艺角FF、TT、SS后仿真的DNL和INL如图9所示。

测试基于 XA-VCS 模拟器,在3种不同的工艺角下分别进行了测试,设置的扫描步长为13 ps,扫描时间为600 LSB,可以得出 DNL 最大值为0.3 LSB,INL 最大值为2.5 LSB,从图 9b可以看出,DNL 与 INL 曲线变化趋势趋于水平,说明采用了新型校准补偿电路的TDC具有良好的一致性。

图9 基于3种工艺角后仿真的DNL和INL

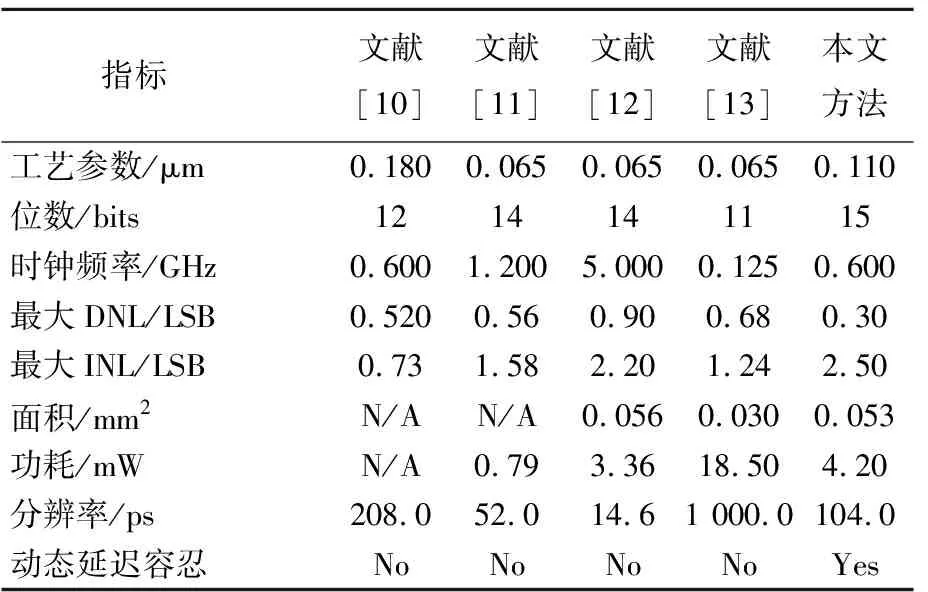

本文总结了TDC 电路的关键指标,并与同样基于计数器采样结构的 TDC 进行比较,结果见表1所列。相较他人研究工作,本文设计的 TDC 在普通工艺下,保持了良好的分辨率,在大动态范围基础上,对时钟抖动、数据亚稳态和翻转延时等引入的不确定值进行了充分考虑,具有更好的线性度。

表1 TDC性能总结与比较

3 结 论

本文提出了一种全数字的补偿校准算法及配套的电路,用于解决相位内插型TDC容易受到PVT及时钟抖动等因素带来的延时以及失配问题。该补偿算法具有很好的移植性,在采样时钟与计数器不同步的前提下,仍可以校准补偿并维持良好的线性度,电路采用CMOS 0.110 μm工艺设计并已提交流片。本文提出的校准补偿算法方案同时也为其余亚稳态敏感高速电路设计提供了参考和借鉴。