S波段6位高性能数字移相器

2023-01-02曹智慧于天新汤正波

张 飞,曹智慧,叶 坤,于天新,汤正波

(中科芯集成电路有限公司,江苏 无锡 214072)

1 引言

数字移相器[1-2]是在输入和输出信号之间的相位偏移量为特定离散值的装置。控制电压的噪声及温度变化对数字移相器的工作性能影响较小,所以数字移相器受到科研工作者的关注并得到了迅速的发展。

本文设计完成了一款S波段集成数字驱动器的6位数字移相器,移相单元的电路结构设计提升了移相精度、降低了散射系数,实现了移相器的低插入损耗和高精度。

2 移相器工作原理

移相器能够对输入、输出端口的相位做出调整,相位调整呈现出来的相移量便是移相器的性能指标,与之相关的相移精度更是关键。在外部电压控制下,移相器电路工作在不同状态,这便会使输入/输出端口的相位发生偏移,实现相移目标。本文设计的6位数字移相器的6个移相单元按45°/90°/5.625°/11.25°/180°/22.5°顺序级联,产生以5.625°步进的64种相移状态。

该移相器控制信号电压Vc为-5 V和0 V(Vc=-5 V时,Vc=0 V;Vc=0 V时,Vc=-5 V)。数字移相器中的移相单元电路采用高低通和全通网络结构。本设计中,单刀双掷开关(SPDT)采用串并联结构[3],其目的是提高控制网络之间的隔离度,减少不同状态下移相单元之间的交叉干扰,进而提高电路的移相精度。此外,为避免信号在控制端泄露,移相器栅极电路中串入了大电阻。

3 电路设计

3.1 移相单元设计

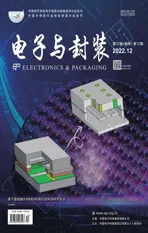

3.1.1 45°、90°移相单元

45°、90°移相单元采用的高低通电路拓扑结构如图1所示[4]。电路中采用串联大管芯开关、并联小管芯开关到地的电路结构。为在提高隔离度的同时降低插入损耗,单元最终采用3阶高低通电路结构。Vc为0 V时,Q1、Q2、Q7、Q8开,Q3、Q4、Q5、Q6关,电路工作在低通状态下,相位延迟随频率的增加而增大;Vc为-5 V时,Q3、Q4、Q5、Q6开,Q1、Q2、Q7、Q8关,电路工作在高通状态下,相位超前随频率的增加而减小。在高低通网络状态之间切换时,低通网络的相位延迟将补偿高通网络的相位超前。在宽频带内,这种结构的移相单元能实现更平坦的相位频率响应。

图1 高低通电路拓扑结构

3.1.2 180°移相单元

180°移相单元采用的5阶高低通电路拓扑结构如图2所示。如果增加并联到地的开关来提高隔离度,该单元电路的插入损耗将增加,这并不满足低插入损耗的设计要求。因此,该单元电路中不使用并联到地的开关结构。Vc为0 V时,Q9、Q10开,Q11、Q12关,电路工作在低通状态下;Vc为-5 V时,Q11、Q12开,Q9、Q10关,电路工作在高通状态下。

图2 5阶高低通电路拓扑结构

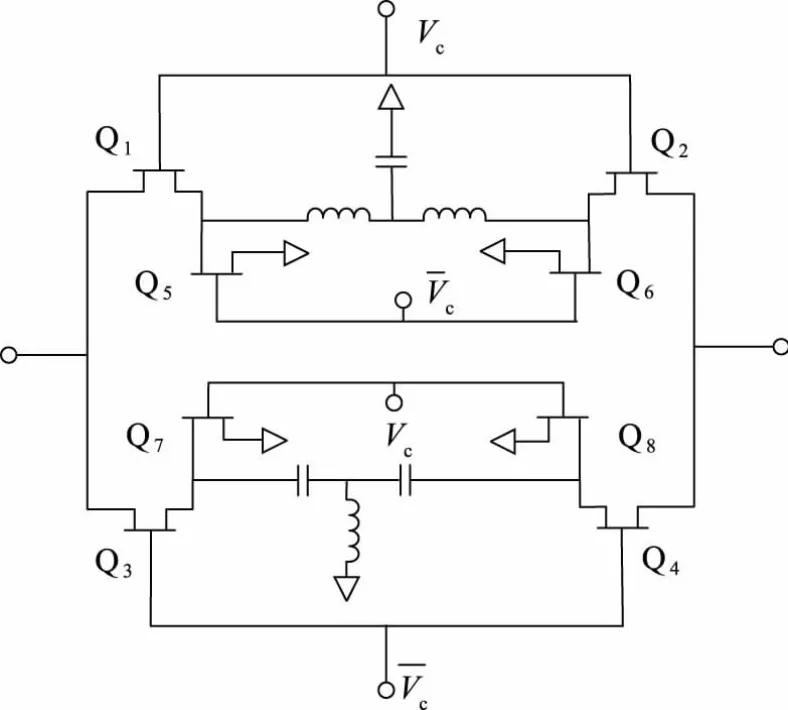

3.1.3 5.625°、11.25°和22.5°移相单元

5.625 °、11.25°和22.5°移相单元采用的T型全通电路拓扑结构如图3所示[6-8]。Vc为0 V时,电路工作在参考状态,Q13、Q14开,谐振电路由L3与Q15关断电容构成;Vc为-5 V时,电路工作在移相状态,Q13、Q14关,L1、L2与Q13形成移相网络。Q15可以提高移相状态下的隔离度,进而使电路的移相精度得到改善。

图3 T型全通电路拓扑结构

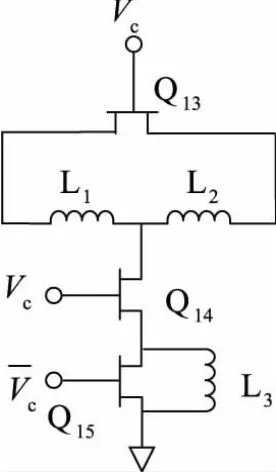

3.2 静电防护电路设计

为确保器件的可靠性,静电敏感器件必须增强抗静电能力。本文选择在输入端口搭配如图4所示的静电防护电路来增强抗静电能力。该静电防护电路可防1000 V的静电,使得芯片整体的可靠性得到加强。

图4 静电防护电路

3.3 移相精度

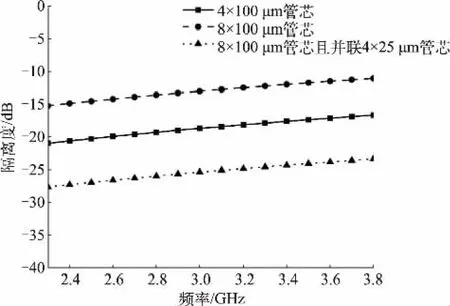

移相精度受开关隔离度影响,开关隔离度越高,移相单元电路的隔离度越高,电路的移相精度也越高。为提高移相单元的隔离度,可以使用小管芯开关串联电路结构或大管芯开关串联且并联小管芯开关到地的电路结构。3种状态下的开关隔离度(4×100μm开关管芯、8×100μm开关管芯、8×100μm开关管芯且并联4×25μm开关管芯到地)如图5所示。从图5可以看出,4×100μm小管芯和8×100μm大管芯并联4×25μm小管芯到地[4-5]2种状态下电路的隔离度更高。

图5 开关隔离度比较

移相单元电路在隔离度提高的同时,其插入损耗是在增加的。因此在提高电路隔离度的同时,电路设计还需兼顾降低插入损耗的要求。在图1所示的高低通电路拓扑结构中,相较于使用小管芯开关的电路结构,选择使用大管芯开关串联且小管芯开关并联到地的电路结构能够将泄露的信号全部接地,可提高开关隔离度,进而提高移相单元的移相精度,这种结构在降低电路的插入损耗上也存在优势。

在图3所示的全通电路拓扑结构中,当电路工作在移相状态时,在与电路其他元件无阻隔的情况下,L1、L2与Q13的寄生电容构成谐振电路。Q14可以隔离信号与Q15、L3通道,避免形成谐振,从而使电路稳定工作且提高电路在宽频带的移相精度[6,9]。

3.4 数字驱动器设计

电平转换电路、并行寄存器和输出缓冲等构成了数字驱动器。数字驱动器可以将单信号电平转换为2个电平值反相的控制电平。在数字移相器电路中,多个开关的通断状态需要用电平信号加以控制,使用数字驱动器便能够减少数字移相器控制端的数目。

数字驱动器功能的具体实现过程如下:首先,晶体管-晶体管逻辑电路(TTL)的电平信号输入后,经过电平移位至由2组增强型/耗尽型(E/D)反相放大器级联构成的放大器电路中,此时信号得到小幅的放大;然后该信号分为2路,一路进入1个E/D反相放大器的放大电路,另一路进入由2个E/D反相放大器级联构成的放大电路;最终,E/D反相放大器端口输出TTL电平的反相信号,而另一端口则输出TTL电平的正相跟随信号。

3.5 级联设计及散射优化

仿真移相单元电路时,需尽量使输入、输出的回波损耗均大于20 dB,这样在移相单元级联的时候,单元间相互影响较小,级联后对整体电路的性能影响小。此外,级联的原则是将驻波比最好的单元放置在电路两端,驻波比最差的单元放置在中间。本设计中移相器按45°/90°/5.625°/11.25°/180°/22.5°的顺序级联。由于高低通网络、全通网络单元级联间有较大的失配,电路设计中采用微带匹配结构来调和匹配,从而抑制级联散射,实现更低的插入损耗[10]。

4 测试结果分析与讨论

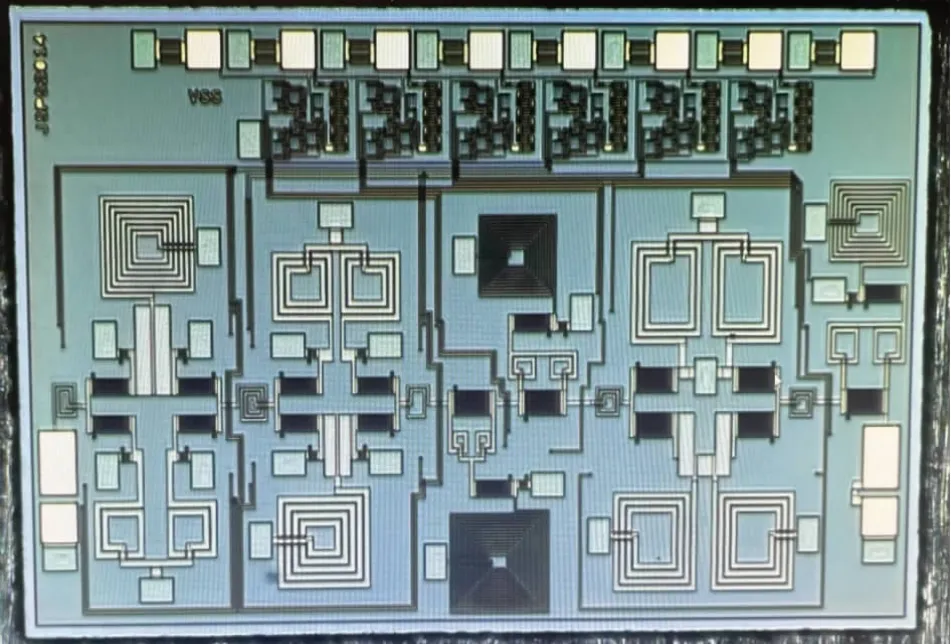

芯片设计采用0.25μm GaAs赝配高电子迁移率晶体管(PHEMT)工艺,开关的控制电压为0 V和-5 V,芯片尺寸为2.44 mm×1.52 mm。S波段6位移相器芯片如图6所示。

图6 S波段6位移相器芯片

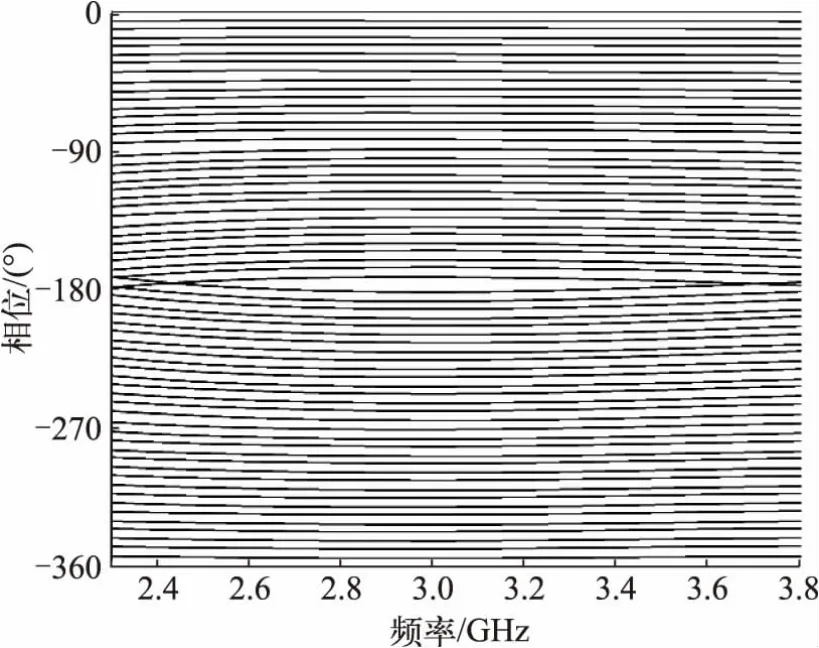

该6位数字移相器具有64种移相状态,相位状态的测试结果如图7所示。相位均方根误差(移相精度)计算公式为:

图7 移相器的64种相位状态实测结果

其中,εi是第i个相移状态时相移实测值和理想值之间的误差,N为相移状态数。移相器的相位均方根误差如图8所示,实测最大值为4°,最小值为0.667°。

图8 移相器实测与仿真的相位均方根误差

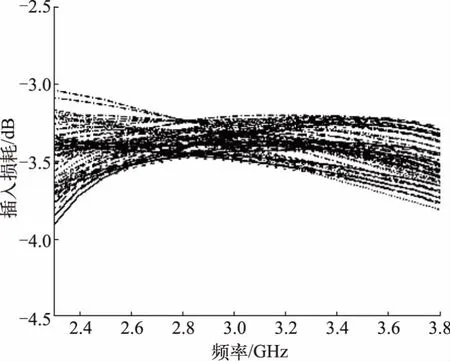

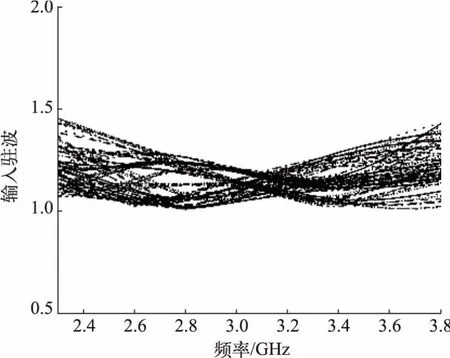

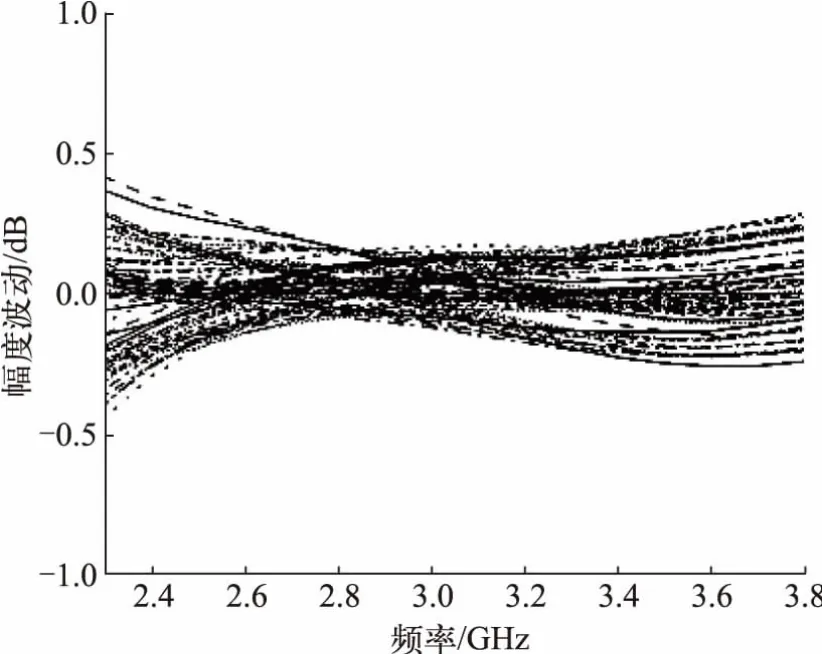

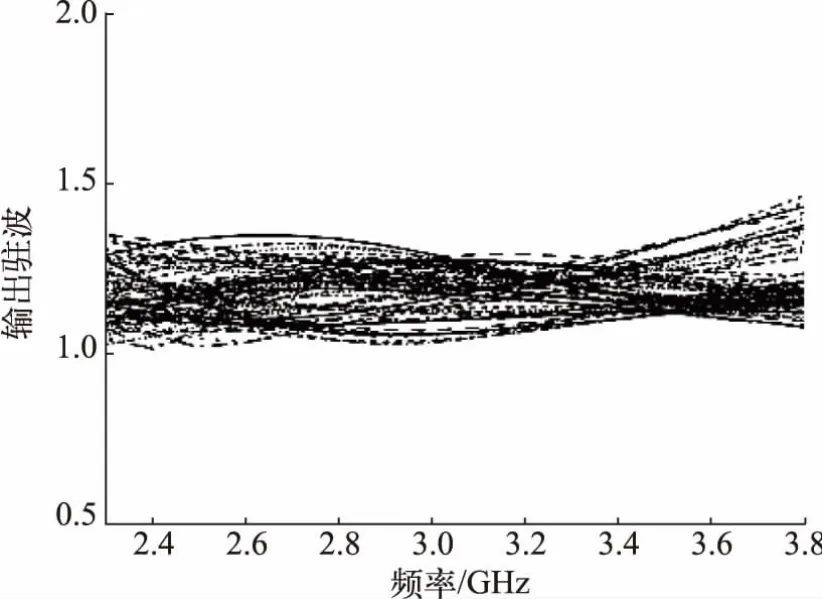

移相器的插入损耗受开关的影响,也受电路中无源器件插入损耗的影响。移相器全态(64种相移状态)下插入损耗和幅度波动的实测结果如图9、10所示。在工作频率内,其插入损耗小于4 dB,幅度波动小于0.8 dB。移相器全态下输入驻波和输出驻波的实测结果如图11、12所示。在工作频带内,其电压驻波比小于1.4。

图9 全态插入损耗实测结果

图11 全态输入驻波实测结果

本文设计的6位移相器与其他文献中移相器性能的对比如表1所示。

表1 相关产品性能对比

图10 全态幅度波动实测结果

图12 全态输出驻波实测结果

5 结论

本文设计的数字移相器工作频段为2.3~3.8 GHz,采用0.25μm GaAs PHEMT工艺,芯片尺寸为2.44 mm×1.52 mm。在工作频段内,该数字移相器最大相位均方根误差为4°,插入损耗小于4 dB,输入输出电压驻波比小于1.4。该芯片满足低损耗、高精度、小尺寸的设计和应用要求。