基于物理不可克隆函数的防御功耗分析攻击对策

2022-12-23杜浩然

杜浩然

纽卡斯尔大学 英国 纽卡斯尔 NE17RU

引言

集成电路行业大致囊括了以下几步流程:购买知识产权、内部设计、集成到集成电路设计、根据设计蓝图进行制造、进行多方面的测试,然后作为产品销售。实时协作平台有助于缩短复杂集成电路的开发周期,允许不同领域的专家从概念到建模,再到制造和售后供应进行精密交流与沟通。这种超越企业和国家的广泛合作同时带来了知识产权和商业机密的相关问题[1]。从设计到制造和测试会有多个第三方过程,这可能会泄露集成电路设计的一些基本信息。有些集成电路可能会以灰色渠道流通到市场上,较为简单的电路也会被逆向工程破解其软硬件加密手段。

相关算法安全的加密基元和协议依赖于硬件信任根来提供所需的安全性。关键的控制和通信操作也同样期望所属硬件平台能够抵御攻击。事实上情况并非如此。现在的微控制器利用“引信位”来防止任何未经授权的用户读取和修改特定部分。然而,一些设计手段能够以电子方式恢复或重置引信位,以获得操作的权限。由于基于硬件的攻击频率和破坏性能力的上升,保护硬件信任根的要求已经显现出来。

侧信道攻击是一种利用密码设备泄露的物理信息进行的物理攻击。其中,物理信息包括时序信息、功耗或电磁辐射等。这些信息是设备自发的、无意识的和被动的,所以侧信道攻击利用的是设备的外部信息,是非侵入性的。这种外部攻击可以使用便宜且泛用的测量仪器执行,使其成为硬件物理安全的实际问题。

1 研究方法和设计

侧信道攻击包括对电路物理特征的各方面监测,可以在简单的逻辑电路或复杂的集成电路设计中实现。通常大型系统的复杂分析需要在噪声消除和时钟对齐上花费大量精力。而通过观察PUF在一个相对简单的单时钟周期组合逻辑电路中的有效性,可以更轻松应对测信道攻击。

对抗功耗分析的手段之一是在不影响电路正常运行的情况下增加了一个干扰电路以提供可变的功耗,实现增幅噪声。在实验的基准测试电路设计中,通过输入外部PUF二进制数组,在组合逻辑电路中引入干扰,使得无论在晶体管层面还是逻辑门层面,通过激活额外的单元产生随机但可控的额外功耗,实现干扰功耗分析的目的。

1.1 测试平台

实验测试平台是一个8∶1复用器。该复用器包含8个输入端口、3个选择端口和1个输出端口。8个输入端口为输出端口提供要选择的基本数据阵列,3个选择端口作为3位地址信号分配,从输入阵列中选择预定的数据,输出端口将选定的数据传输给接收器。

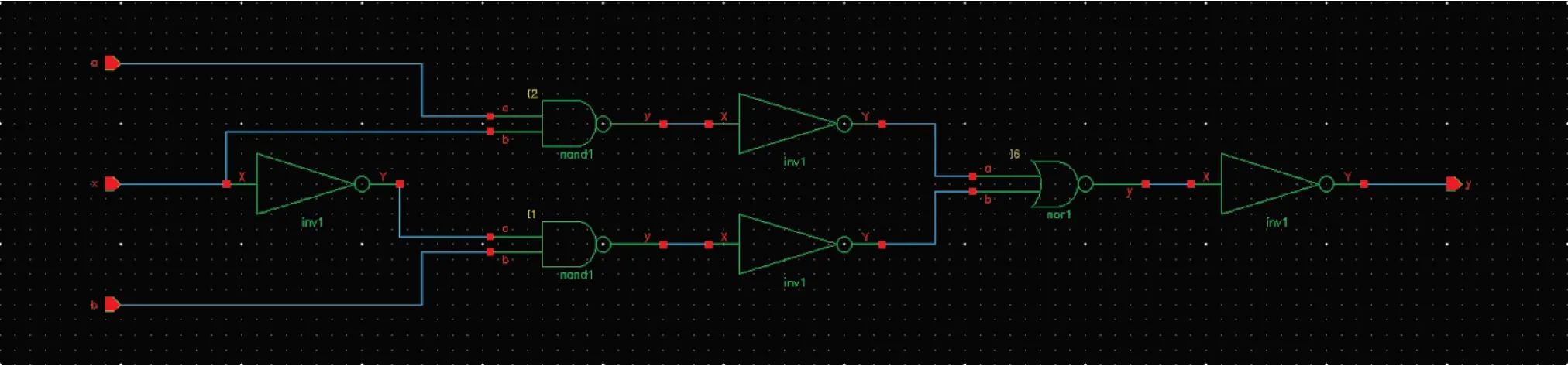

该8∶1复用器是由7个2∶1复用器连接在一起构成的。每个2∶1复用器由2个输入端口、1个选择端口和1个输出端口组成。2∶1复用器可以表示为。因此,2∶1复用器单元由1个或门、2个与门和1个反相器组成,其中一些被更常用的NAND门和NOR门取代。电路图如图1。

图1 2∶1复用器的原理示意图

1.2 基准测试电路

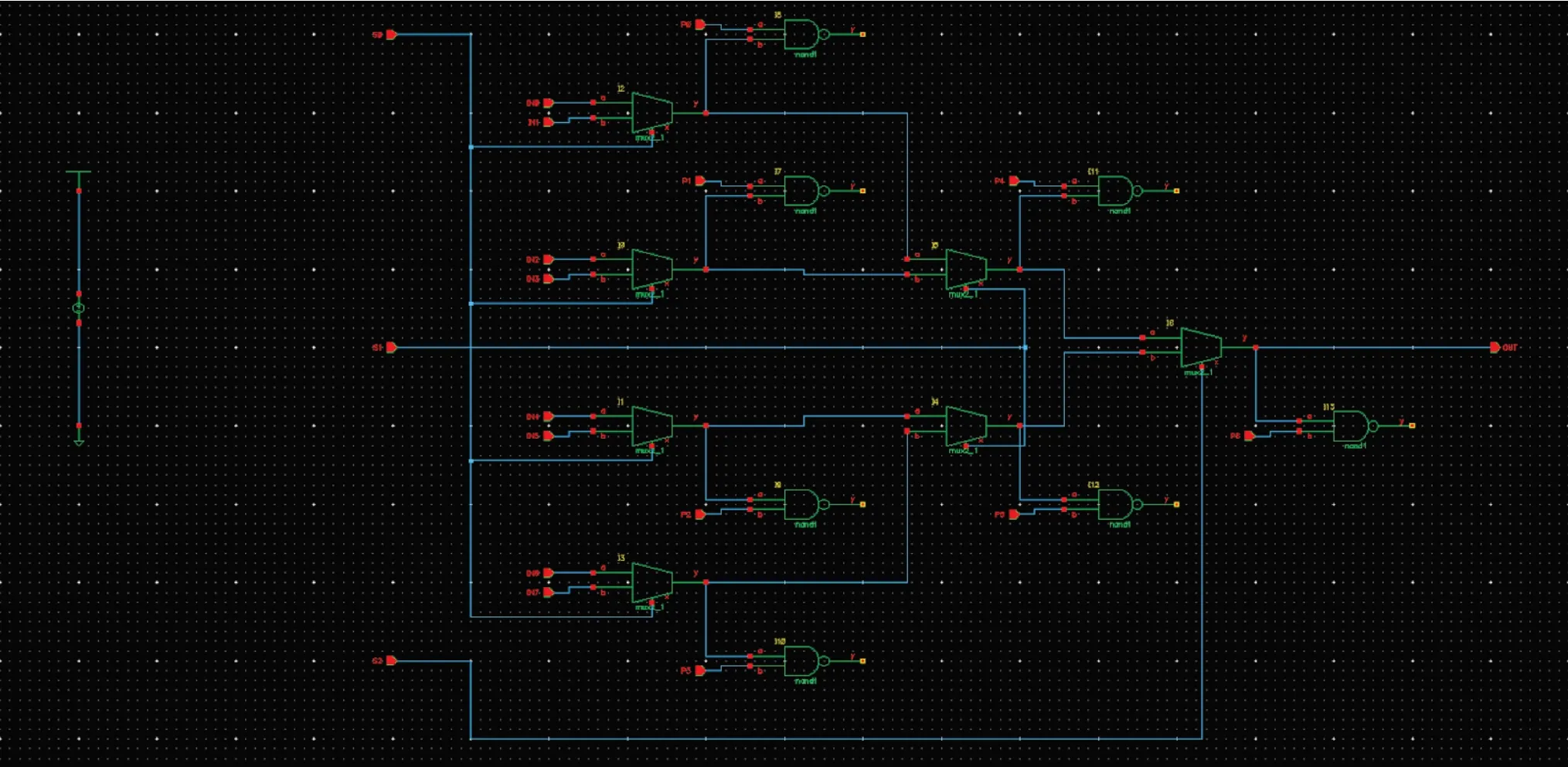

该基准测试电路是基于测试平台增加一个可以被外部PUF可控并干预的电路。其中外部PUF输入由哈希函数生成的外部随机数组所取代以在模拟中实现相似功能。利用PUF输入信号激活一些晶体管可以产生一定程度的干扰,而不改变电路的输出。它的影响会以弱相关的方式出现在电路的运行中。因此,一些由内部运行信号和外部PUF输入同时控制的逻辑门将有效地产生一些功耗层面的变化和不确定性,以干扰功耗分析,见图2。

图2 基准的示意图设计

1.3 实验设置

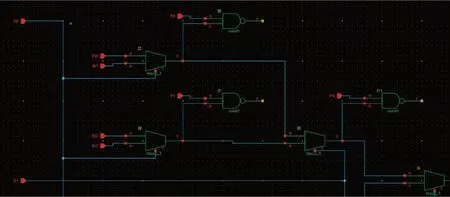

在本实验的设计中,模拟软件从测试平台的电源负极读取电流波形。该电路采用稳定的直流电压输入,其电流变化直接反映功耗变化。由于有8个数据输入端口和3个数据选择端口,所以有组可能的输入组合,这将会让分析工作不堪重负。作为替代,选择第二级多路复用器 “I5 ”的输出节点,只受4个数据输入端口和2个选择输入端口的影响,见图3,把组合的数量限制在。

图3 来自基准的目标电路的设计原理图

输入方波信号S0、S1、X0、X1、X2、X3的运行周期为2ms,4ms,8ms,16ms,32ms,64ms,128ms。为了避免电路中任何潜在的延迟,整个模拟流程被设置为运行130ms。

实验划分为两个部分,PUF针对SPA的防御和PUF针对DPA的防御。SPA部分对无干扰基准测试电路和有干扰介入基准电路分别进行测量以及SPA相关分析,并比对生成的两个功耗曲线的特征;DPA部分选取一组3位数组进行DPA解析并验证其作为选择函数的可行性,随后将该数组生成的差分功耗曲线与外部PUF介入基准电路产生的差分功耗曲线进行对比。

1.3.1 SPA实验设计。SPA侧重于捕获设备在运行期间的功耗变化。物理电压差反映了数字信号的传输。在数据的传输过程中,“0”比“ 1”产生更少的功耗。使用适当准确的测量来开发静态模型,可以用于对比特流内容进行具有一定精度的合理预测。通过比较两组电流曲线之间的逐点差异进行SPA分析。如果这两个样本完全相同,则他们之间的差异曲线与x轴重叠。

干扰电路由在电路中施加额外的输入激活。三个独立的干扰端口提供了8组可能的输入。当干扰电路被干扰端口传输的数据激活时,所有的组合都在功耗曲线上反应为一个可观察到的波动。NAND门的激活与电路中的逻辑输出相关联,则干扰信号是由电路自主控制的。这些图将与原始设备生成的电流波形进行比较,以显示功耗曲线之间的差异。这种差异意味着该PUF控制的干扰电路成功扰乱了简单功耗分析。

1.3.2 DPA实验设计。DPA首先将轨迹集划分为子集,然后计算并比较每个集的平均值之间的差异。如果每个子集中的选定迹线与包含的测量值不相关,则迹线平均值的差异趋于零[2]。相反,如果测量与子集中的分区轨迹相关,则平均值功耗曲线会表现不同。随着所选样本的增加,噪声信号对于研究的影响会被削弱,而任何微小的输入输出相关性都可以被放大。典型的DPA 攻击包括以下4个步骤:

1.3.2.1 设备检测。根据设备的可访问性,使用与设备电源或地线串联的电阻器和电流探针作为测试工具,并选择更靠近受干扰或加密部分的节点以接收质量更好的信号。测量仪器一般为示波器或用于虚拟仿真的波形模拟器。

1.3.2.2 测量及收集数据。当目标在启用干扰或加密的情况下运行正常操作时,会记录功耗曲线。捕获的功耗曲线与相关加密关联以供进一步分析。调整采样率和带宽可以提高测量的效率。

1.3.2.3 信号处理。通过对齐时序来消除误差、突出显示目标信号和消除噪声,以提高信号质量。该步骤可以基于捕获数据的质量选择。

1.3.2.4 预测和选择函数生成。这是DPA最重要的阶段。选择函数通过DPA测试解释目标电路包含的信息。它用于将功耗曲线分布到子集并计算目标电路加密的状态。子集生成曲线之间的差异称为差分曲线。当从最终DPA差分曲线中观察到明显的尖峰时,选择的输出被识别为与目标设备中的数据相关。另一方面,如果推测不正确,则差值将接近0,并且选择函数的结果与状态位无关。选择函数可以是单个位的预测,如组合逻辑的输出,或者是针对多个位的更复杂的函数。将每个获得的选择函数应用于每个功耗曲线相关的干扰和加密,为下一步提供基本的电路状态预测[3]。

对于输出端的结果将根据多路复用器“I5”上输出节点的逻辑状态,将目标的功耗曲线设置为两个子集。根据计算,间隔的数量是均匀分开的,因此子集的迹线有相同的长度。通过计算每组迹线的平均功耗可以生成每个子集的功耗曲线,用一个功耗曲线减去另一个功耗曲线就可以得到一个差分曲线。差分曲线如果有明显波动,则证明干扰电路的输入与当前监视的节点具有相关性,可作为破解电路加密的选择函数。

最后阶段是应用并验证以上选择函数的有效性,以作为攻破相似电路加密系统的途径[4]。受制于模拟软件对PUF的有效模拟,模拟过程中PUF将被一个外部产生的哈希函数所取代。该哈希函数通过特定的输入将返回一个固定长度的哈希值和d.H.代码,模仿了PUF单元在生产时的“部分固定,其余随机”的特征。将该数组输入到干扰电路得到功耗曲线,经过前述的DPA流程,验证其干扰功能的有效性,并对比该输入产生的差分曲线与选择函数差分曲线的异同,反向核验之前步骤中推测的选择函数是否能够有效解码PUF驱动的相似电路。

2 测试结果

2.1 SPA实验结果

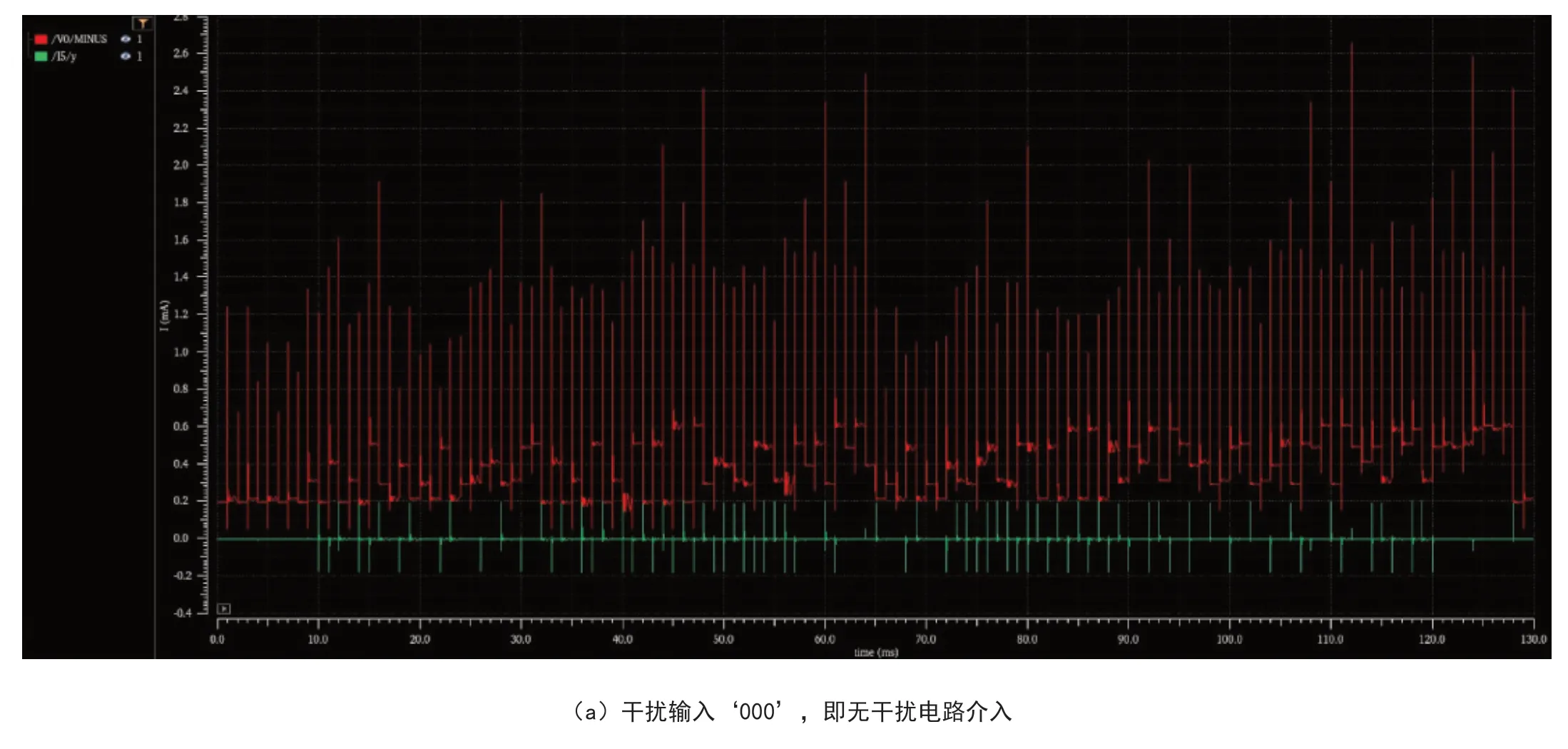

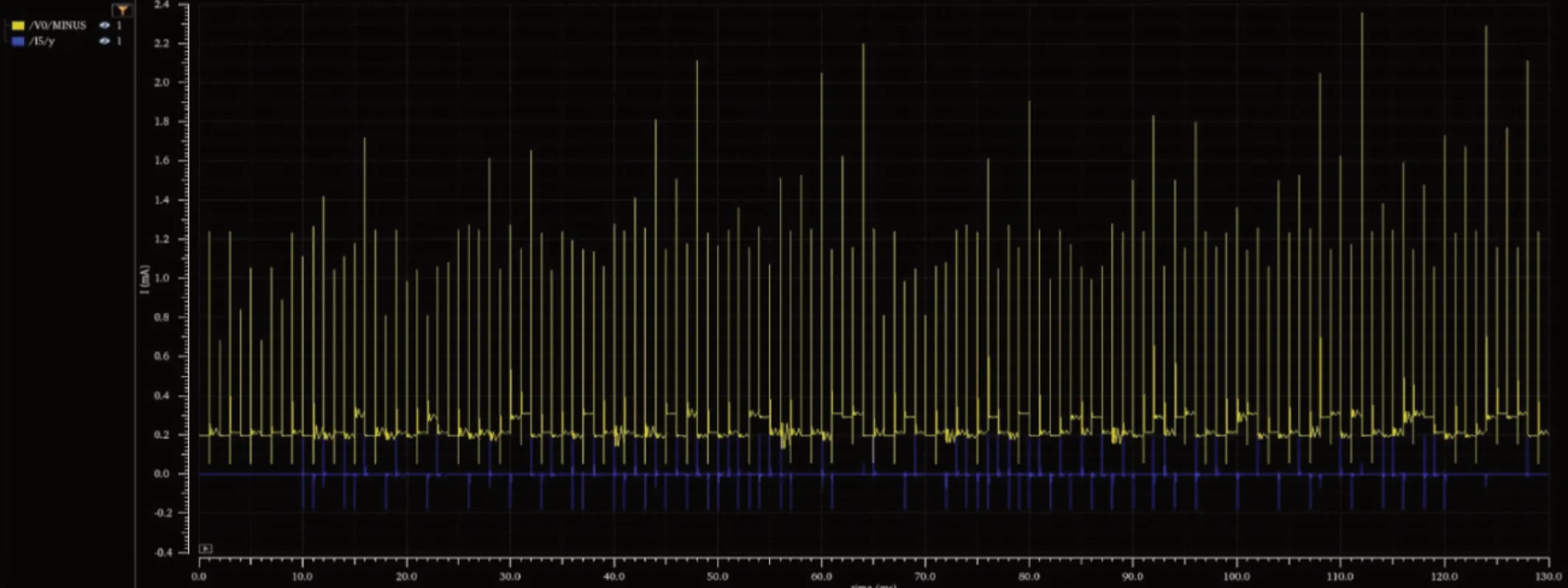

图4(a)是在128毫秒内捕获的,基于没有任何干扰介入的初始平台功耗曲线,而(b)是带有一部分干扰信号数组输入的功耗波形图。蓝色和绿色的波形表示多路复用器I5的输出。显然在两种工况下流经同一节点的电流是相同的,由此可以证明外部干扰电路不影响基础逻辑电路的正常运行。

图4 节点电流和电源电流的工作曲线

通过对比原电路的红色电流变化曲线和干扰介入电路的紫色电流变化曲线的差异,干扰电路成功地扰乱了原电路的功耗特征[5]。在原电路的功耗曲线中,输出电流可以被分为5个阶段。其中稳定状态有0.2mA,工作状态有0.3mA、0.4mA、0.5mA和0.6mA。当电路工作时,0.2mA代表没有启用多路复用器,而0.3mA到0.6mA代表工作的多路复用器组件数量(I0、I2、I5、I6)。相比之下,在启用干扰电路的情况下,工作状态的数量下降到两个,即0.2mA和0.3mA,且在0.3mA工况下可以观测到电流产生较为明显且随机的波动,加大了攻击者通过SPA以确定电路内部运行状况的难度。

2.2 DPA实验结果

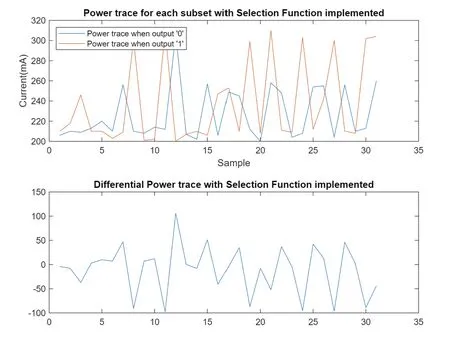

当数组‘101’作为选择函数的备选时,根据每个输入组合在目标点位产生的逻辑状态,将功耗曲线各个间隔的平均值分到‘0’组和‘1’组两个子集[6]。绘制由两个子集的功耗轨迹以及两组相互减去的差分轨迹,如图5/6所示。

图5 干扰输入为‘101’时的电源电流曲线

图6 子集的功耗曲线和差分功耗曲线

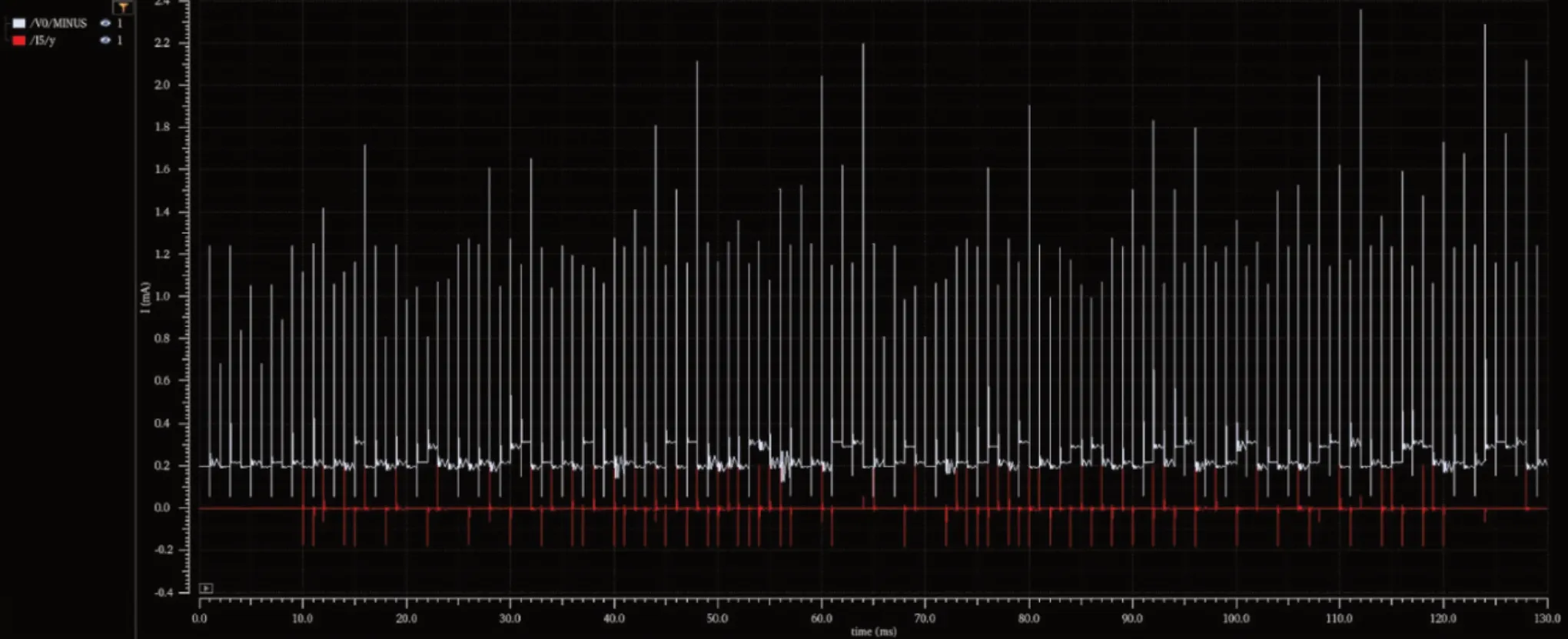

由于干扰电路的设计是基于多路复用器的正向输出,逻辑‘1’子集可以观察到非常明显的功耗波动,而逻辑‘0’子集只有微小的变化。电路的差分轨迹主要是追随‘1’子集的趋势进行的。由外部PUF通过哈希函数随机生成并应用于基准平台,电流曲线见图7。经过上述相同的操作,将两个轨迹绘制在一起,子集轨迹和差分曲线显示如下图8。

图7 节点电流和电源电流的曲线

图8 子集的功耗曲线和跟踪以及差分功耗曲线

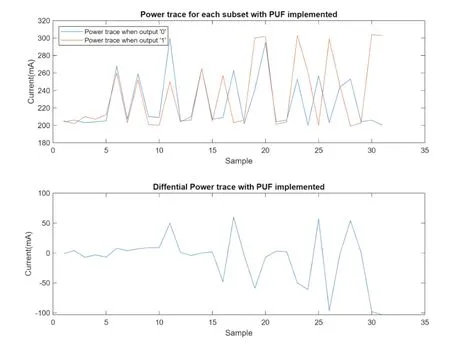

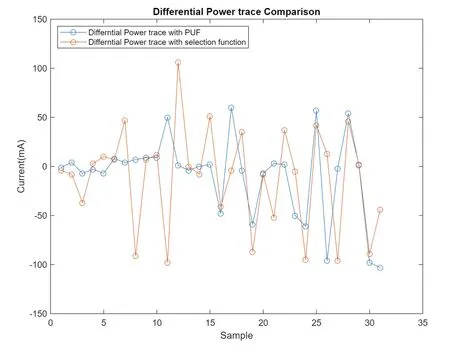

尽管与之前选择函数生成的功耗曲线略有不同,差分曲线上的波动表明:外部PUF输入控制的干扰电路产生的噪声足以阻止潜在的简单功耗分析攻击[7]。如图9,两个差分曲线之间的不匹配表明,在外部PUF干扰参与的情况下,在之前步骤中针对原型电路分析出的选择函数将无法破译这个电路。也就意味着,PUF在电路中的应用成功地阻止了基于一个样本的原型进行的差分功耗分析,从而无法用以攻破相似电路。

图9 差分功耗曲线比较

3 结论

在基于差分功耗分析和简单功耗分析的信号破解中,PUF成功地保卫了设备的数据不被解析。由于其输出的随机性,PUF与简单的干扰逻辑电路相关联,破坏了数据传输与功耗变化之间的直接联系;同时,由于其不可预测性和唯一性,攻击方无法建立一个适当的选择函数,以破解相似结构的电路[8]。

在简单功耗分析中,PUF的输入通过干扰电路生成了可控且明显的功耗差,从而降低了单迹分析的效率。由于PUF输出的随机性,即使一些电路运行噪音可以被弱化,PUF操作的干扰逻辑电路仍然以外部不可预料的模式运行,使得多组功耗轨迹对比的简单功耗分析无法有效实现。

对于差分功耗分析,通过比较选择函数和PUF外部输入产生的功耗波形,可以观察到:即便是在较为简单的组合逻辑电路中采用三位的外部输入用以激活干扰信号,PUF的唯一性仍然会使破解单个电路对应不同的选择函数。这表明,在实际应用中,面对更为复杂的电路设计以及更多数位更为复杂的PUF单元,无论攻击者在一个特定的PUF样本上付出了多少努力,都很难有机会解码另一个由PUF保护的相似电路。

以上DPA和SPA测试运行结果表明,PUF在保障简单集成电路安全方面的应用潜力。一个适当的PUF添加到特定的加密电路中,将成为该电路的独特特征,用以避免逆向工程和信号分解。这将会提供足够的知识产权保护,并鼓励开发者愿意放心地分享他们的概念和想法。这还将有利于保护具有基于组合逻辑的复杂设计。例如,某些需要大量的数据处理和传输、而对效率并不十分关心的应用领域中,PUF仅仅需要在功耗上稍作权衡,便可以以简单的设计提供了适当的硬件防御。

4 结束语

通过利用PUF的随机性和唯一性来生成真正不可预测的电路标识符或加密密钥,使得攻击不能根据一些确定的或准确定的过程进行预测,从而增加了电路的安全性。它像一把隐形的钥匙,总是在、却永远无法看到。