基于FPGA 的旋转变压器信号解码设计

2022-12-23王亚京包鹏赞陈金香王海涛程向群

王亚京,包鹏赞,陈金香,王海涛,程向群

(北京航天新立科技有限公司,北京 100143)

位置传感器是电机伺服控制系统中最常用的转子位置检测装置,常用的位置传感器有光电式、霍尔式、磁阻式、电涡流式和旋转变压器(简称旋变器)等。旋转变压器结构坚固、抗干扰能力强、响应速度快、温度适用范围宽,因此广泛应用在高温、严寒、潮湿、高震动等特殊工况下运行的电机伺服控制系统中[1-2]。旋转变压器的缺点是信号解码比较复杂,但是近年来随着旋变数字转换芯片(Resolver-to-Digital Converter,RDC)的不断发展,其被应用于旋变器信号处理,能够有效简化接口电路,缩短工程研发周期。文中通过FPGA 驱动旋变数字转换芯片AD2S1210对旋转变压器信号解码进行简化方案设计,并结合硬件驱动电路与FPGA 解码软件研制进行了实验验证。

1 旋变器测量角度原理

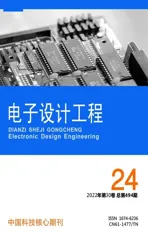

旋变器的输出电压随转子角度发生变化,旋变器由一个励磁绕组(R1-R2)和两个正交的感应绕组(S1-S3、S2-S4)组成,如图1 所示。在励磁绕组加上高频信号后,感应绕组会产生同频信号,信号幅值与转子角度相关[3]。

图1 旋变器测量角度示意图

具体函数关系如下:

式中,ER1-R2为绕组端电压幅值;ω为励磁电压角频率;θ为转子转角;k为变比。

2 硬件驱动电路设计

2.1 AD2S1210解码概述

旋变数字转换芯片可以向旋变器提供正弦波激励,接收旋变器输出的正余弦模拟信号并将其转化为数字信号[4],并且具有数字通信接口,可以很好地实现与单片机、DSP 和FPGA 等处理器的对接[5-7]。

该方案以ADI 公司推出的AD2S1210 芯片作为解码的旋变数字转换芯片,其最大跟踪速率可达2 500 r/s,最大分辨可达16 位[8],可通过接口总线对AD2S1210 进行参数配置,读取片内的角度、速度和故障等信息。

AD2S1210 的硬件驱动电路主要包含旋变器励磁驱信号动电路和感应信号接收电路[9]。旋变器硬件驱动电路设计方案如图2 所示。

图2 旋变器硬件驱动电路

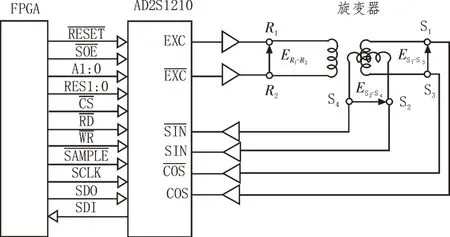

2.2 励磁信号驱动电路

励磁信号驱动电路如图3 所示。AD2S1210 直接输出的差分励磁信号EXC/------EXC 抗干扰能力和驱动能力均较弱[10],因此需要提高励磁信号的抗干扰能力和驱动能力;此外,EXC/------EXC 来自AD2S1210 内部的数模转换模块,由于D/A 转换过程会产生一定的量化噪声,因此励磁信号驱动电路中增加了滤波电路[11]。

图3 励磁信号驱动电路

图3 中励磁信号驱动电路的单端增益计算公式为:

将电阻值代入式(2),计算出励磁信号驱动电路的单端增益为1.28,因此差分总增益为2.56。

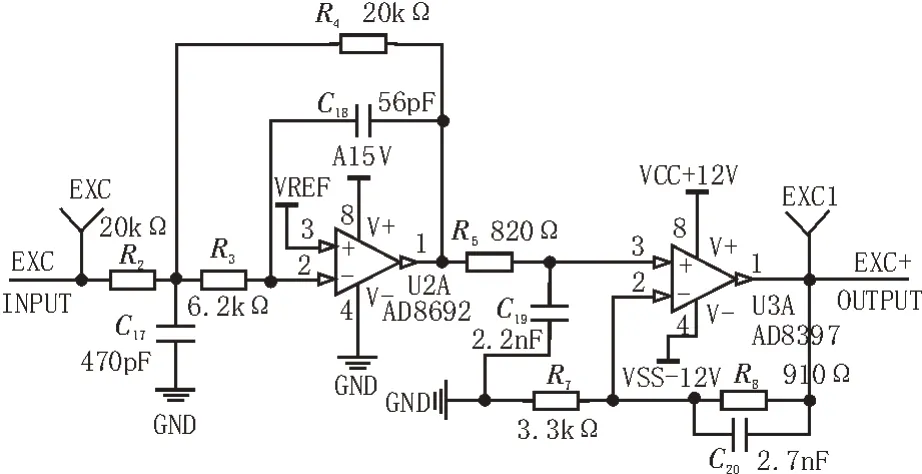

2.3 感应信号接收电路

感应信号接收电路如图4 所示。通常应用环境中,旋变器感应输出的SIN/COS 信号传输链路较长,信号传输过程中易受环境噪声干扰[12],且感应信号往往较小,其电压幅值难以达到AD2S1210 的信号输入要求(2.3Vpp~4.0Vpp)。所以,AD2S1210 感应信号接收电路设计的目的是滤除传输链路中的环境噪声,并将感应信号电压幅值调整到AD2S1210 要求的范围内[13]。

图4 感应信号接收电路

图4 中感应信号接收电路的单端增益计算公式为:

将电阻值代入式(3),计算出感应信号接收电路的单端增益为1.629,因此差分总增益为3.297。

3 FPGA解码软件设计

FPGA 信号时钟精确,适合完成时序逻辑,通常应用于一些对时序要求比较高的场合[14]。文中方案选用FPGA 对AD2S1210 芯片进行时序解码,FPGA产生读写时序并对读写数据进行处理,采用Verilog语言进行编写,不使用IP核,以保证FPGA 解码软件具有良好的移植性[15-16]。

解码软件的工作流程为:初始化完成后,读/写状态寄存器,之后以2 ms 的固定周期采集AD2S1210的角度位置数据。解码软件设计采用模块化的设计思路,其关键功能模块有AD2S1210 初始化配置模块、AD2S1210 数据写入模块及AD2S1210 数据读取模块。

3.1 AD2S1210初始化配置模块

初始化模块的功能是完成AD2S1210 上电复位和采样锁定时序。电路上电后,初始化模块启动,AD2S1210 的复位信号由FPGA 输入,复位信号需要持续保持低电平,直到AD2S1210 的供电电压VDD达到额定值(4.5~5.5 V)。

查询AD2S1210 芯片手册可知,VDD达到额定电压后,复位保持时间tRST至少为10 μs;而采样锁定时间tTRACK和AD2S1210 位置输出分辨率有关,设计中设定该分辨率为16位,则tTRACK时间不少于60 ms。如果以上两个时间不正确,会导致AD2S1210 指示位置错误或无法正常工作[17-18]。

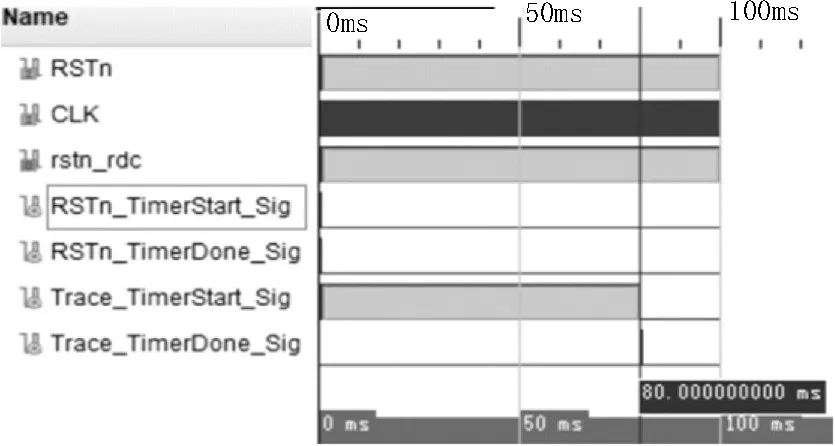

在FPGA 中编写AD2S1210 初始化配置模块,并进行时序仿真。时序仿真如图5 所示,首先测试tRST,其值为上电零时刻到rstn_rdc 信号上升沿的时间,可观察到tRST为20.09 μs;tTRACK的值是tRST信号上升沿到TRACE 计数器完成时刻的时间,即图中两标尺间的时间80 ms。初始化tRST和tTRACK时长满足AD2S1210 芯片手册要求,复位和采样锁定上电时序正确,初始化配置模块设计合理。

图5 初始化配置模块时序仿真

3.2 AD2S1210数据写入模块

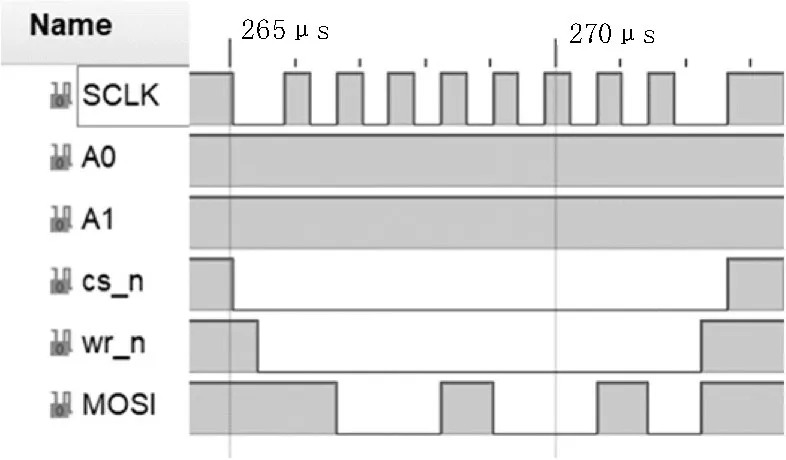

AD2S1210 数据写入模块用于向AD2S1210 的片内寄存器完成一次数据写入,以实现相关命令和配置。只有在配置模式下,AD2S1210 的片内寄存器才允许写入,因此AD2S1210 数据写入模块使能期间,A0、A1 应该都保持高电平。

AD2S1210 数据写入模块从时序上分为两个步骤,第一步写入寄存器地址,第二步写入数据。AD2S1210 数据写入模块时序仿真如图6 所示,AD2S1210 写入模块使能后,A0、A1 均置高电平,接着依次置低电平,写入寄存器地址(控制寄存器0x92),在串行时钟SCLK 的下降沿将串行数据输入总线MOSI 上的数据写入寄存器,因此下降沿时MOSI 保持稳定,寄存器的D7 位至D0 位依次写入,写入完毕依次置高电平;然后依次置低电平,再向寄存器中写入8 位的配置数据(0x7F),写入完毕相继置高,由此完成一次数据写入操作。

图6 AD2S1210数据写入模块时序仿真

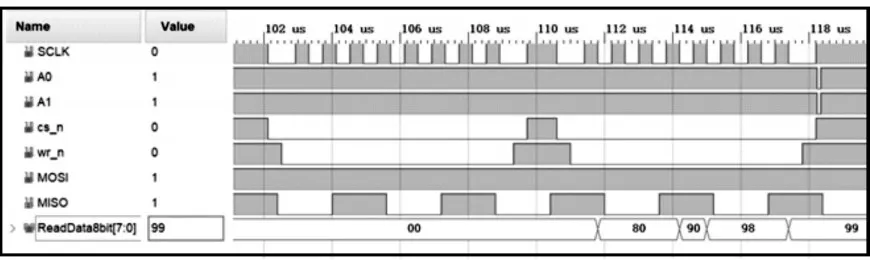

3.3 AD2S1210数据读取模块

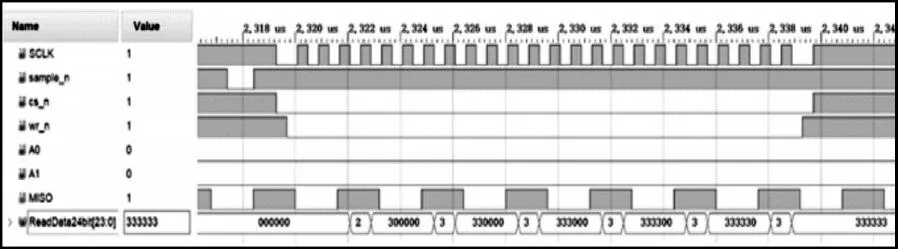

AD2S1210 数据读取模块用于从AD2S1210 完成一次数据读取。当通过A0 和A1 输入将AD2S1210设置为配置模式时(即A0、A1 均为高电平),AD2S1210 数据读取模块可读出片内寄存器中的存储数据;当通过A0 和A1 输入将AD2S1210 设置为普通模式时,AD2S1210 数据存储模块可从输出移位寄存器读出转角的位置(A0、A1 均为低电平)或者速度(A0 为低电平,A1 为高电平)数据。

在配置模式下,AD2S1210 数据读取模块从时序上分为两个步骤,第一步写入寄存器地址,第二步读出数据。配置模式下AD2S1210 数据写入模块时序仿真如图7 所示,读出模块使能后,A0、A1 均置高电平,接着依次置低电平,写入寄存器地址(故障寄存器0xFF),写入完毕依次置高电平;然后依次置低电平,在串行时钟SCLK的上升沿将寄存器内的数据从串行数据输出总线MISO 上读出,待SCLK 下降沿的MISO 数据稳定,FPGA 可进行采集,寄存器的D7 位至D0 位依次读出,读取数据完毕后,相继置高,完成一次数据读取操作。在普通模式下,输出移位寄存器为24 位宽,AD2S1210 数据读取模块读出转角的位置时序仿真如图8 所示。读取模块使能后,A0、A1 均置低电平,信号发生高电平到低电平转换且达到脉冲宽度要求后,输出移位寄存器数据更新,接着依次置低电平,在串行时钟SCLK 的上升沿将寄存器内的数据从串行数据输出总线MISO 上读出,待SCLK 下降沿MISO 数据稳定后,FPGA 可进行采集,输出移位寄存器的D23 位至D0 位依次读出,数据读取完毕后,相继置高,完成一次数据读取操作。

图7 配置模式下AD2S1210数据读取模块时序仿真

图8 普通模式下AD2S1210数据读取模块时序仿真

4 实验测试

将FPGA 解码软件注入硬件驱动电路,进行定点控制测试,测试环境参数:

1)电机型号MS24HS1P4150,保持力矩为1.28 N·m,相数为2;

2)旋变器型号TS2610N171E64,额定输入电压/频率为7 Vrms/10 kHz,额定变比为0.5;

3)AD2S1210励磁频率为10 kHz,分辨率为16位。

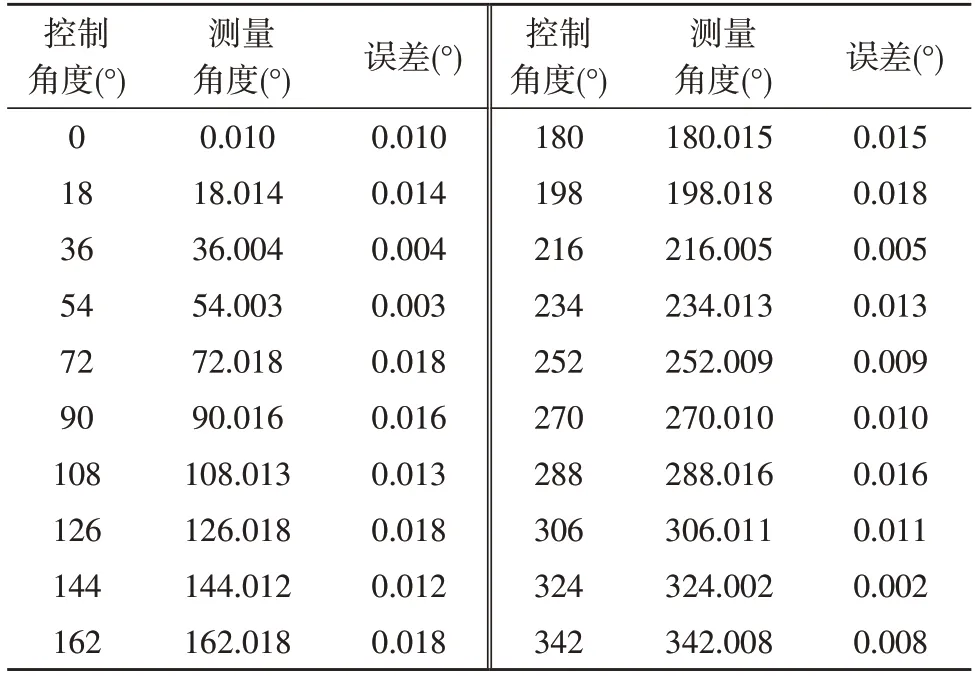

在测试过程中,控制电机转子每隔18°定点输出精确角度,记录旋变器测量角度并计算两者误差,如表1 所示。经过360°圆周测试,测量误差不大于0.02°,且在各测试点角度值示数稳定。

表1 定点控制测试记录表

5 结论

文中设计了旋转变压器解码硬件驱动电路以及FPGA 解码软件,并进行了实验验证,从实验结果来看,测量误差可控制在0.02°范围内,且角度值示数稳定。结合旋转变压器对高温、严寒、潮湿和高震动等工况的适用性,该设计方案可以应用于上述特殊工况下电机伺服控制系统中的转子位置检测。