基于千兆以太网的FPGA 远距离在线更新设计

2022-12-23文丰韩冰袁小康

文丰,韩冰,袁小康

(中北大学电子测试技术国家重点实验室,山西太原 030051)

一般情况下,FPGA 需要通过JTAG 接口,使用配套的下载线和上位机进行连接,来完成程序的更新。这种方法有很大的局限性,如一些产品的使用环境特殊,要求结构密封,这样就无法打开下载口更新程序。该文以此为出发点,介绍了一种由Flash、FPGA 和以太网组成的远距离在线更新系统。

Xilinx 7 系列FPGA 支持多重配置功能(即Reconfiguration and MultiBoot),具体划分有:主串模式、从串模式、主并模式、从并模式和SelectMAP 模式,MultiBoot 特性允许用户在不掉电重启的情况下,针对不同的功能需求,从存储于Flash 中的多个更新文件中选择其中的一个进行加载,便可实现FPGA 系统配置更新,完成对应的设计任务。这就为FPGA远距离更新带来极大的便捷性和操作性[1]。该文提出一种远距离更新方法,将待更新的配置文件编程到Flash,FPGA 将优先更新配置这些文件,实现在线更新。

1 原理简述

1.1 硬件框图

硬件设计框架如图1 所示,主要可分为FPGA 控制,以太网传输和Flash 存储,以太网选用Marvell 的88E1111 芯片,它的功能主要是把上位机下发的指令和更新程序数据传输给FPGA,FPGA 选择Xilinx公司的XC7A100T 芯片,7 系列芯片采用28 nm 加工工艺,集成度高、价格低廉、功耗控制较好。Flash 采用Micron 生产的N25Q128A,该芯片通过SPI 总线与FPGA 通信,内存大小为128 MB。FPGA 收到配置文件后,通过SPI 读写将配置文件写入Flash 指定的存储空间[2]。

图1 总体结构框图

1.2 FPGA内部处理框图

以太网接口选用TCP/IP 通信协议,进行上位机与FPGA 两者之间的通信。以太网接口在很多方面与Flash 接口存在不同,例如传输的速率和数据位宽等,因此选择加入FIFO,用来存放缓存数据以及中转位宽,FPGA 内部更新结构设计如图2 所示,由以太网接口、FIFO、SPI 接口三部分组成[3]。就传输速度来说,以太网相对更快,所以传完一整包数据后,需等待FIFO 中缓存的数据存到Flash中,再传下一包数据。

图2 FPGA处理框图

1.3 SPI接口

该文选用的SPI 协议支持的是主串模式,这种模式的优点是操作简单,实用性强,占用空间小,资源利用率高。当配置FPGA 选择主串模式时,主设备选择FPGA,从设备选择Flash,SPI接口配置图如图3所示。

图3 SPI接口配置图

SPI 接口是一种高速的、全双工、同步、串行的数据总线,FPGA 通过Flash_clk,Flash_cs,Flash_datain和Flash_dataout4 条信号线来控制与Flash 之间的数据传输[5]。其中Flash_clk 是时钟信号,FPGA 通过控制Flash_clk 信号来控制通信时序。Flash_cs 的作用是片选功能,起作用时电平为低,当Flash 处于选中状态时,写入FPGA 的操作指令和数据信息就会通过Flash_datain 传输到Flash中,同时Flash_dataout 读取Flash 的信息并发送到FPGA 上。

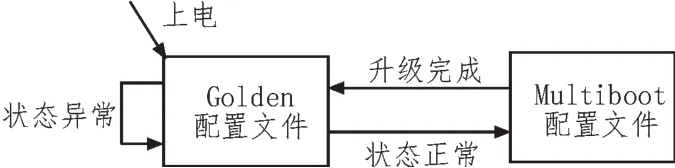

2 Flash地址空间及配置文件跳转

FPGA 远距离更新配置文件分为Golden 配置文件和Multiboot 配置文件。其中,Golden 文件远程更新时不对它操作。Multiboot 文件则是由用户定义的,用来实现系统主要功能(即FPGA 功能)的配置程序,远程更新时只对它进行操作[7]。程序重新加载切换更新框图如图4 所示。

图4 配置文件跳转框图

Flash 芯片内部地址如图5 所示。

图5 Flash芯片内部地址

FPGA 更新结束后,可以正常工作的前提:1)Flash 中指定的地址空间放置着相应的配置文件;2)Golden配置文件能正确跳转到Multiboot配置文件[8]。

Flash 内部空间的最开始部分用来存储Golden配置文件,文件内包含在线更新功能和一些基础功能。而Multiboot 配置文件包含SPI 读写及远程更新接口,以及其余功能模块,存放在指定的地址空间;最后放置状态字,目的是验证Multiboot 配置文件是否准确完整。

3 功能实现

3.1 实现流程

远距离更新流程如图6 所示。

图6 远距离更新流程

远距离更新一开始,上位机先经过以太网接口下发“擦除”命令给FPGA,等待FPGA 得到指令后,马上擦除Flash 中的数据[9],完成该操作后反馈“已擦除”状态给上位机。

在SPI 读写程序编写时,擦除时地址由低到高,写数据时地址由高到低,FPGA 加载Flash 数据时,最先检验同步字,检测正确后再加载其余配置数据。同步字在bin 文件头部,所以擦除时需先擦除同步字,避免先擦除其余配置数据由于同步字仍存在,FPGA 检测到同步字后一直等待加载,从而卡死。写数据时最后写入同步字,避免写数据时异常断电,由于同步字存在,FPGA 检测到同步字后一直等待加载,从而卡死[10]。

上位机为擦除完成状态后,就可以将需要传输的配置文件下发给FPGA,FPGA 将配置文件解析后“存入”Flash,直到配置文件传输完成[11]。

上位机下发配置文件时,由于FPGA配置SPI写数据时地址由高到低,FIFO 的半空标志应为256 字节,检测到半空标志后,进行页编程,写入256 字节数据。所以上位机发送配置文件时,首先发送配置文件最底部的256 字节数据,256 字节组成一帧,接着传输配置文件,由下往上发送数据信息,直到传输完所有数据[12]。

上位机软件发送完配置文件后,自动读取FPGA设备中Flash 的配置文件,并与下发的配置文件进行比对,如果文件内容一样,则证明下发配置文件正确,如果不一样,则提醒配置失败。

3.2 多重配置设计

多重配置特性使FPGA 能够从Flash 中的指定地址有选择地加载bit流文件,将热启动地址(WBSTAR)和内部程序(IPROG)命令嵌入到bit 流文件中。内部生成的脉冲(IPROG)启动配置逻辑在热启动地址寄存器(Warm Boot Start AddRess)WBSTAR 中指定的地址位置跳转到更新bit 流文件,并尝试加载更新文件。如果在更新文件加载过程中检测到配置错误,则会触发Fallback 加载Golden 文件。

Golden 文件存储在Flash 0 地址中,Multiboot 更新文件存储在WBSTAR 寄存器指定的地址中[13]。当WBSTAR 设置为默认值以外的任何地址值时,IPROG 会自动嵌入到bit流中。

3.3 Vivado约束文件配置

打开约束文件,将以下内容复制到Golden 文件的约束文件中并保存。

set_propertyCFGBVS VCCO [current_design](根据FPGA 连接情况进行设置)

set_property CONFIG_VOLTAGE 3.3 [current_design](根据FPGA 连接情况进行设置)set_property BITSTREAM.GENERAL.CO MPRESS TRUE[current_design](bit流压缩)

set_pr-operty BITSTREAM.CONFIG.CONFIGRA TE40[curr-ent_design](配置速度)

set_property CONFIG_MODE SPIx1[current_de sign](X1 模式)

set_property BITST REAM.CONFIG.SPI_BUSW IDTH 1[current_design](X1 模式)

set_property BITSTREAM.CONFIG.CONFI GFA LLBACK ENABLE[current_design]

(配置FPGA 失败后可跳转)

set_property BITSTREAM.CONFIG.NEXT_CONF IG_ADDR 0x0300000[current_design]

(配置跳转位置,暂定3 MB,可以根据bin 文件大小需求进行更改,但需与程序中SPI—Flash 模块设置一致)set_property BITSTREAM.CONFIG.TIMER_CFG 0x00 0F4240 [current_design](设置看门狗时间,一个时钟4 000 ns,暂设置为4 s,可根据不同PROM 设置)

同理,将上述内容中配置地址语句去掉,然后复制到Multiboot 约束文件中并保存。最后将bit 文件生成mcs 文件下载到Flash 即可[14]。

4 验证方法

4.1 上位机配置Multiboot文件正常测试

选择配置文件并打开配置FPGA,结束后,将设备断电并重新上电,观察设备是否能正常工作,若能正常工作,则代表上位机软件配置FPGA 成功[15]。更新过程中,上位机界面如图7-9 所示。

图7 擦除Flash界面

4.2 上位机配置Multiboot文件异常情况测试

4.2.1 擦除时断电异常情况测试

图9 配置完成界面

上位机软件在图7 配置文件擦除任意时刻时,将设备断电并重新上电,上位机重新单击“配置FPGA”按钮,按4.1 节的步骤进行操作,若上位机能配置FPGA,且弹出“配置FPGA 结束”提示框,则证明当Multiboot 代码配置文件被擦除后,设备能自动跳转并调用Golden 代码配置文件。

4.2.2 配置时断电异常情况测试

上位机软件在图8 配置文件配置任意时刻时,将设备断电并重新上电,上位机重新单击“配置FPGA”按钮,按4.1 节的步骤进行操作,若上位机能配置FPGA 且弹出“配置FPGA 结束”提示框,则证明当Multiboot 代码配置文件被擦除后或者未写完时,设备能自动跳转并调用Golden 代码配置文件。

图8 配置FPGA界面

经验证,两种异常情况下,设备均能自动跳转并调用Golden 代码配置文件。

5 结论

该文介绍的远距离在线更新方法,以Flash 和FPGA 主串模式配置为基础,通过对FPGA 配置流程、SPI 读写控制的研究,提出了该方案,经过实际测试,实现了远距离在线更新功能。克服了特殊环境下FPGA 程序无法在线更新的困难。对于密封结构,无法开盖的情况,在线更新程序流程简单、经济实用,使得程序更新的效率大大加快。该方法已经应用于具体设备中。另外,该方案的移植性强,如在LVDS,光纤等其他通信接口也可以很容易被应用,因此,在工程方面应用前景广阔。相比于之前的程序更新方法,为防止掉电导致更新失败,该方案加入了保护措施,进一步增加了在线更新的可靠性[16]。