基于FPGA的数字逻辑电路实验设计

2022-12-08贺雪莉

贺雪莉

(兴义民族师范学院物联网工程专业,兴义 562400)

0 引言

《数字逻辑电路》课程作为电子信息专业的必修课程之一,在电子电路专业学科人才培养中占据重要的地位。传统的数字逻辑电路实验教学多基于Logisim、Multisim等仿真工具来完成,主要培养学生重现逻辑电路和验证分析电路功能的能力,对组合逻辑电路内部的逻辑关联和电路应用分析能力培养不足。此外,随着电子科学技术的飞速发展,现阶段手工设计电子产品已经不再适应社会的需求。电子设计自动化(electronic design automation,EDA)技术是以计算机为工作平台[1],实现电子电路技术、计算机技术和智能化技术的综合应用,并以此来达到电子线路系统功能的技术手段。目前,EDA已成为电子领域的主要趋势,因此,在数字电路课程设计中引入EDA技术是数字逻辑电路实验及课程设计的教学改革方向[2]。EDA以大规模可编程逻辑器件为设计载体,来实现集成电子系统功能。而现场可编程门阵列(field programmable gate array,FPAG)因其具有运算速度快、存储容量大、扩展性强和可无限重复编程等特点,在安防及工业领域、医疗检测分析仪器、软件无线电等各个领域均有应用,是当前主流的可编程逻辑器件之一。将基于EDA技术的FPGA设计开发应用到数字逻辑电路实验课程的教学中来,通过实操实验及综合应用实验,帮助学生更好地理解并掌握逻辑门电路的结构特点和时序逻辑,结合FPGA开发板的可扩展性和可重复编程特点,让学生自主设计逻辑电路解决实际工程问题,以此培养学生的创造性,调动学生的积极性。

基于FPGA的数字逻辑电路实验设计,主要通过XC7A35T-2FFG484开发板来完成,开发板如图1所示。

开发板上集成有DDR3存储颗粒、数码管、通用按键、通用LED灯、OLED/摄像头模块、千兆以太网接口、HDMI接口和足量的扩展接口等,能够满足常规数字逻辑电路实验的设计要求。实验基于Vivado工具实现,通过Verilog硬件描述语言编写程序设计,结合Notepad++编辑器和Modelsim仿真工具来完成各项实验工程的搭建和验证分析。研究基于FPGA的数字逻辑电路实验方法具有很大的发展前景,在实验教学上具有推广的价值和意义[3]。

1 基于FPGA的数字逻辑电路实验设计规划

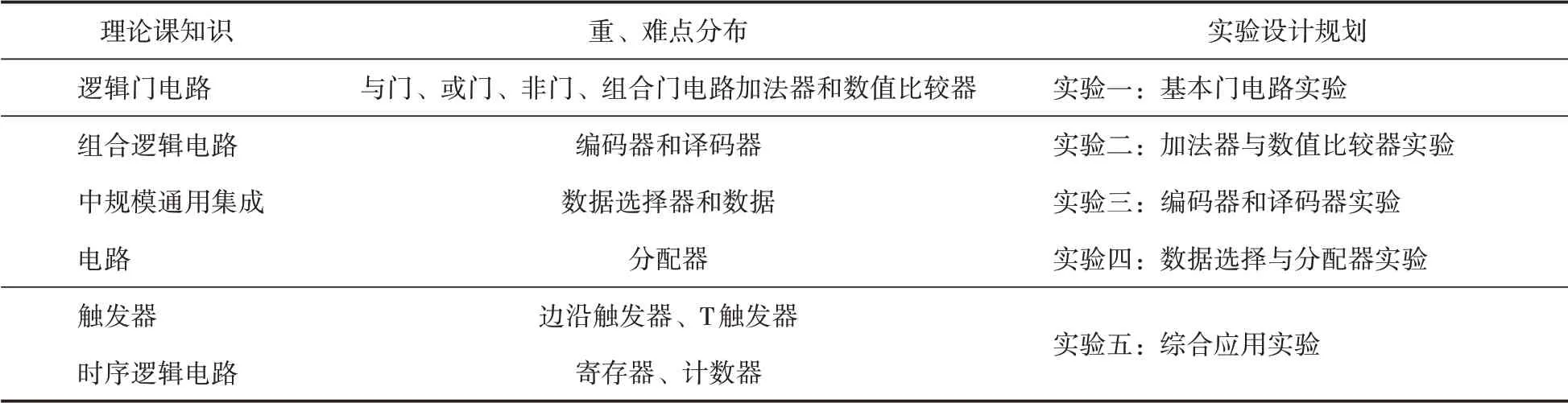

各系列数字逻辑电路教材内容基本大同小异,虽因不同专业培养方案不同,教学中的侧重点会稍有差异,但是核心知识点基本一致,主要章节分布一般为数字逻辑概述、逻辑化简、组合逻辑电路、触发器和时序逻辑电路等几个模块。无论是纯仿真的实验还是基于FPGA的设计实验,在实验教学中均是围绕重点章节展开。本文研究的基于FPGA的数字逻辑电路实验设计,主要通过和理论知识重点章节映射完成实验设计规划,具体设计思路如表1所示。其中触发器和计数器的设计实验可综合在显示译码器实验中完成,在此不再赘述,实验五综合应用实验可根据不同专业培养方案做调整,达到考查学生综合应用能力的目的即可,本文重点对实验一至实验四做详细分析。

表1 基于FPGA的数字电路实验设计规划表

基于FPGA的数字逻辑电路实验设计,实施分为四个步骤来完成,即分析、设计、仿真和实测验证。每个实验均通过分析逻辑电路的功能特点拟定设计思路,再结合Verilog硬件描述语言完成设计,接着通过仿真检验设计的逻辑性和功能性,最后通过JTAG下载接口实现工程的实测验证。

2 基于FPGA实现数字逻辑电路基础电路实验设计

本文研究的基于FPGA设计的数字逻辑电路均是基于芯片型号为xc7a35tfgg484-2达芬奇FPGA开发板来实现,考虑到图片的显示问题,文中给出的FPGA设计原理图部分为不完整的缩减图。在设计中赋值操作均通过非阻塞赋值完成,因此在FPGA设计仿真波形图显示中,结果均要比输入数据晚一个系统时钟周期。

2.1 基于FPGA设计基本的逻辑门电路

无论是组合逻辑电路、触发器还是时序逻辑电路,其最基本的逻辑元器件构成都是基本逻辑门电路。基本逻辑门电路指实现简单逻辑关系的电路[4],比如“与”逻辑、“或”逻辑和“非”逻辑。三种基本的逻辑门电路可以组成例如“与非”“或非”“与或非”“同或”和“异或”等多种符合逻辑运算,也可以搭配构成复杂的组合逻辑电路,多种不同类型的触发器电路和各类时序逻辑电路。图2的(a)、(b)、(c)图依次表示二端口“与”逻辑、“或”逻辑和“非”逻辑的中国国标符号,其逻辑表达式分别为Y=A·B,Y=A+B和Y=Aˉ。

基于FPGA设计基本的逻辑门电路可根据门电路的逻辑运算关系,通过简单的算术运算来实现。图3所示为FPGA工程的原理图。为了便于观察结果,实测中将端口输入数据data_a和data_b通过按键控制输入,三个逻辑门的输出接在LED引脚,通过LED灯的亮灭来观察逻辑门电路的输出结果状态。

图4所示为FPGA设计的逻辑门电路的仿真波形图,所有输出数据在复位信号高电平无效状态和时钟上升沿到来时刻触发有效。分析波形图可以看出,当逻辑门电路的数据以00、01、10、11、00输入时(其中“or”逻辑只有一个输入端口data_a),仿真输出结果与逻辑表达式Y=A·B、Y=A+B和Y=Aˉ计算结果一致。

2.2 基于FPGA设计加法器和数值比较器

2.2.1 二进制加法器

数字逻辑电路中的加法器分为半加器、全加器和n位加法器三大类。其中半加器位最基础的二进制加法器,只需要考虑当前位的计算结果即可;全加器在计算本位结果的同时需要考虑运算后是否产生进位问题;而n位加法器是一种全加器的级联扩展模式。因此本文研究的基于FPGA的加法器设计主要针对全加器来完成。全加器的逻辑电路图和逻辑符号如图5所示。

基于FPGA设计的全加器原理图如图6所示。设计包括脉冲产生、动态显示和全加器三个模块,输入信号A和B通过开发板的按键输入实现,运算后的sum值和进位C的值通过数码管显示。仿真结果如图7所示。全加器依次输入00-01-10-11-00的数值,对应的和值S依次显示0-1-1-0-0数值,进位C依次显示0-0-0-1-0数值,全加器功能验证完成。

2.2.2 数值比较器

数电中的数值比较器是指用来比较两个二进制数大小的逻辑电路,输入变量是两个n位二进制数值,输出变量有Y(A>B)、Y(A=B)和Y(A<B)三个状态[4]。数值比较器逻辑符号如图8所示,其中输入端A、B可以是多位二进制数。工作原理为当两个多位二进制数相比较时,应从高位到低位逐位比较,如果最高位不相等,则可立即判断两个数值的大小;如果最高位相等,则需比较次高位,以此类推,直到最低位。

基于FPGA设计数值比较器,结合开发板的数码显示模块、按键模块和LED灯模块来完成。由于本文设计用到的达芬奇Artix-7 FPGA开发板只包含4个独立按键,因此实测设计时以2 bit输入端为例完成实验,并通过LED亮灭来表示输入端按键的状态,比较器输出结果通过数码管显示。实验设计的原理如图9所示。

图10所示为数值比较器仿真波形图。其中输入数据data_1和data_2由按键控制输入,由于开发板按键是低电平有效,因此需要引入一个按键标志信号key_flag来表示正逻辑下的按键状态数值,并通过LED亮灭来显示按键通断状态;输出结果result表示,初始状态为“00”,当data_1<data_2时输出“01”;当data_1>data_2时输出“10”;data_1=data_2时输出“11”。观察波形图可以看到,2bit数值比较器的功能正常实现。

2.3 基于FPGA设计编码器和译码器

基于FPGA实现数值逻辑电路编码器的设计,主要设计二进制编码器。所谓二进制编码器,即将数值通过编码转换为计算机能够识别的二进制形式。编码器是组合逻辑电路中最基础的电路之一,基于FPGA设计编码器,只需要将编码器的输入和输出接入FPGA的相应控制管脚即可,在实操中等同于实现了按键控制LED的实验,操作较简单。本文重点分析译码器设计,对编码器不做详细分析。译码是编码的逆过程,即将具有特定含义的一组代码“翻译”出来的过程,其原理框图如图11所示。

基于FPGA的译码器设计包括译码器设计和显示译码两个模块,其原理图如图12所示。按键控制译码器输入,数码管输入端接译码器输出端,通过数码管显示出译码器的输出结果,由于本文所使用的开发板只有六个数码管,因此对于3-8线的译码器实现,需要结合2位的LED来表示数值6和7。

数码管实际上是由七个发光管组成“8”字形构成的,加上小数点就是8个,这些段分别由字母a,b,c,d,e,f,g,dp来表示,八个发光二极管有共阴极和共阳极两种接法,如图13所示,前者某一段接高电平时发光,后者某一段接低电平时发光。达芬奇Artix-7 FPGA开发板上集成有六个八段数码管,LED数码管由多个发光二极管封装在一起组成“8”字形的器件,引线已在内部连接完成,只需引出它们的各个笔划,公共电极,其原理图如图14所示。

图15所示为译码器设计仿真图,按键控制输入,按键输入的数值从000~111变化,对应的显示译码值从7~0变化,当数值为7和6时,通过LED灯的状态表示输出结果;当数值为5~0时,通过数码管的位选信号LED_SEL表示结果,并在对应的数码管上显示数值1,表示当前数码管被选通。

2.4 基于FPGA设计数据选择器和数据分配器

2.4.1 数据选择器

数据选择器是一种多路调制器,主要由地址译码和多路数字开关组成[4]。数据选择器是数字逻辑电路中常见的一种组合逻辑电路,主要功能是通过地址选通控制数据的多路输入单路输出,其逻辑框图如图16所示。当选择器有nbit的地址输入控制时,则允许的最多数据输入端为2n路,根据地址来选择可以输出的数据通路。

基于FPGA设计多路数据选择器原理图如图17所示。实验设计地址输入为3 bit,通过按键控制输入,考虑到开发板的可显示资源情况,实测分析中仅利用了4路输入数据端口,并通过开发板的LED指示信号表示当前被选通的输入端,输出端结果通过数码管显示。

图18 所示为多路数据选择器仿真波形图。地址控制端由key_flag表示,输入为3 bit,可用于实现8路数据的选通,综合考虑达芬奇Artix-7 FPGA开发板资源情况,假设数据输入端有4路数据,即iC0~iC3。分析仿真波形,当地址选路key_flag从1~4变化时,对应的输出端Z依次输出iC0~iC3的数据,数据选择器的功能得到验证。LED_SEG和LED_SEL为数码管的段选和位选信号,通过查看共阳极数码管的显示数值表可知,数码管显示数值LED_SEG依次为1、2、4、8,即为输入端iC0~iC3的数据0001、0010、0100、1000所对应的十进制数值。

2.4.2 数据分配器

数据分配器实现的即为数据选择器的逆过程,将1路输入数据信号通过地址控制端,从不同的输出端口输出数据,其原理框图如图19所示。

数据分配器设计原理和思路与数据选择器一致,不再重复描述,其FPGA设计原理图如图20所示。

3 结语

新时代高校的人才培养目标随着科技的发展不断进行着变革和更新,高素质、高技能的综合实践型人才是现今高等院校为中国特色社会主义主要输送的人才类型[5]。在数字逻辑课程中运用FPGA技术,一方面可以将理论教学知识点和实验教学的知识点实现一一映射,让学生不仅对数字逻辑电路的内部结构知其然而且要知其所以然,真正地弄懂、学透组合逻辑的知识,并能熟练地应用组合逻辑电路来解决实际问题;另一方面,FPGA作为在各个行业均能发挥重要作用的技术,懂数字逻辑电路设计、FPGA的专业人才也备受用人单位的青睐[6],让学生学习并掌握FPGA的应用也能让其在职业生涯上多一个选择的机会,这也是高校培养计算机专业学生创新能力和实践能力的一种有效方式。