Q 波段宽带功率合成倍频器的设计

2022-12-03乔欣然刘敬陈振华

乔欣然,刘敬,陈振华

(南京信息工程大学 电子与信息工程学院 电子信息技术与装备研究院,江苏 南京 210044)

Q 波段(33~50 GHz)作为毫米波频谱资源的重要组成部分,具有其独特的应用价值,比如其低频段位于35 GHz 的大气传播窗口,可以作为雷达工作频段;其中段频率(37~43.5 GHz,47.2~48.2 GHz)是国际电信联盟(ITU)规划的第五代移动通信毫米波频率范围;另外,整个33~50 GHz 还是应用于磁约束等离子体装置的有效探测频率范围[1-3]。在针对Q 波段频谱资源的开发应用中,Q 波段信号的产生是很重要的一个环节,而固态倍频已被证明是产生毫米波、亚毫米波信号的有效途径之一。实现固态倍频一般有以下几种方式: (1)基于分立肖特基二端器件的无源倍频;(2)基于分立FET 等三端器件的有源倍频;(3)基于CMOS、SiGe、GaAs、InP、GaN 等工艺的集成MMIC倍频器。其中,基于肖特基器件的无源倍频,因为器件本身相对较低的寄生参数,因而在高频率以及大带宽这两项指标上具有更大的优势[4-6]。

在倍频电路的设计中,受电路损耗以及非线性器件的寄生效应影响,倍频效率通常有一个上限,一般不超过1/N2(N为谐波次数)。在此基础上,要获得更高的输出功率,只能提高输入功率。但单个倍频管功率容量有限,输入功率超过一定限度时,会因为热聚集效应导致倍频管的物理损坏。为此,一些研究者尝试在倍频电路中使用金刚石、碳化硅等高导热材料作为电路基底,取得了较好的效果,但也很难突破倍频效率的物理极限。另一个解决方案是增加倍频二极管的肖特基结的数量,但在特定的电路中,肖特基结的数量受限于电路物理尺寸,无法增加太多,且倍频电路的功率负载平衡性会随着肖特基结数量的增加而降低,最终影响倍频效率[7-11]。

基于上述原因,“倍频合成” 为高功率倍频输出提供了一条现实可行的技术途径。通过增加倍频支路的数量,提高整个倍频电路功率容量,从而在不牺牲倍频效率的前提下提高输出功率。本文设计了一个输出频率覆盖整个Q 波段(33~50 GHz)的有源四倍频器,对电路模块的整体方案、各子电路设计过程、测试结果及性能比对进行了详细介绍。

1 Q 波段功率合成倍频器的设计

1.1 电路整体方案

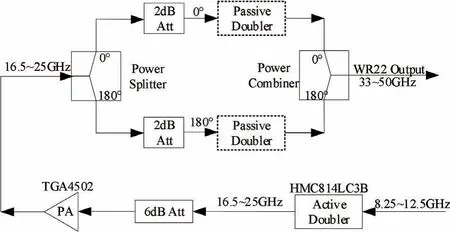

本文所设计的Q 波段功率合成倍频器采用如图1所示的电路设计方案。输入基波频率为8.25~12.5 GHz,首先使用HMC814LC3B 芯片进行有源二倍频,将输入频率倍频至16.5~25 GHz,然后采用TGA4502芯片对二倍频后的信号进行功率放大。在HMC814LC3B 和TGA4502 之间插入一个6 dB 衰减器,一方面进行功率调节,另一方面改善倍频器和放大器之间的驻波匹配,提升功率的平坦度。

图1 Q 波段有源四倍频模块原理框图Fig.1 Principle block diagram of Q-band active frequency multiplier

TGA4502 的饱和输出功率约为30 dBm,该功率电平已超出常规单个倍频电路所能承受的功率,因此使用反相功分器将30 dBm 的基波功率分成等幅反相的两路,分别驱动两个反向配置的Q 波段无源二倍频电路,从而得到两路相位相反的Q 波段输出信号。在无源二倍频之前预留2 dB 衰减器的位置,防止功率过高损坏二极管,同时进一步改善驻波,提升输出平坦度。最后,再使用反相合成器对两路反相的谐波输出功率进行同相合成,并通过WR22 标准波导输出。

下面分别对方案中所涉及的功分器以及无源倍频合成这两部分关键电路的设计进行阐述。

1.2 基于180°反相器的宽带功分器设计

由上节的设计方案可知,功分器的工作带宽需要覆盖16.5~25 GHz,同时满足低损耗、高隔离、反相功分的技术特征。常规的Wilkinson 功分器工作带宽有限,需要通过构建多级功分结构来扩展带宽,但也会导致损耗的增加。而悬置带线结构因具有低损耗、弱色散、宽频带的特点而应用广泛[12],图2 所示为基于悬置带线及超宽带180°反相器的功分器模型。该模型基于0.254 mm 厚的Rogers5880 基片进行设计,反相器的核心部分包括四个长度均为四分之一波长的支路以及一个180°宽带反相器。在信号沿悬置带线传输的过程中,上下带线的传输信号在金属通孔处进行交换,具有天然的相位反转功能,因而具有宽带特性。当信号从P1 输入时,信号会沿着两条不同的路径分别在P2 和P3 端口同相叠加输出,其工作带宽在相当大程度上由反相器的带宽决定。为保证两个支路的隔离度,在金属过孔间需要添加阻值为100 Ω 的隔离电阻。基于反相器设计的宽带功分器结构如图3 所示,因为在实际电路中,功分器的前后级电路均为微带形式,因此,在功分器的输入、输出端,使用宽带巴伦将平衡型悬置带线模式转换为不平衡的微带模式,以便与前后级匹配。

图2 基于悬置带线的反相器结构示意图Fig.2 Structural diagram of suspended strip-line based phase inverter

图3 基于反相器的宽带功分器结构示意图Fig.3 Structural diagram of broadband power splitter based on phase inverter

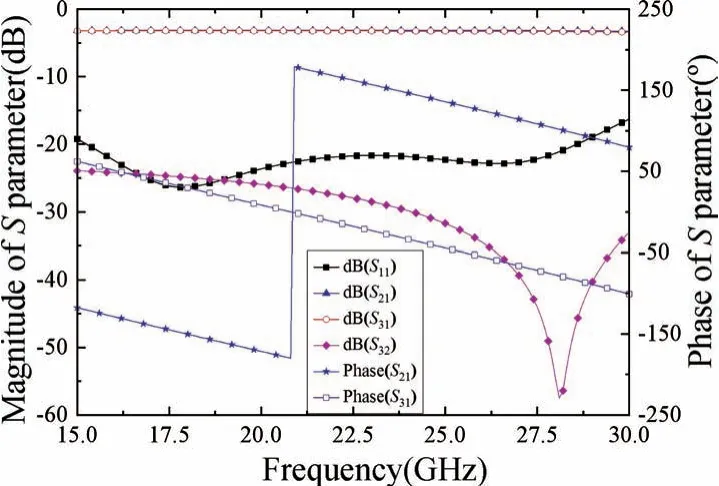

宽带功分器的仿真结果如图4 所示,可见在16.5~25 GHz 频率范围内,回波损耗优于20 dB,仿真插入损耗基本小于0.5 dB,两输出端口的隔离度大于20 dB。同时,两个输出端口的相位差维持180°±1°,能够实现宽带反相等功率分配。

图4 宽带功分器仿真S 参数Fig.4 Simulated S-parameters of broadband power splitter

1.3 无源功率合成二倍频器设计

如图1 所示,Q 波段功率合成二倍频电路是整个模块的核心部分,由两路Q 波段无源二倍频电路通过功率合成而得到,其基本原理框图如图5 所示。需要注意的是,因为前级宽带功分器及后级双探针合成器的两个支路都是反相的,结合偶次倍频的特性,需要将两个支路上的二极管反向安装,这样才能保证二极管输出的二次谐波反相,再经反相双探针实现同相合成输出。

图5 Q 波段双路合成二倍频电路原理框图Fig.5 Schematic drawing of Q-band power-combining frequency doubler

Q 波段二倍频电路包括输入低通滤波器、二极管对、输入输出匹配电路。输入低通滤波器主要功能是使16.5~25 GHz 的基波激励信号通过,同时反射二极管所产生的谐波信号以提高能量利用效率。滤波器采用高低阻抗线的形式,基于 0.127 mm 厚的Rogers5880 基片进行设计,其基本结构如图6 所示,其中低阻抗线宽度取1 mm,高阻抗线宽度取0.1 mm,通过调整高低阻抗线的长度,对滤波器通带内的驻波以及带外抑制进行优化。

图6 Q 波段倍频器输入低通滤波器结构Fig.6 Structure of the input low-pass filter of Q-band frequency multiplier

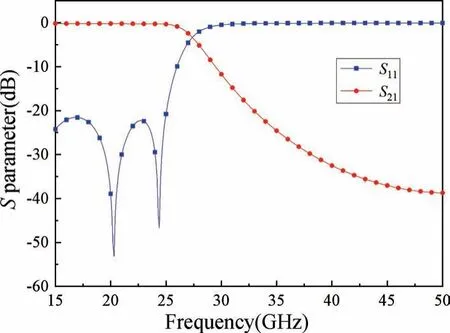

优化后的低通滤波器的仿真S参数如图7 所示,其通带截止频率为25 GHz,可保证基波信号通过,同时对33~50 GHz 的二次谐波抑制在20 dB 以上,满足预期功能。

图7 低通滤波器仿真S 参数Fig.7 Simulated S-parameters of low-pass filter

倍频功能的实现,依赖于非线性器件,一般采用肖特基二极管。本文所使用的非线性倍频二极管为MACOM 公司的MA4E1310,该二极管的非线性管芯Spice 参数如表1 所示。其中,Is表示反向饱和电流,Rs表示等效串联电阻,n为理想因子,Cj0为零偏结电容。

表1 MA4E1310 二极管主要Spice 参数Tab.1 Main Spice parameters of MA4E1310 diode

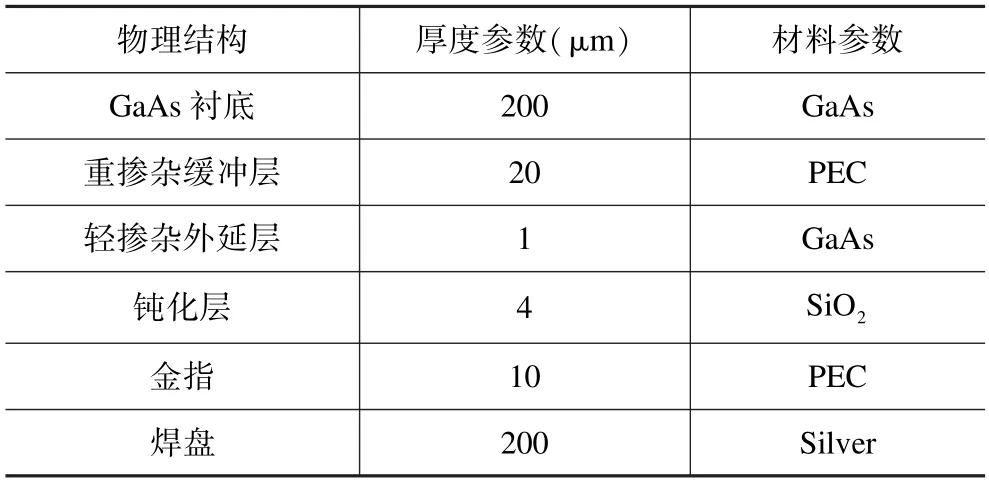

在倍频器的设计过程中,需要使用二极管的电路模型。二极管模型通常由两部分组成,一部分是非线性参数(如表1 所示),主要由肖特基接触产生;另一部分是线性寄生参数,由二极管的无源结构产生。在毫米波频段,因为波长较小,所以二极管无源寄生参数的影响变得不可忽略。对于二极管无源寄生参数的评估有两种手段,一种是通过在片测试提取S参数,另一种是通过三维全波电磁场仿真提取S参数。本文采取后者,也就是三维电磁仿真的方法提取寄生参量。这种方法需要基于二极管的材料物理参数构建其三维模型,MA4E1310 的二极管材料参数如表2 所示。

表2 MA4E1310 二极管主要结构物理参数Tab.2 Main structural physical parameters of MA4E1310 diode

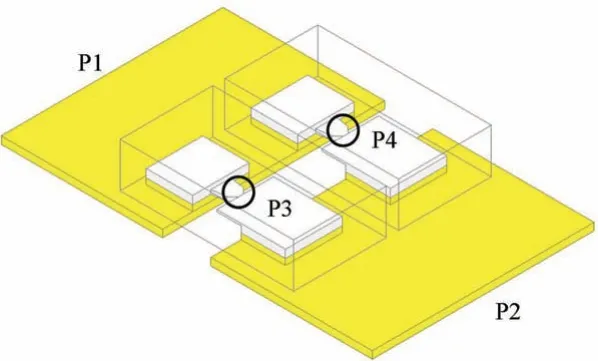

基于上述二极管的物理结构参数以及非线性管芯参数,构建由两个二极管同向并联组成的管对结构,如图8 所示,提取其整体的无源线性结构的S参数响应。图8 所示的管对结构有4 个端口,一个输入端口P1,一个输出端口P2,两个二极管端口P3、P4。仿真后可以得到一个表征其线性S参数响应的S4P 文件,结合非线性参数,可以得到二极管对的等效模型。结合前述低通滤波器的仿真结果,可以在Keysight ADS(Advanced Design System)软件中搭建倍频器的仿真电路,如图9 所示,对输入输出匹配电路进行优化。

图8 二极管对三维电磁模型Fig.8 3D-EM model of diode pair

图9 单路倍频器的ADS 仿真电路Fig.9 Simulation circuit of single frequency multiplier in ADS

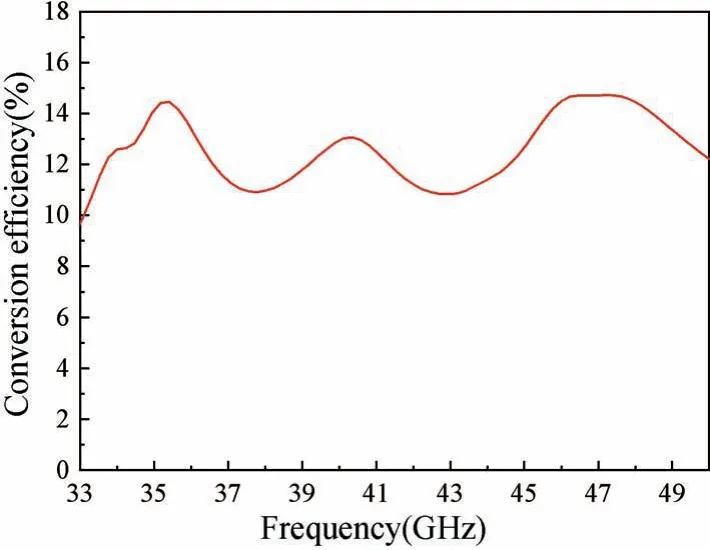

在ADS 中以倍频效率Ce为目标,对输入、输出匹配电路进行多次迭代优化,最终确定匹配电路的结构参数。并对单路倍频器的倍频效率进行仿真,仿真结果如图10 所示。由图10 可见,在所需的二次谐波频率范围内,所设计二倍频电路的倍频效率典型值达到17%。

图10 倍频器的仿真倍频效率Fig.10 Simulated conversion efficiency of frequency multiplier

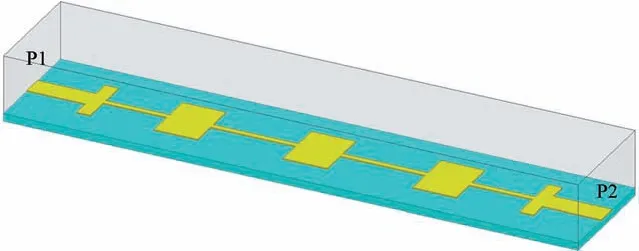

根据模块的整体方案设计,在二倍频电路设计完成后,需要对两路倍频输出信号进行功率合成并输出。本文使用波导E 面双探针结构作为合成器,其基本结构如图11 所示。

图11 Q 波段波导双探针结构Fig.11 Dual-probe transition structure of Q-band waveguide

P2、P3 端口分别接两个二倍频支路的输出端口,因为两个支路的信号本身相位相反,在波导中可以叠加合成为TE10模输出。该双探针结构虽然为无源结构,但在实际使用过程中P2、P3 端口作为输入,P1 端口作为输出。因此在仿真时,需对P2、P3 端口做等幅反相激励的设置,以反映实际工作状态,其仿真结果如图12 所示。由图12 可见,作为输入端口,P2、P3 的回波损耗在33~50 GHz 频率范围内大于20 dB,且两端口的幅度相位平衡性较好,幅度不平衡度小于±0.3 dB,相位不平衡度小于±2°。

图12 Q 波段波导双探针仿真结果Fig.12 Simulated results of Q-band dual-probe transition structure

基于上述仿真结果,将宽带功分器、倍频电路以及双探针合成器的SNP 文件导入ADS,搭建如图13所示的仿真电路,并对整个双路合成倍频的性能进行验证,倍频效率的仿真曲线如图14 所示。

图13 Q 波段功率合成倍频器ADS 仿真电路Fig.13 Simulation circuit of Q-band power-combining frequency multiplier in ADS

图14 合成倍频器的仿真倍频效率Fig.14 Simulated conversion efficiency of power-combined frequency multiplier

相比于图10 所示的单个倍频电路的倍频效率,双路合成之后的效率略有下降,但变化不大。考虑到倍频电路输出端口与双探针合成器的输入端口在级联情况下并非理想匹配的,由此导致两路幅相一致性出现偏差,进而在一定程度上影响合成效率,仿真结果是符合电路理论的。

2 实验测试

2.1 组件装配

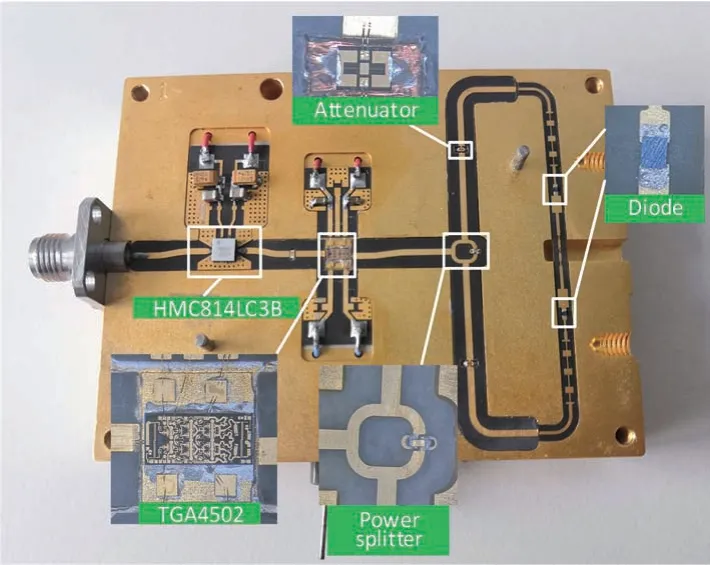

在上述方案设计以及电路仿真优化的基础上,对整个Q 波段有源4 倍频模块的芯片器件、微带电路及波导电路进行了布局以及互联设计,并完成了模块的加工与装配。模块结构件使用H62 黄铜作为材料,微带基片以及裸芯片使用金锡焊料烧结于壳体上,二极管使用导电胶粘接于微带电路,使用金丝键合工艺完成裸芯片各引脚的对外连接。装配完成的模块内部电路如图15 所示。

图15 装配完成的模块内部电路Fig.15 Assembled circuits of the developed module

2.2 实验测试

对倍频模块的测试主要包括倍频输出功率以及频谱特性这两个方面。测试所用仪表如表3 所示。

表3 测试所用仪表设备Tab.3 Instruments used in measurement

输出功率的测试框图及实际测试场景分别如图16和图17 所示。

图16 倍频模块(a)功率测试框图和(b)频谱测试框图Fig.16 Test setup of (a)output power and (b) spectrum of the developed module

图17 实验模块测试场景Fig.17 Real test setup of the developed module

信号源E8267D 产生16.5~25 GHz 的激励信号,激励功率为5 dBm,经过待测模块(DUT)放大及倍频后,产生33~50 GHz 的输出信号。根据仿真的倍频效率,该倍频模块的输出信号功率在20 dBm 左右,而N8487A 功率探头的最大可承受输入功率就是20 dBm,为保证测量设备的安全,在倍频模块的输出端接一个10 dB 的同轴衰减器,对功率进行衰减后再输入功率探头,并由N1911A 对输出功率进行显示。因为倍频模块的输出接口为WR22 波导口,所以在波导口和同轴衰减器之间级联一个波导同轴转换器(Adapter)。在对衰减器的衰减量进行校定扣除后,测量所得的输出功率如图18 所示,在33~50 GHz 的输出频率范围内,输出功率基本在17 dBm 以上,最大达到19 dBm。

图18 倍频模块输出功率测试曲线Fig.18 Measured output power of the developed module

因为N8487A 功率探头为热电偶式功率探头,功率计所显示的功率数值是功率探头在整个工作频段内所有输入信号的总功率值。为验证输入功率探头的确是倍频输出的Q 波段信号,而不包含自激、杂散等无用信号,因此,有必要对倍频模块的输出频谱进行测量。所用频谱仪E4447A 的频率测量范围为3 Hz~43 GHz,因此只能对43 GHz 以下的信号频谱进行测量。

图19 所示为36 GHz 频点的输出频谱,可见在5 GHz 带宽内,无明显杂散信号,由此也可以证明,图19 所示的功率是所需的倍频输出功率。

图19 倍频模块36 GHz 输出谱线Fig.19 Measured spectrum line at 36 GHz of the developed module

表4 所示为本文所设计的Q 波段有源四倍频电路与其他文献的倍频电路的性能比对。相较于所列文献的电路,本文设计的四倍频模块在工作带宽以及输出功率这两项指标上具有明显的优势。

表4 本文设计的固态倍频源与已报道倍频器的比较Tab.4 Comparison between the solid-state source designed in this paper and the reported frequency multipliers

3 结论

本文提出了一种工作于Q 波段的功率合成式有源四倍频器,通过整体方案设计、各功能电路仿真设计、整体性能仿真验证后,最终加工出了实验样品并进行了测试。测试结果表明,所设计的有源倍频模块,在输入频率为16.5~25 GHz,输入功率为5 dBm,直流偏置为5.5 V/2.2 A 的条件下,可以在33~50 GHz 频率范围内输出15 dBm 以上的功率,在35~50 GHz 频率范围内,输出功率在17~19 dBm 之间。输出信号频谱纯净,在实验可观测范围内,无明显杂散信号。所设计的倍频模块已成功应用于相关的实验系统中。