基于TIADC 的高速、高带宽信号采集系统*

2022-12-03余国良李居强孟祥冬孙晓冬

余国良,陆 霄,李居强,孟祥冬,孙晓冬

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

1 引言

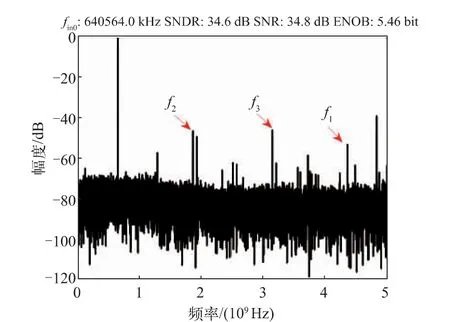

高速、高带宽信号采集系统在医疗、通信、测试仪器等领域起着决定性的作用,尤其是测试仪器数字示波器对信号采集系统的性能指标要求很高,而高端数字示波器市场一直被欧美厂家垄断。以泰克、是德为代表的欧美数字示波器公司更是推出了超10 GHz 带宽、100 GSa/s 采样率的产品。国内最新的鼎阳SDS6000 系列和普源精电MSO8000 系列产品的带宽为2 GHz,采样率为10 GSa/s。信号采集系统依赖于模数转换器(ADC),由于制造工艺和国外市场的限制,国内高性能ADC 器件匮乏。并行交替采样是提升采样率和带宽的有效办法,目前国内的研究重点是利用多个ADC 并行交替采样来制作高性能时间交织模数转换器(TIADC)[1-2],提升TIADC 校准算法的性能[3-4]。信号采集系统的研究和设计多是基于TI、E2V 等国外厂家的先进ADC 器件以获得较好的性能指标[5-6],针对国产TIADC 如何搭建信号采集系统的研究鲜有报道。

本研究利用国产TIADC 设计了一款带宽为4 GHz、采样率为10 GSa/s 的信号采集系统,为国产高性能信号采集微系统设计打下基础。

2 系统设计

2.1 系统架构

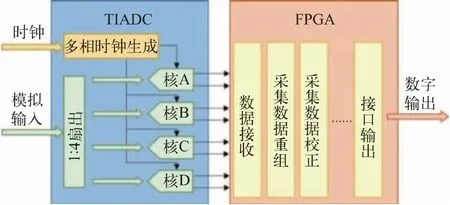

整个信号采集系统在一块16 层印制电路板(PCB)上实现,包括FPGA、TIADC、电源模块、复位和时钟模块、存储功能模块、基本模式配置模块、串口和网口等调试接口模块,信号采集系统核心架构如图1所示。

图1 信号采集系统核心架构

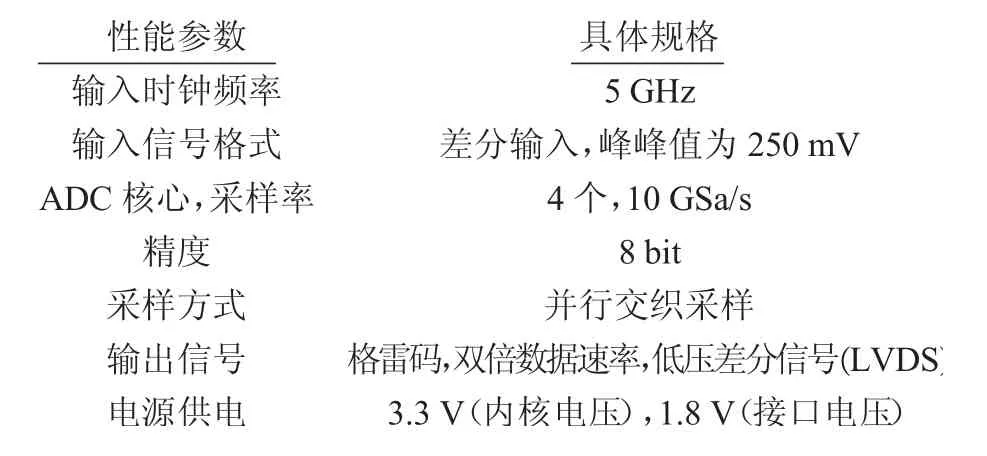

FPGA 采用的是复旦大学微JFM7 系列器件,该器件集成了功能强大、可灵活配置组合的可编程资源,适用于实现复杂、高速的数字逻辑电路。国产TIADC 由4 个并行的ADC 核阵列通过多相交织采样的方式实现高速采样,主要参数如表1 所示。

表1 TIADC 主要参数

2.2 电源模块

FPGA 器件需要提供内核电压信号VDD_1V0、内核辅助电压及LVDS VDD_1V8、输入/输出(I/O)口供电电压信号VDD_3V3、第三代双倍速率同步动态随机存储器(DDR3 SDRAM)的控制器供电电压信号VDD_1V5 和VDD_0V75。采用凌特公司的DCDC LTM4644 产生FPGA 和双倍速率同步动态随机存储器(DDR SDRAM)工作需要的5 路电源。TIADC 的内核电压信号VCC_3V3 由凌特公司的LTM4644 提供(3.3 V),其最大电流为4 A。TIADC 的数字接口直接和FPGA 的I/O 连接,I/O 电压信号AD1V8 与FPGA的LVDS 合并设计,由低压差线性稳压器(LDO)TPS74401 产生。

2.3 TIADC 时钟和信号调理电路模块

在实际工程应用中,接收机前端输出的信号多为单端信号,而TIADC 要求输入信号为抗干扰能力强的差分形式,因此需要在TIADC 前端进行信号调理。TIADC 的5 GHz 参考时钟由外部信号源提供,为了避免引入额外噪声,采用无源器件巴伦(BALUN)转化差分时钟。外部接口输入的单端模拟信号通过BALUN或者全差分运算放大器(FDA)转化为差分信号,再提供给ADC 进行采样处理。

2.4 高带宽、大容量存储功能模块

系统采样率高达10 GSa/s,精度为8 bit,瞬时工作带宽为80 Gbit/s,需要高带宽、大容量DDR SDRAM来支撑工作。选用9 片8 bit 位宽、每个引脚速率达1600 Mbit/s 的DDR3 SDRAM 颗粒,采用字长(位数)拓展的方式形成72 bit 位宽[7]、9 GB 容量的存储功能模块,其带宽高达115.2 Gbit/s,按照80%的吞吐效率来预估,可以满足80 Gbit/s 的信号采集系统瞬时工作带宽需求。

2.5 PCB 设计

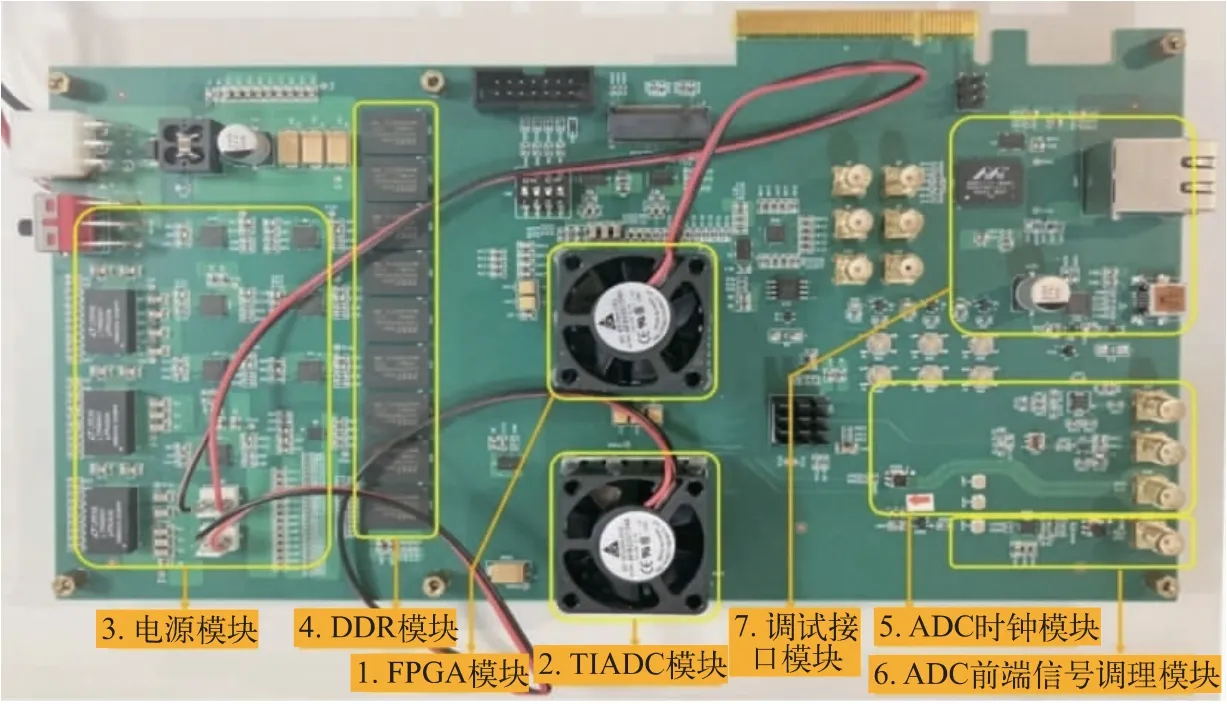

信号采集系统的PCB 设计需要注意参考地和差分信号对称[8]。理论上,在由多个ADC 器件组成的系统中,每个ADC 都有独立的模拟地(AGND)区域,并在该区域内与数字地(DGND)单点相连,这样AGND就会构成一个死区,使得杂散电流无法进入。TIADC的4 个核模拟输入信号相同,需要将4 个通道的AGND连通,器件内部不区分AGND 和DGND,使用同一个参考地,这样处理有利于信号回流。TIADC 的4 个ADC 核间存在3 种失配误差,其中时间相位误差主要来源于各ADC 核与FPGA 之间走线的长度差异。各ADC 核内和ADC 核之间的差分走线要等长,差分阻抗要一致,避免因布线不对称而引入时序偏斜。布线时要考虑器件封装的影响,做到硅片至硅片走线等长,整板PCB 实物如图2 所示。

图2 整板PCB 实物

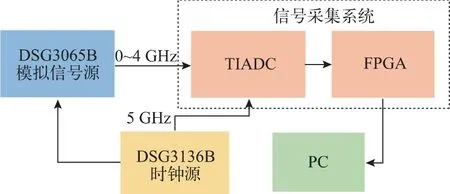

3 系统测试

信号采集系统的测试硬件平台如图3 所示。作为模拟输入的正弦波信号由RIGOL 公司的信号源DSG3065B 产生,TIADC 采样所需的5 GHz 时钟由RIGOL 公司的DSG3136B 时钟源提供。TIADC 的4个ADC 核并行交替采样得到的数据经过量化编码后传输至FPGA 高速数据接口,FPGA 截取波形数据,通过串口送至上位机,上位机用MATLAB 进行数据处理和分析,主要用信号噪声失真比(SNDR)、信噪比(SNR)和有效位数(ENOB)3 个技术指标来量化评价信号采集系统的动态性能[9]。系统测试前需要排除噪声、频谱泄露、时钟抖动和TIADC 通道失配对动态性能指标的影响。

图3 信号采集系统测试硬件平台

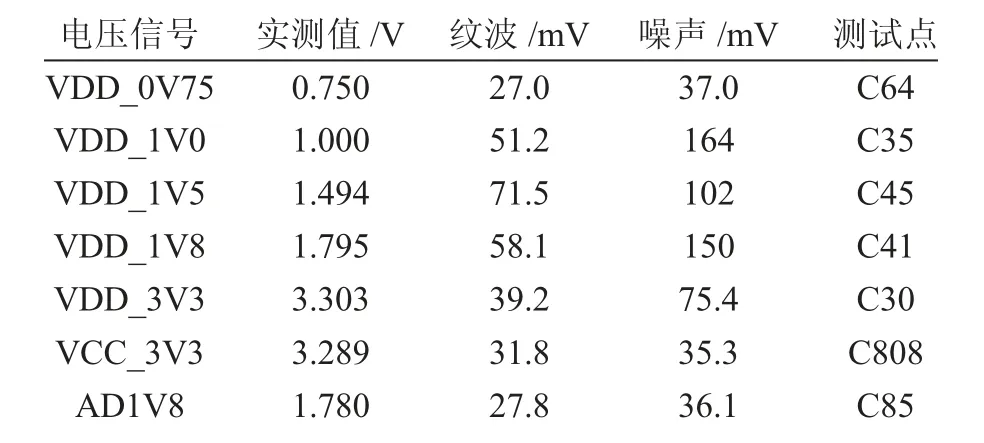

3.1 电源系统测试

为了确保FPGA 和TIADC 等模块的正常工作,避免电源系统的电压纹波和噪声影响到信号采集系统相关参数指标,用数字万用表测得电源关键点直流电压值。将数字示波器的带宽设置为20 MHz、时间刻度设置为10 ms,在交流耦合模式下测量电压纹波。将示波器设置为全带宽模式,测量电压噪声。电源电压的纹波和噪声测量结果如表2 所示,满足系统中关键器件的要求。

表2 电源电压的纹波和噪声

3.2 测试模拟信号选择

为了避免频谱泄露影响信号采集系统的性能指标,采用相干采样的方式来获取ADC 测试数据。首先对时钟源和外部模拟信号源进行锁相同步,为了避免在输入信号的频率点处发生频谱泄露,采用的输入信号频率fin=fsJ/N,其中fs为采样率,J 与N 互为素数,N为采样点数[9]。实际测试中fs=10 GSa/s,N 为32768。在0(DC)~4 GHz 内选取3 个频率点(对应的信号分别为Fre01、Fre02、Fre03)进行测试,J 选取1~32767 内和32768 互素的3 个奇数199、2099 和13109,对应的3个 输 入 频 率 点 为60.730 MHz、640.564 MHz 和4000.549 MHz。输入时钟信号Clock 频率为5 GHz,快速傅里叶变换(FFT)后的频谱中频率分辨率约为0.15 MHz。

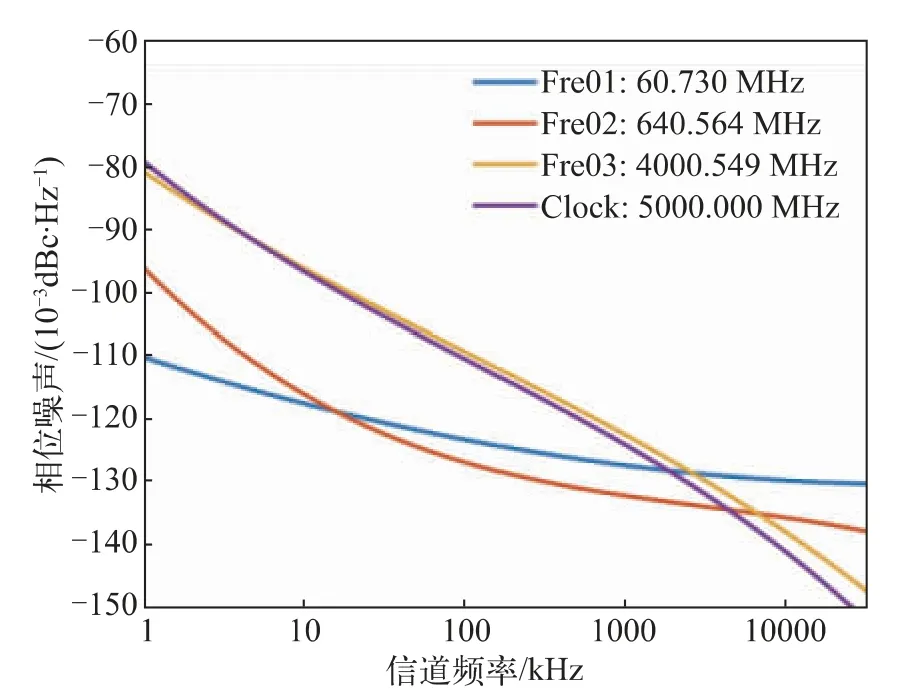

3.3 模拟信号相位噪声测试

相位噪声可以转化为时钟抖动,进而对系统信噪比产生影响。时钟和输入信号相位噪声的多项式拟合结果如图4 所示,模拟信号相位噪声在系统允许范围之内。使用信号分析仪对时钟和选定频率点的相位噪声进行测试。具体的模拟信号频率、输入端口处的功率及其在1 kHz~1 GHz 带宽范围内相位噪声的等效均方根(RMS)抖动等参数如表3 所示。

图4 时钟和输入信号相位噪声的多项式拟合结果

表3 模拟信号的参数

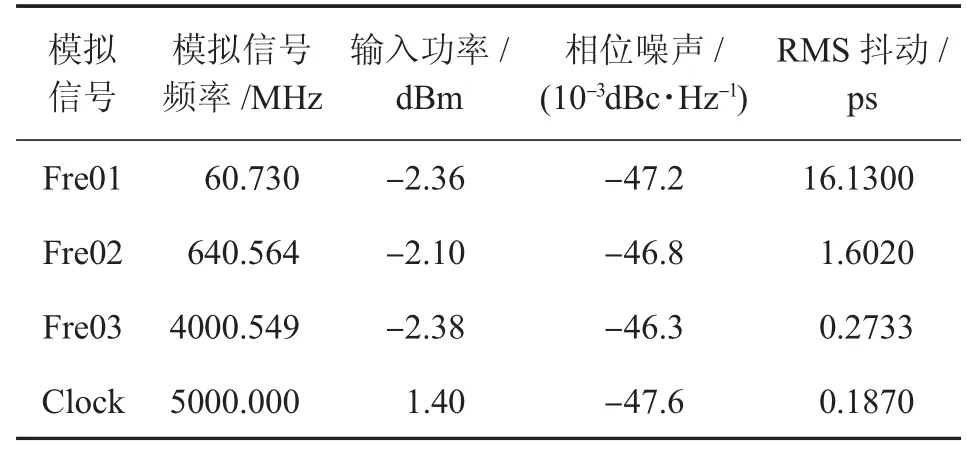

3.4 TIADC 动态性能调试

由于TIADC 的4 个采样通道不完全一致,以下3种失配误差会被引入到系统中:1)多相时钟不完全理想及同一输入信号到达各个ADC 核的延迟不一致,引起采样时刻偏离而带来的时间相位误差;2)各采样和量化过程中各个ADC 核增益不一致而引起的增益误差;3)各个通道的直流偏置不一致而引起的偏置误差。失配误差会被引入到系统中,从而使信号采集系统的性能指标恶化,因此在测试之前需要对TIADC的通道失配误差进行校准。外部输入模拟正弦信号经过TIADC 采样、量化、编码后,通过MATLAB 在时域进行了波形重现。基于最小二乘法原理对信号采集系统输出的数据进行分析,在各个输入信号的频率点处通过拟合分别得到各个采样通道的偏置误差、增益误差和相位延迟误差,完成通道失配误差的标定。根据误差标定的结果,调整TIADC 芯片相关寄存器的参数设置,依次对其偏置误差、增益误差和时间相位误差进行修正,实现4 个ADC 核的通道校准。信号采集系统校准前后得到的时域数据拼接图和频域性能分析结果如图5 所示。

图5 TIADC 校准前后性能对比

无论是模拟信号的相位噪声引起的抖动,还是TIADC 系统自身的通道间失配导致的误差,都会在输出数字信号的频谱中引入杂散频率。为了避免杂散频率的频谱泄露影响到TIADC 系统的调试和性能分析,在进行FFT 时需要对ADC 输出的数据进行“加窗”预处理。该系统选取适用于ADC 性能表征的Blackman Harris 窗来提升SNDR 的测试精度,评估信号采集系统的性能[9]。

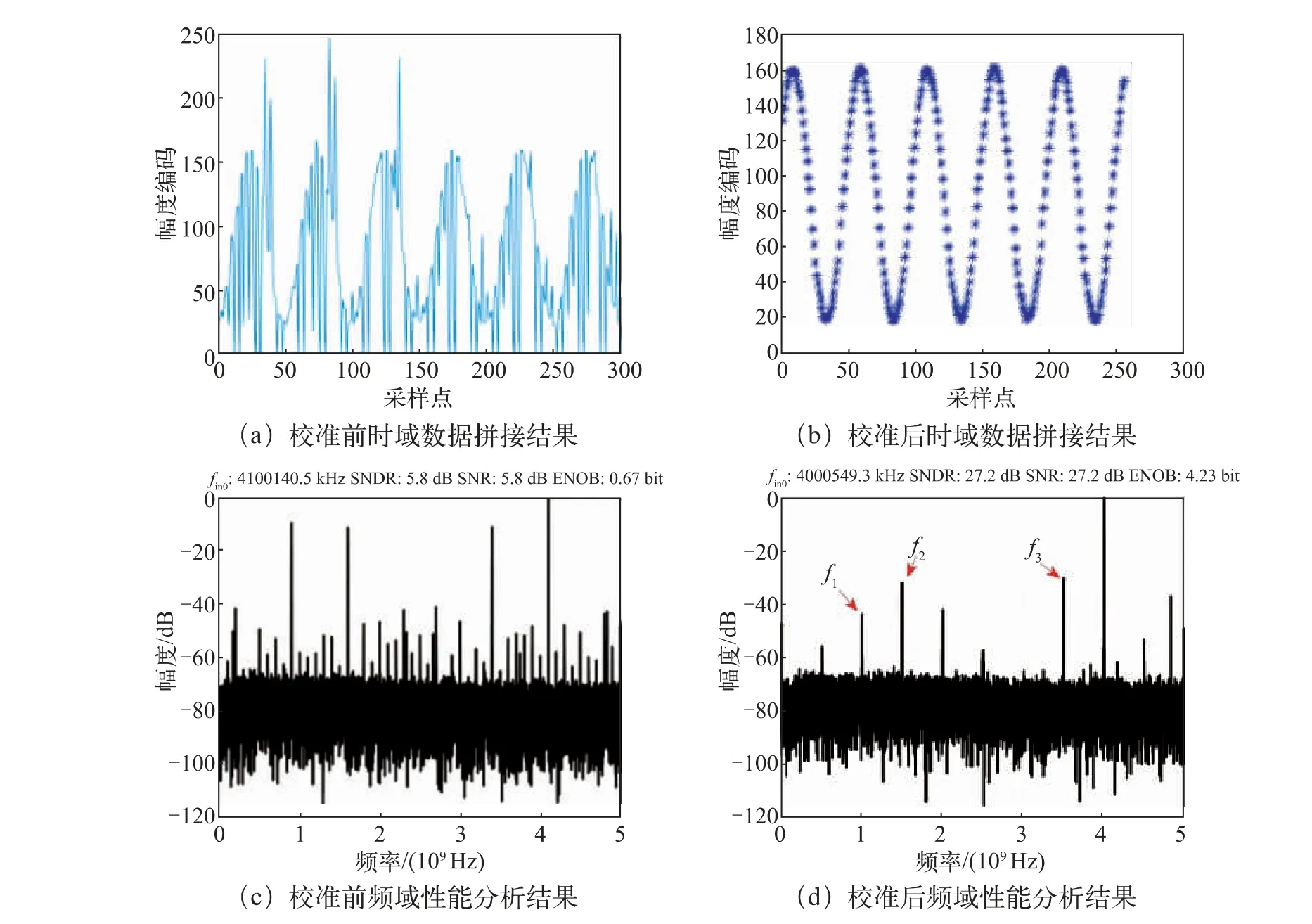

3.5 测试结果和分析

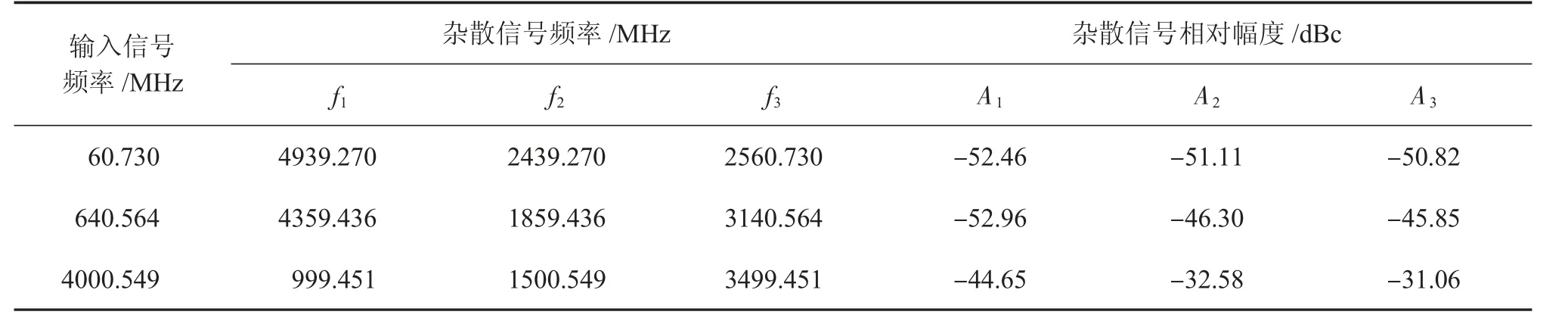

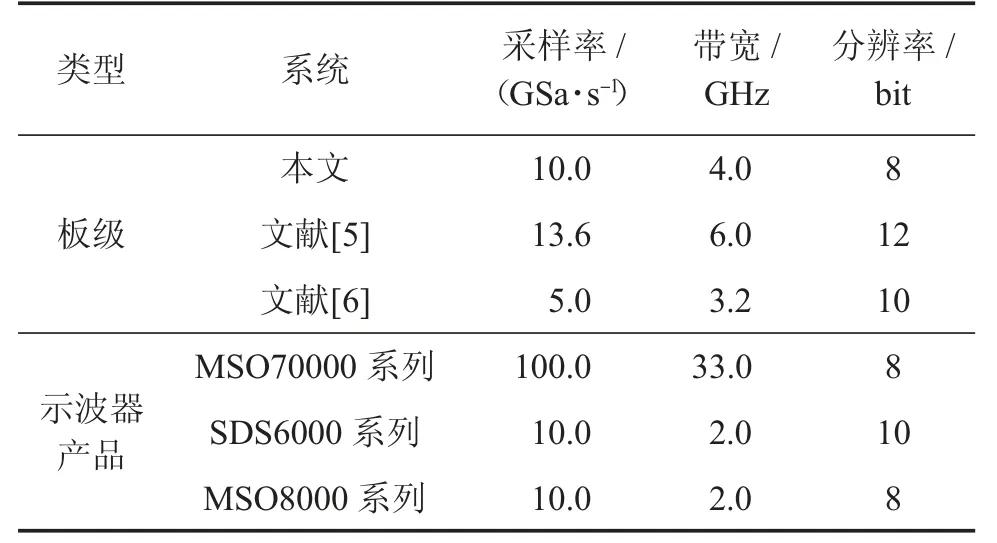

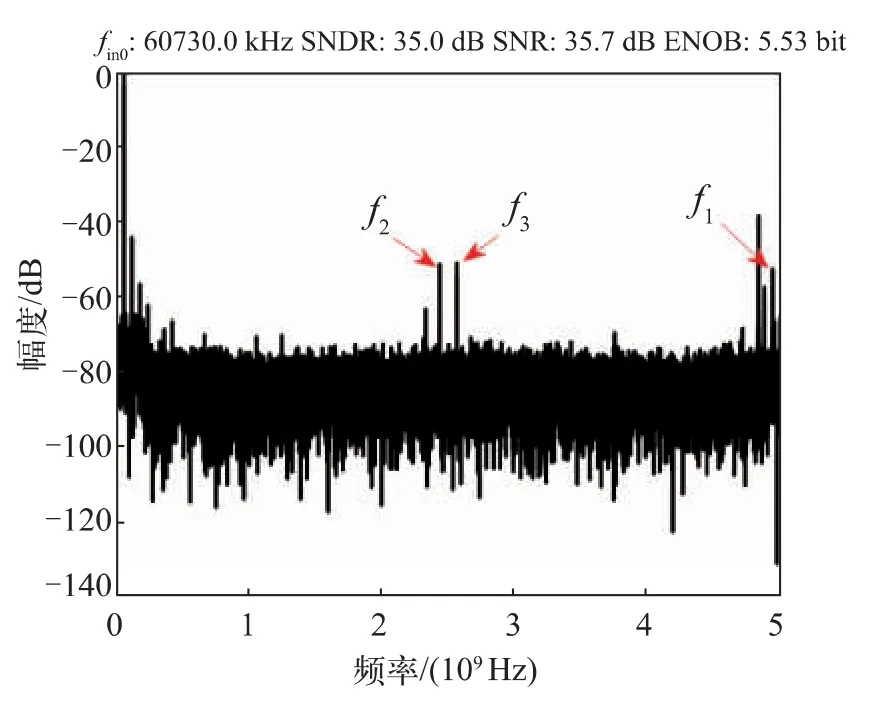

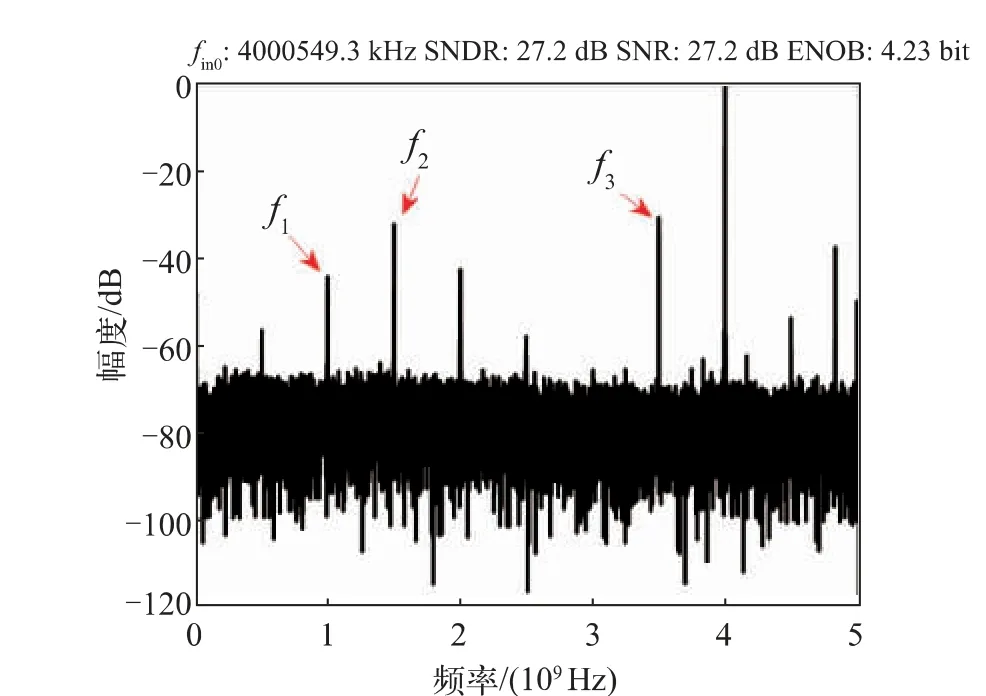

TIADC 的通道失配误差中,偏置误差会引起输入时钟、各个ADC 核时钟以及直流处的频率杂散,而增益误差和相位误差则会导致一些特定频率点处的谐波失真。信号采集系统测得的数字信号频率为fin0,整个系统的外部时钟频率为fc,而系统内部各个采样通道中ADC 核的时钟频率fc/2=fc/2,则增益误差和时间相位误差在整个系统输出数字信号频谱中引入的主要杂散频率f1=fc-fin0,f2=fc/2-fin0,f3=fc-f2,对应的相对幅度分别为A1、A2、A3。实测不同模拟输入信号频率处的3种杂散信号频率和相对幅度如表4 所示。测试得到的TIADC 系统的动态性能如图6~8 所示。

表4 各测试频率点处通道间失配误差引入的杂散信号频率和相对幅度

由图6~8 中频谱分析的结果可知,ENOB 由60.730 MHz 处的5.53 bit 缓慢降至4000.549 MHz 处的4.23 bit,SNDR 由60.730 MHz 的35.0 dB 逐渐下降至4000.549 MHz 处的27.2 dB。信号采集系统TIADC数字输出信号的频率和设定的模拟输入信号的频率基本一致,而随着模拟输入信号频率的增加,杂散信号的相对幅度显著增大,谐波造成的频谱失真会使信号采集系统的性能恶化,时间相位误差对整个TIADC系统的影响变得更加明显。该信号采集系统与目前国内外基于TIADC 的板级数据采集系统、商用示波器产品技术指标的比较如表5 所示。本研究设计的信号采集系统方案完全国产化,并且在保持10 GSa/s 高速采样率的前提下实时带宽达到4 GHz,和目前国内商用示波器产品(2 GHz)相比有明显优势,能更好地捕捉信号细节,有利于国产TIADC 的推广和产品化。

表5 本系统与相关信号采集系统指标对比

图6 模拟输入信号为60.730 MHz 时的测试结果

图7 模拟输入信号为640.564 MHz 时的测试结果

图8 模拟输入信号为4000.549 MHz 时的测试结果

4 结论

本研究基于国产FPGA 和TIADC 设计了一种信号采样系统,开发了系统的底层驱动,并完成了测试平台搭建,评估了系统的动态性能。该信号采集系统采样率高达10 GSa/s,实时采样带宽高达4 GHz,技术指标为国内顶尖水平。而该系统作为微系统的原理样机,在研制过程中探索并解决了TIADC 应用过程中需要注意的问题,将为国产化高速信号采集微系统的设计提供重要的参考依据。接下来还需要探索对TIADC 的通道失配误差进行估算和修正的更好方法,进一步优化采样系统的动态性能。