基于FPGA和VPX架构的星载存储系统设计实现

2022-11-26林海兵刘胜阳顾得友张俊杰苏思友

林海兵,刘胜阳,顾得友,张俊杰,苏思友

上海航天电子技术研究所,上海 201109

0 引言

随着宇航技术的不断发展,卫星的载荷展现出多样化、复杂化等特征。固态存储器作为卫星上的核心存储设备,其性能的好坏与任务的成功与否息息相关。一方面,固态存储器的处理速度因为更多载荷种类、更高精度、更快速度的信息流而持续提升。另一方面,在更加严苛的通信速率和恶劣的空间环境约束下,传统的基于板间并行通信设计的固态存储器不能满足当前的应用要求。

与ASIC相比,FPGA具有多种优势,如开发时间短、性能功耗比高、设计灵活、支持并行处理、延迟低、支持高存储器带宽等。因此,FPGA在航空航天、国防武器、高性能计算与数据中心、通信等领域有着极其广泛的应用。基于高速串行总线的VPX是目前国际上兼容性较好的军用嵌入式规范,具有模块化、通用化、扩展性、高可靠性等特点[1]。VPX总线作为新一代的工业总线标准,是VITA组织在保留了VME总线机械结构以及导冷抗震等方面优势的同时,引入了高速串行总线来替代并行总线的新一代高速串行总线标准。VPX总线带宽的大大增加得益于其模块之间的互联可以采用RapidIO、PCIe、光纤等高速串行总线,因此,这让设计时集成更多的I/O接口成为可能。VPX总线由于技术积累时间长、可靠性高、架构开放等优点,且在VITA组织也在积极推动下,它已形成了完备的规范体系和广大的应用市场。

1 VPX标准的发展过程

VPX是VITA推出的一种嵌入式系统总线标准,它在VME的开放式架构中引入了高速串行总线。VPX总线的核心为制定了基本机械结构和电气标准的VITA 46.0标准,它采用了MultiGigRT2连接器且沿用了VME 3U/6U的欧卡规格[2]。VPX总线标准对于5V、12V和48V的供电电压也有显著的提升,最大支持功率分别为115W、384W和768W,这为大功率高性能系统的设计提供了重要的保障。随着技术的发展,VITA46标准根据功能形成了多个版本的子系统,如VITA48系列标准、VITA 65系列标准。VITA48为了使VPX能适应恶劣的工作环境而对散热方式和结构加固这两方面进行了重新定义。为了有更好的兼容性和开放性,VITA 65重新定义了VPX系统间的拓扑结构[3]。

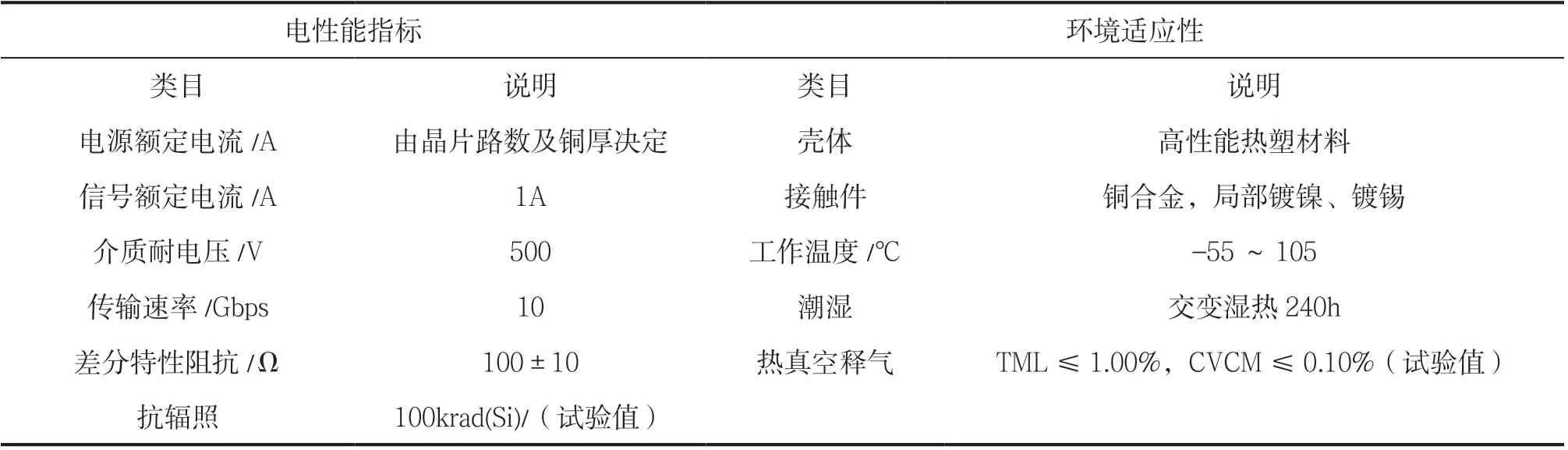

SpaceVPX(VITA 78)总线[4]描述了用于创建高性能、具备容错能力的背板和模块的通用开放标准,以适应航天器和其他高可靠性应用的电子系统。SpaceVPX在OpenVPX行业标准的基础和空间应用的背景下,增加了航天器接口和容错设计,如单点故障容错,航天器接口,备用模块支持,冗余管理以及状态和诊断支持。表1给出了VPX部分重要电性能与环境适应性。

表1 VPX部分电性能与环境适应性

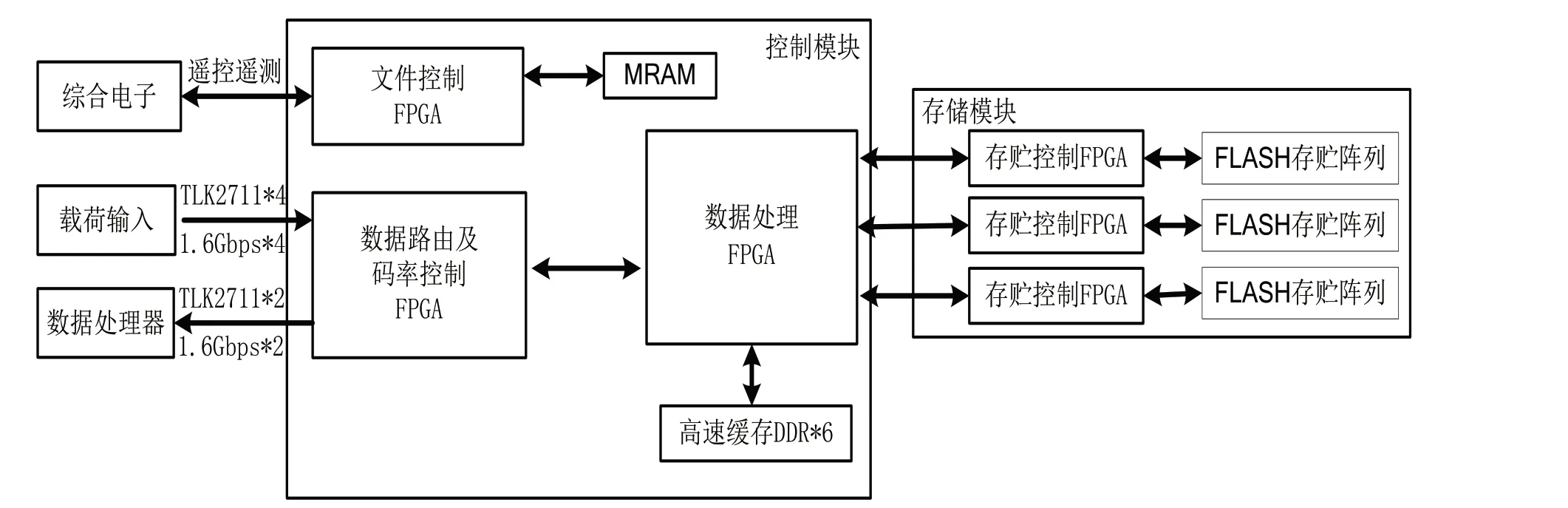

2 固态存储器总体方案设计

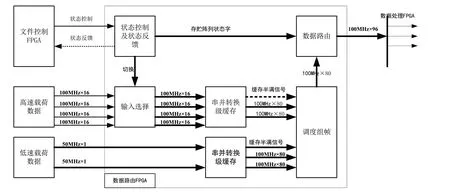

固态存储系统是卫星圆满完成任务的重要存储介质,它能记录多种载荷数据,但随着空间任务的日益复杂化和多样化,良好的设计在开发流程中值得设计师们的关注。图1给出了本文固态存储器的系统架构框图。该固态存储器由电源模块、控制模块、存储模块组成,如4路TLK2711共6.4Gbps高速载荷数据输入和2路TLK2711共3.2Gbps输出的接口模块、NAND FLASH存储芯片组、用于数据高速缓存的DDR SDRAM和用于管理的存储器MRAM,此外,该系统中还有多个晶振和多块电源芯片。根据存储器的功能,我们将整个系统进行划分。因此,硬件上有电源板、存储板、控制板和底板,而底板上各板级之间的供电和数据通信则通过VPX接口进行连接,该接口在设计中遵循表1所列约束。本节接下来对部分重要模块进行设计。

图1 固态存储器系统架构框图

电源板作为任何一台单机的重要组成部分,它将外部输入的30V电压转换成需要的5V电压。为了使设计更加的简单,本设计将集成电源模块引入,并在前级使用共模线圈来滤除共模电磁干扰和抑制本身不向外发出电磁干扰。在集成电源模块的后端,本设计中放了两对并联的16V/330uF的钽电容用于储能,加入了数个0.1uF常规电容来滤除高频噪声。5V的电源通过底板进入功能板,然后根据该功能板上需要的电源种类,5V电压进入DC-DC芯片或者LDO芯片转换成需要的供电电压。固态存储器系统中的多个FPGA需要协同工作,控制板上的文件控制FPGA是交互的核心。它接收了来自综合电子的遥控信号,经过解析后将各个控制指令转发给相应的模块。此外,他还将各个模块返回的遥测信号打包并在遥测群采信号到来之后返还给综合电子。文件控制FPGA最为重要的一点是其控制了存储模块的逻辑地址并对MRAM芯片进行操作。

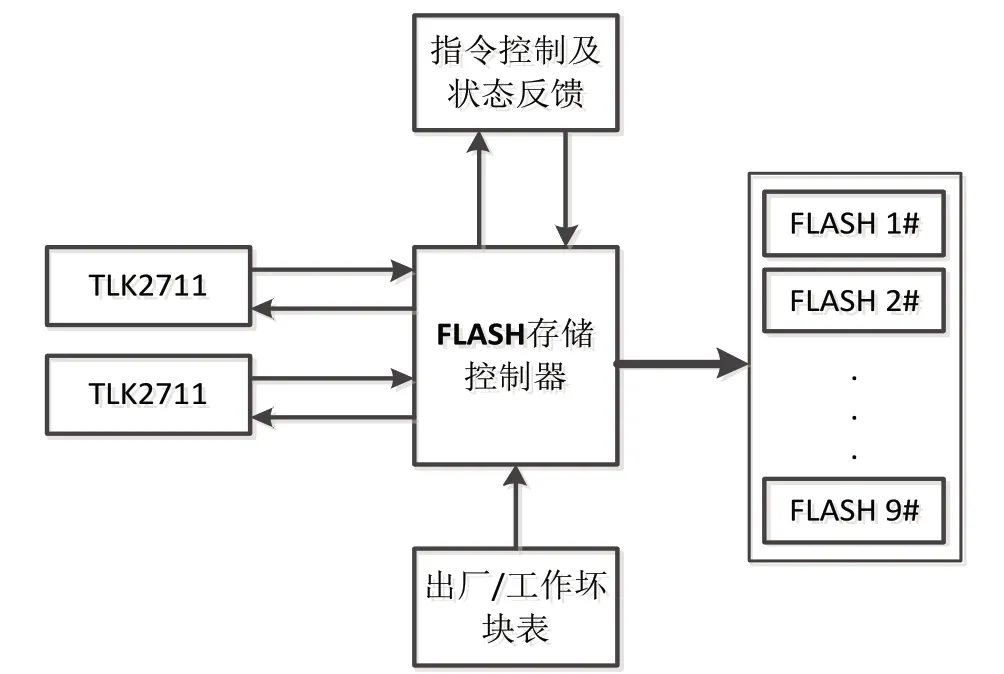

2.1 存储单元设计

FLASH存储单元组成框图如图2所示。一组FLASH存储单元主要由2路高速TLK2711数据接口、FLASH存储控制器、出厂坏块映射表、工作坏块映射表和存储阵列等组成,每个存储阵列由9片8位位宽的FLASH存储芯片构成。FLASH存储芯片容量可以根据研制技术指标要求灵活配置成32Gb/64Gb/128Gb。在兼顾可靠性和吞吐率的情况下,本设计的FLASH采用多组并行读写但读写时钟频率不会太高。在硬件上,一块存储板有3组Flash芯片组,2块存储板构成一台单机。为了降低主控芯片避免单粒子翻转的风险,本设计中选用了ACTEL公司生产的AX2000反熔丝型FPGA。

图2 FLASH存储单元组成框图

一组FLASH存储单元提供2路TLK2711高速串行数据,在存储单元热备份时作为控制板主备份的输入输出信号,设计时钟100MHz,线上码速率2Gbps,有效数据率1.6Gbps。

FLASH存储控制器的设计功能如下:

①接收控制板主份或备份输入数据,打包成FLASH存储协议格式;

②将回放数据复制后发送给控制板主份或备份;

③FLASH底层驱动程序、坏块管理。

如前所述,文件控制FPGA对存储系统的逻辑地址进行管理控制,那么这里的FLASH控制器需要将逻辑地址映射为实际的物理地址。针对FLASH芯片不可避免出现坏块的情况,本设计中的控制器在对坏块进行维护时使用坏块替换策略,将坏块的地址映射为高地址中未使用的好块地址。

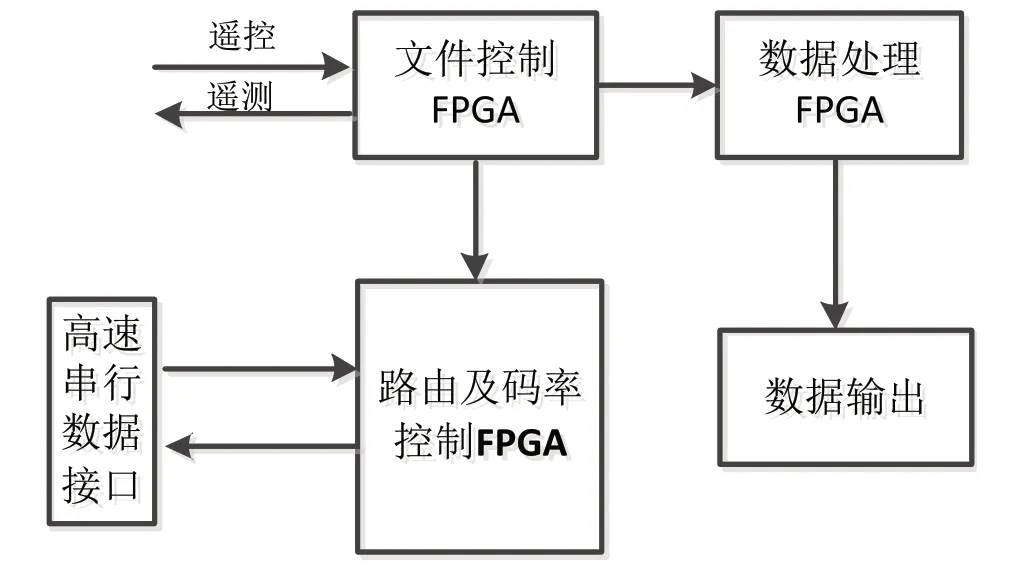

2.2 控制单元设计

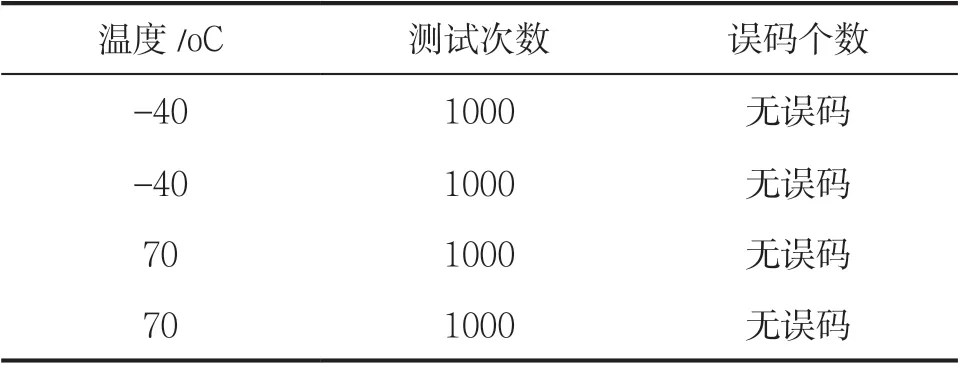

控制板是固态存储器的设计核心,它主要完成输入数据路由、输出码率控制、高速数据处理、指令发送和状态采集等功能。控制单元设计框图如图3所示。

图3 控制单元设计框图

数据处理FPGA作为数据通路中的中枢,它控制着数片DDR SDRAM用于载荷输入数据和存储板读出数据的缓存。DDR芯片使用并行控制的方式来提高数据的吞吐能力。在考虑了设计的复杂度和资源的使用率的情况下,数据处理FPGA和路由及码率控制FPGA采用了XILINX公司的Virtex4芯片。然而,SRAM型FPGA容易发生单粒子翻转事件,因此在程序设计时对关键模块采用了三模冗余设计,并对芯片进行贴铅皮处理。

2.3 数据路由FPGA设计

数据路由及码率控制FPGA完成输入数据路由和输出数据码率控制两个功能。数据路由功能根据文件控制FPGA发送的状态控制字,完成高速载荷数据的输入选择,然后将数据进行通道复用后输出给数据路由单元,数据路由单元根据存储阵列状态字进行数据路由和发送给数据处理FPGA。路由FPGA设计框图如图4所示。码率控制模块相对来说比较简单,不再详细说明。

图4 路由FPGA设计框图

3 测试方案

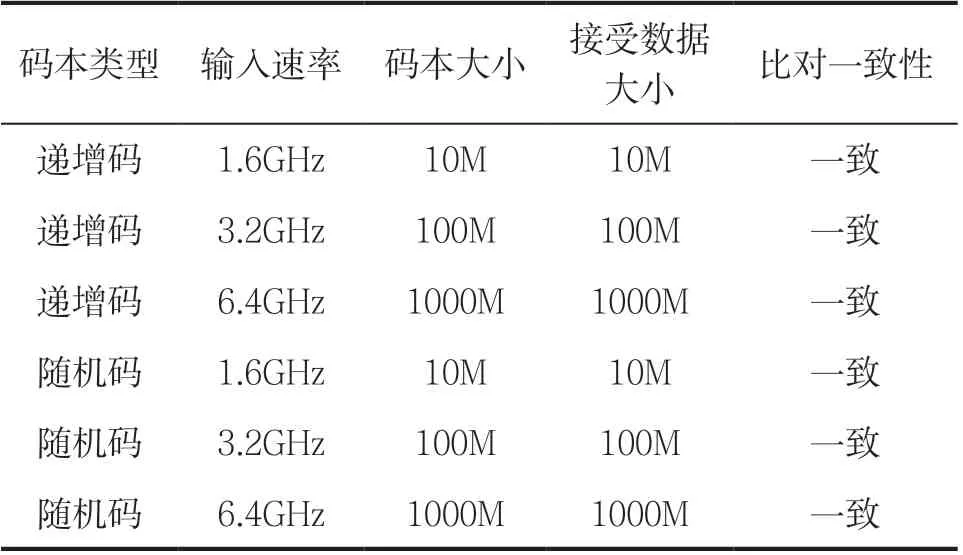

固态存储器采用冗余备份设计,输入信息有遥控遥测设备和码源设备,前者通过LVDS接口与固态存储器连接,后者通过4路2711通道连接。测试分为单次测试和循环测试,单次测试结果如表2所示。

表2 单次测试结果

从表2可知,本文对设计的系统一共使用了两种测试码型,码本的大小分别是10M、100M和1000M,输入总速率分别为1.6G、3.2G和6.4G,将接收到的数据与码本进行比对,结果一致。为了考核所设计存储系统的稳定性与可靠性,在温度拉偏的工况下进行了重复试验。试验使用的码本为随机码,输入总速率为6.4G,码本大小为1000M,-40度和70度工况下的测试结果如表3所示。

表3 循环测试结果

4 结语

目前大多数固态存储器的载荷输入使用LVDS接口类型且板级间的通信使用CPCI,这样的存储系统带宽较小、可扩展性较差。本文设计的一种基于VPX架构和FPGA的高性能星载固态存储器可以较好地解决固态存储器内外数据传输带宽小的限制,大幅提升了信号处理与存储的能力。该固态存储器具有传输带宽大,接口配置灵活等优点,可满足大部分对总线带宽和实时性要求较高的星载存储平台任务要求。在通用化、模块化和系统化设计方法指导和国内空间技术不断发展的浪潮下,VPX和FPGA组合成的系统功能将会被进一步丰富完善。