基于0.18 μm SMIC工艺的一款TDC芯片设计

2022-11-19马毅超王亮懿滕海云蒋俊国

马毅超 王亮懿 滕海云 蒋俊国

1(陕西科技大学 西安 710021)

2(中国科学院高能物理研究所 东莞 523000)

粒子飞行时间(Time of Flight,TOF)测量是当代高能物理实验中不可或缺的技术手段之一,它能够间接反映粒子的动量、质量等信息,对于鉴别粒子种类从而确定其反应类型,探究粒子物理本质起着至关重要的作用[1-2]。不同类型的粒子,在实验中的飞行时间也会存在一定的差异,为了能够实现较好的鉴别能力,通常要求探测器的时间分辨率达到百皮秒以内[3-4]。现阶段应用广泛的时间数字转换器(Time to Digital Convertor,TDC)设计方案主要分为两类:其一是通过延迟链内插法实现高精度时间测量算法的设计,该方法测量精度可达13 ps以内[5],但是内插单元的增多使得解码困难且对时钟要求较高[6-7];其二是通过时钟分相法实现高精度时间测量算法的设计,该方法没有过多的延时单元插入,解码简单,但是精度最好只能达到100 ps左右[8],难以满足实验中百皮秒内时间精度的要求[9]。

针对以上两种设计方案存在的问题,本文完成了一款基于差分延迟环结构的TDC芯片设计。其中差分延迟环结构可以使芯片的分辨率达到17 ps。该结构的内插单元较少,且采用双环结构设计,由于两组延迟环之间仅延迟时间不同,其余特性相似,因此双环之间的延迟差可以抵消工艺、电压及温度变化,使得芯片抗干扰能力强,受外界温度等环境因素影响较小。TDC芯片采用中芯国际(Semiconductor Manufacturing International Corporation,SMIC)0.18 μm工艺技术设计完成并进行流片,可以实现高分辨率的时间数字转换[10-11]。

1 TDC芯片结构设计

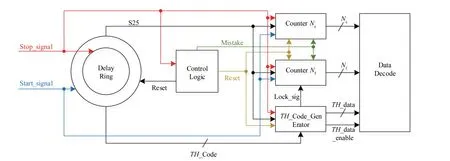

TDC芯片结构如图1所示,该芯片由差分环TDC内核、控制逻辑、温度计解码器、4位精细计数器(Nf)和16位粗计数器(Nc)组成。该芯片在对两组信号时间差进行测量时,代表起始的信号(Start)先进入到慢环,之后代表停止的信号(Stop)再进入到快环。通过内置的比较器对信号状态进行比较,最终输出温度计码“TH”,并通过温度计到二进制编码器转换成6位二进制代码。TH记录结束信号超过起始信号的位置,即延迟单元的数量。精细计数器(Nf)记录结束信号赶上起始信号之前起始信号的传输圈数,粗计数器(Nc)记录结束信号进入差分环TDC之前起始信号的传输圈数。通过对三个数据进行整合最终得到测量的时间差。

图1 TDC芯片结构Fig.1 Diagram of TDC chip structure

2 电路结构设计

2.1 差分延迟环TDC设计

传统的差分延迟链TDC如图2所示。该TDC结构由两条分别带有多个延迟单元的延迟链构成,两条延迟链上的延迟单元相互对应,且每条链自身各延迟单元的延迟时间相同,其中Start链上延迟单元的延迟时间为t1,Stop链上延迟单元的延迟时间为t2,t1>t2[12]。相互对应的两个延迟单元的输出信号在同一个D触发器中进行比较,但由于其分辨率与集成电路工艺决定的门延时密切相关,且硬件消耗随测量范围的增大呈指数增长[13]。为了减少延迟链上延迟单元的浪费,本文对传统的差分延迟链进行改进[14],设计了一种延迟环结构。环状结构可以使差分延迟单元在一次测量中重复使用,通过该设计可以大大减少延迟单元的数量[15]。

图2 差分延迟链TDCFig.2 Differential delay chain TDC

差分延迟环TDC结构如图3所示。两个具有不同延迟的与非门环用于测量输入信号的时间间隔。差分环TDC的核心由两个比较链路组成,分别在奇数圈和偶数圈时运行[16]。差分环TDC包含奇数个延迟单元,输入信号沿环传播一圈后,会由上升沿变成下降沿。两种类型的比较器沿环交替放置,分别比较上升沿和下降沿。差分环TDC的核心由三个部分组成:一个延迟较小的快环、一个延迟较大的慢环和50个比较器。每个环有25级与非门,延迟可通过外部偏置电压调节。快环和慢环中与非门的传播延迟分别设置为Tf和Ts。因此,差分环TDC的时间分辨率R如式(1)所示:

图3 差分延迟环TDCFig.3 Differential delay ring TDC

2.2 判断单元组合设计

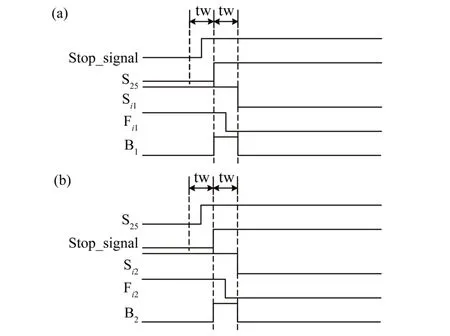

差分环TDC将整个TDC核心分离为两个差分延迟环,如图4所示。图4(a)显示了差分环TDC在第一圈中的操作。在第一圈中,起始信号和结束信号的上升沿进入到两个与非门,分别沿慢环和快环进行传输。起始信号在与非门延迟Ts后传播到S2,结束信号在与非门延迟Tf后传播到F2。比较器A1比较S1和F1处的两个上升沿,而比较器B2比较S2和F2处的两个下降沿。当起始信号分别传播到S23和S24时,A1和B2将复位。图4(b)显示了差分环第二圈的操作。与第一圈的操作类似,不同的是在第二圈中,起始信号和结束信号的下降沿进入到两个与非门。

图4 判断单元组合示意图(a)TDC第一圈操作,(b)TDC第二圈操作Fig.4 Diagram of judgment unit combination(a)TDC first loop operation,(b)TDC second loop operation

当两个信号都进入差分环后,慢环和快环的输入都设置为逻辑“1”,直到结束信号赶上起始信号。

2.3 数据处理及分析

延迟总量由三个元素组成,粗计数器值Nc、精细计数器值Nf和温度计代码TH,如图5的时序图所示。在结束信号进入到差分环TDC之前,只有起始信号沿着慢环传输,此时的差分环TDC在其粗测量模式下工作,时间间隔的差值为50Ts,这种粗插值模式提高了功率和面积效率,使测量时间更加方便。一旦结束信号进入环,差分环TDC将使用差分原理自动切换到其精细测量模式,在该模式下,TDC以精细分辨率对被测时间间隔的剩余部分进行插值,直到结束信号赶上起始信号。由于温度计码的位计数有限,计数器用于辅助计算精细插值的数量。因此差分环TDC的最终输出代码,即测量的时间间隔T如式(2)所示:

图5 差分环TDC时序图Fig.5 Sequence diagram of differential ring TDC

其中:TDC分辨率由R=Ts-Tf给出,测量范围为0~T。

3 关键模块电路实现

3.1 比较器的实现

图6为差分环TDC的比较器示意图,其采用了对称拓扑结构,使比较器对外部因素变化的敏感度降低。两个比较器分别由上升沿和下降沿触发,且均由一对边缘检测器、两组复位电路和一个核心比较器组成。在慢环中的起始信号传输期间,每隔一圈Rst_i信号会重置比较器。在开始新的测量之前,来自控制逻辑的Rst_e信号将重置所有比较器。两个比较器中的边缘检测器都输出一个窄的负脉冲来设置比较器,继而释放对重置信号的控制。当慢环中的信号首先到达Si时,比较器输出“0”,即结束信号尚未赶上起始信号。当快环中的信号首先到达时,比较器输出“1”,表示结束信号赶上起始信号。系统会检测到比较器输出处从0到1的第一次转换,并用于锁存精细计数器。

图6 比较器结构图(a)上升沿比较器,(b)下降沿比较器Fig.6 Structure diagram of arbiter(a)Rise edge arbiter,(b)Falling edge arbiter

本文TDC芯片为单输入通道,输入信号的类型为TTL(上升沿有效)。比较器的输入输出延迟对TDC至关重要,该延迟依赖于两个输入信号之间的时间间隔。当时间间隔小于1 ps时,比较器延迟急剧增加。

在每次比较开始之前,都需要重置比较器。复位信号来自慢环中延迟单元的输出,比当前的慢环早三级,需要比较器在慢环的半个周期内进行比较,并在另外半个周期内重置。边缘检测器将比较器A与比较器B区分开来。图7显示了比较器A的工作周期,半个周期的时间为25Ts,其中“1”区域和“0”区域的时间分别为3Ts和22Ts。前半个周期是就绪周期,其中比较器准备接收输入信号并判断它们的到达时序。后半个周期是重置周期,其中比较器重置为零,输入信号也被屏蔽。如图7所示,当Fi的上升沿出现在“0”区域时,比较器将输出0,当Fi的上升沿出现在“1”区域时,比较器将输出1。在两个环中,结束信号追赶起始信号的过程可视为Fi的边沿接近并超过Si边沿的过程。

图7 比较器A的运行周期Fig.7 Operating cycle of arbiter A

3.2 校正电路的实现

如图8所示,当结束信号在其第一圈的传输期间出现在“1”区域时,B1处会发生异常的“01”转变。正常情况下,比较器B1应该对边沿c与边沿a进行比较。信号传输发生异常时,边沿c将与F1的下一个下降边沿b进行比较。在结束信号沿着快环传输之前,比较器A25和B24均被设置为“0”,此时温度计码的最低有效位将错误检测到“001”转换,差分环TDC会错误地判断结束信号已经赶上起始信号,因此需要正确的错误检测和校正电路。该校正电路会屏蔽这种错误的“001”检测信号,并保持结束信号的边沿c继续追赶边沿a,直至下一次追赶发生。延迟的结束信号将在输入快环后立即采样比较器B24、A25以及B1的状态。如果检测到错误的“001”代码,校正电路会将温度计中的寄存器组重置为二进制编码器,该复位信号将保持有效,直到图8中的边沿c进入比较器的复位区域。由于比较器B24、A25以及B1的“001”状态由结束信号采样,因此校正电路正常工作,当输入时间间隔非常小时,可以对校正电路进行修改,通过使用小相位误差检测(Small Phase Error Detector,SPED)来禁用寄存器组的复位。

图8 比较器B的意外“01”转换Fig.8 Unexpected"01"conversion of arbiter B

3.3 温度计到二进制编码器

温度计到二进制编码器由寄存器组、气泡校正、“01”检测电路和二进制编码器组成。两个比较器链的输出被组合成一个50位的温度计码,并将其转换为6位二进制码。温度计码中的第一个“01”转换将由“01”检测电路检测,但是在比较器输出的下降沿中有很多假“01”转换,如图9所示。这种情况需要从差分环TDC的输出中将其移除,因此本文设计的寄存器组将比较器输出的下降沿过滤掉,从而消除温度计码中的假“01”转换。追赶完成后,当差分环的两个外部输入重置为“0”时,两个环就停止工作。

图9 时序图显示寄存器组在下降边缘过滤掉假“01”(a)假“01”时序图,(b)过滤假“01”后的时序图Fig.9 The sequence diagram shows that the register group filters out the false"01"at the falling edge(a)Fake"01"sequence diagram,(b)Sequence diagram after filtering fake"01"

3.4 粗细计数电路设计

SPED由两个比较器组成,两个比较器交叉输入结束信号和S25,如果两个输入信号之间的时间间隔小于tw,则输出“1”。图10为小相位误差检测器的时序图,其中Si1、Fi2和Si2、Fi1被反向复制,S25和结束信号的延迟分别为tw。当Fi1出现在B1的“1”区域时,B1输出为“1”;当Fi2出现在B2的“1”区域时,B2输出为“1”;当结束信号出现在S25的小范围内时,Y被设置为“1”。

图10 B1(a)和B2(b)的时序图Fig.10 Sequence diagram of B1(a)and B2(b)

计数器Nc和Nf由差分环中的S25触发,由于差分环到温度计-二进制编码器和差分环到两个计数器之间的传播延迟差,以及S25到粗计数器Nc和结束信号到Nc之间的延迟差,都可能会出现代码丢失的现象,这些延迟差随输入时间间隔而变化,不容易进行匹配,因此两组计数器Nc和Nf就用于解决代码丢失的问题。在计数器中,Nceven和Ncodd用于计算起始信号在结束信号进入差分环之前传输的奇偶圈数。当结束信号没有超过S25时,SPED将选择Nceven,否则Ncodd减去B1将是Nc的结果;当结束信号领先S25一小段时间间隔且Ncodd比Nc大“1”时,B1设置为“1”。同时,在奇数圈追赶时,Nfeven将被选中,否则Ncodd减去“1”将是Nf的输出。

4 仿真分析

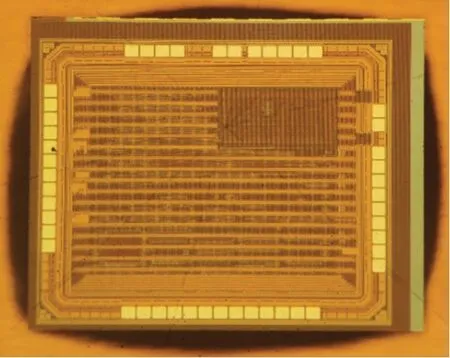

芯片整体版图如图11所示,该版图由Synopsis IC Compiler制作完成,主要由差分延迟环TDC模块、250 MHz时钟的锁相环(Phase Locked Loop,PLL)电路模块、计数器模块、温度计解码器以及控制模块构成。其中差分延迟环TDC模块又可细化为延迟环模块、温度计码生成模块以及粗计数与细计数生成模块三个部分。芯片实体如图12所示,该TDC芯片采用0.18 μm SMIC系列工艺制造[17-18],时钟输入为25 MHz,芯片死时间为11.77 ns,动态范围为0~210 μs,整个芯片的版图面积为1.35 mm×1.35 mm,芯片在1.8 V电源下进行工作。

图11 芯片版图Fig.11 Chip layout

图12 TDC芯片图Fig.12 TDC chip diagram

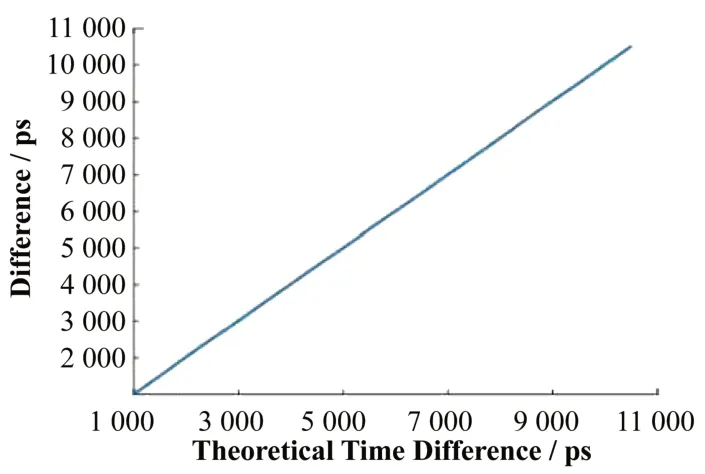

TDC芯片在1.8 V工作电压、25℃工作温度的基础器件库下进行工作。器件库的部分参数为:时间单位1 ns、电流单元位1 ms、功率单位1 μW、负载电容单位1 pf、输入信号变化的界定为50%、输出信号变化的界定为50%。在信号的上升与下降过程中,有效高电平的阈值设置为基准电压的70%,有效低电平的阈值设置为基准电压的30%。默认引脚的负载电容为0.004 pf,默认最大传输延时为2.49 ns,默认器件扇出为1。图13为差分延迟环的校准结果曲线图。本文TDC共有50个延迟单元,对差分延迟环的时延进行带寄生参数的后仿真,50 Bin对应的总延迟时间为893 ps,平均每Bin约为17 ps,即时间分辨率为17 ps。图14显示了TDC的时间精度,对时间间隔差值为260 ps的信号进行了100 000次测试,结果表明时间精度为8.5 ps(Root Mean Square,RMS)。图15与图16为实际测量中多组实验数据的真实时间差值与实验时间差值的折线对比图。图15为局部时间差值对比图,图中包含20组有效数据,时间测量间隔为10 ps。图16为总体时间差值对比图,同样为20组有效数据,时间测量间隔为500 ps。由此可得TDC芯片的线性度良好,符合本设计的预期结果。

图13 延迟环校正曲线Fig.13 Calibration curve of delay ring

图14 TDC时间精度Fig.14 Time accuracy of TDC

图15 局部时间差值对比Fig.15 Comparison of local time difference

图16 总体时间差值对比Fig.16 Comparison of overall time difference

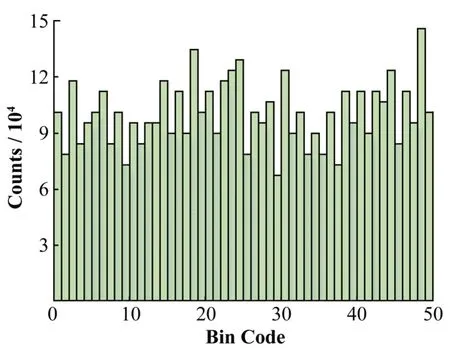

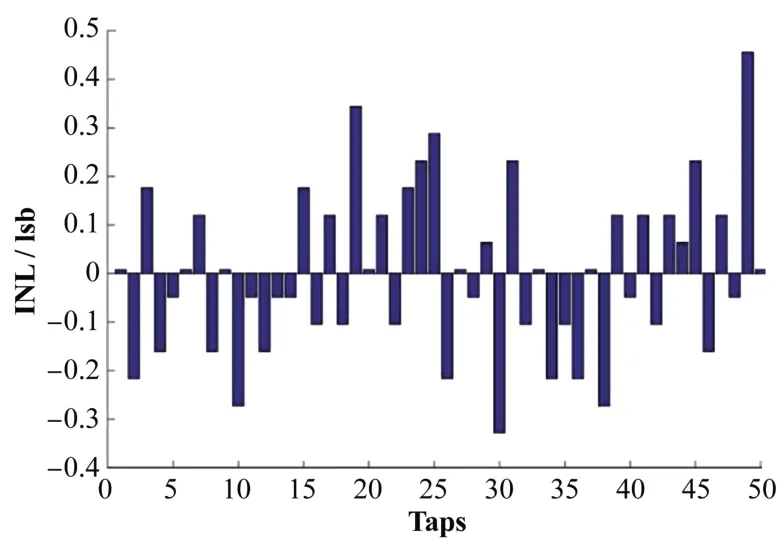

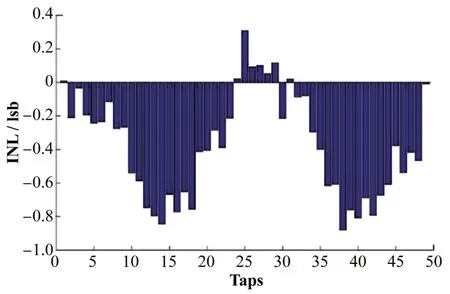

对每个设置的延迟时间进行2 000次测试,统计TDC读数,按照TDC每个读数为一个时间Bin宽,得到统计结果如图17所示。图18、19分别为延时单元的微分非线性(Differential Nonlinearity,DNL)与积分非线性(Integral Nonlinearity,INL)测试结果。DNL代表延时单元理论时间间隔与实验时间间隔的偏移值。INL则相当于DNL的累积效应。DNL代表延时单元的一致性,DNL越小,延时单元的延时时间就越均匀。由图18、19可知,TDC的DNL在[-0.4,0.5]LSB之间,INL在[-1,0.4]LSB之间。

图17 TDC各延迟单元的计数Fig.17 Counts of each TDC delay bin

图18 DNL测试结果Fig.18 DNL test results

通过对比不同设计TDC芯片的工艺、面积以及分辨率等,如表1所示,本文设计的TDC芯片可以更好地应用于高精度时间测量的高能物理实验中。

表1 不同设计的TDC芯片对比Table 1 Comparison of TDC chips with different designs

图19 INL测试结果Fig.19 INL test results

5 结语

本文基于高能物理实验对高精度时间测量的时间数字转换器的需求,在经典差分延迟链的基础上,提出了一种差分延迟环TDC结构,该结构将差分延迟链中一个个小的差分延迟单元放置在环形结构中,使得差分延迟链上的每个差分延迟单元可以得到重复利用,从而能够测量出更大的时间间隔。在环形结构中重复使用的每个差分延迟单元都能以小面积和低功耗的效率实现高分辨率和大动态范围,提出的差分环TDC动态范围为0~210 μs,分辨率为17 ps,精度可达8.5 ps(RMS)。该TDC芯片采用0.18 μm SMIC工艺实现,版图面积为1.35 mm×1.35 mm,芯片在1.8 V电源下进行工作,工作频率为250 MHz。综上所述,本文设计的TDC芯片可以更好地应用于高精度时间测量的高能物理实验中。

作者贡献声明马毅超:负责研究的提出及经费支持;王亮懿:负责文章起草及最终版本修订;滕海云:负责文章审阅;蒋俊国:负责数据分析及技术支持。