基于XpressGXS10的FPGA硬件仿真平台研究

2022-11-17李凯亮刘洋

李凯亮,刘洋

(江南大学,江苏 无锡 214122)

0 引 言

作为可重复编程的半定制集成电路,FPGA 凭借其设计灵活、低时延低功耗、计算资源丰富等众多优点在越来越多的智能化设备中被应用,无论是在传统的军工航天、移动通信,还是在新兴的人工智能、自动驾驶、边缘计算等领域均扮演着愈发重要的作用。

完整的FPGA 设计流程包括需求分析、逻辑设计、功能仿真、综合优化、门级仿真、实现、布局布线、时序仿真、生成比特、板机仿真、下载配置[1]。本文提出的仿真类型属于FPGA 功能仿真,主要用来验证电路功能是否符合设计要求,是最基础最重要的一个仿真。当下随着FPGA 的应用场景不断拓展,其设计复杂度也快速上升,这就使对应的功能仿真也面临巨大挑战。

已有的功能仿真方法主要有三种。第一种是基于EDA(Electronic design automation) 软件做test bench 仿真,如Synopsys 公司的VCS(Verilog Compiled Simulator),Mentor 公司的Modelsim 等。仿真流程是确定要验证的功能点后,使用硬件描述语言编写定向测试激励,仿真软件将测试激励送入待测设计(Design Under Test,DUT),将DUT输出信号与期望值进行手动比较[2,3],如通过观察仿真波形的方式进行确认。这种仿真方法方便快捷,适用于小型设计,但是对于中大型复杂设计,采用人工观察波形的方法不仅工作量大且极易出错。第二种是文章[4]提出的形式化验证,这种仿真方式不需要激励文件,通过严密的逻辑方式和数学推理,去验证逻辑设计是否满足规范。但这种方法无法观察到DUT 内部的仿真动态行为,且需要大量的计算资源支持。第三种是文献[5-7]提出的基于UVM(Universal Verification Methodology)的功能验证方法。UVM 是Accellera 组织推出的一种针对可编程逻辑的通用验证方法学,这种验证方法学采用System Verilog 面向对象语言,架构清晰,代码可读性强,兼容三大EDA 厂商(Synopsys、Mentor、Cadence)的仿真工具,可以最大程度的支持随机化测试和代码重用。但UVM 在仿真大型FPGA 设计时比较耗时,稍微大一点的设计需要数十个小时才能完成一次功能仿真,如果仿真出现问题修复后需要重新启动,时间成本过大。

综合分析现有仿真方法的缺陷,本文提出了一种针对大型FPGA 设计的硬件仿真平台。该仿真平台采用PC+XpressGXS10硬件板卡的架构,两者通过PCIe(Peripheral Component Interconnect express)总线进行数据交互。PC 用来生成测试激励、参考模型,控制仿真流程,生成仿真报告等。XpressGXS10 用来实现仿真组件、映射DUT、比对仿真数据等。这种仿真架构主要解决了目前已有FPGA 仿真平台的4 类问题:

(1)人工比对仿真结果带来的烦琐不可靠、验证效率低的问题。

(2)可编程逻辑映射成实际电路过程中带来的时延不确定性问题。

(3)大型FPGA 设计仿真带来的时间过长问题。

(4)抽象层次低、通用性差、定向测试覆盖率不全面问题。

本文在第一部分主要描述了基于XpressGXS10 的FPGA硬件仿真平台架构及实现,在第二部分提出了一种针对OFDM(Orthogonal Frequency Division Multiplexing)系统的仿真应用案例。通过对仿真结果和速度的分析,进一步验证了所提仿真平台的可行性和高效性。

1 基于XpressGXS10 的FPGA 硬件仿真实现

同时兼备可靠性和快捷性是大规模FPGA 设计仿真的重点和难点。本文所提出的基于XpressGXS10 的硬件仿真平台一方面基于MATLAB 生成完备灵活的场景模型和参考模型,保证仿真的可靠性,另一方面将运算量大、耗时长的仿真组件和DUT 映射到XpressGXS10 板卡进行硬件仿真加速,进一步提高FPGA 的仿真效率。

1.1 XpressGXS10 硬件板卡

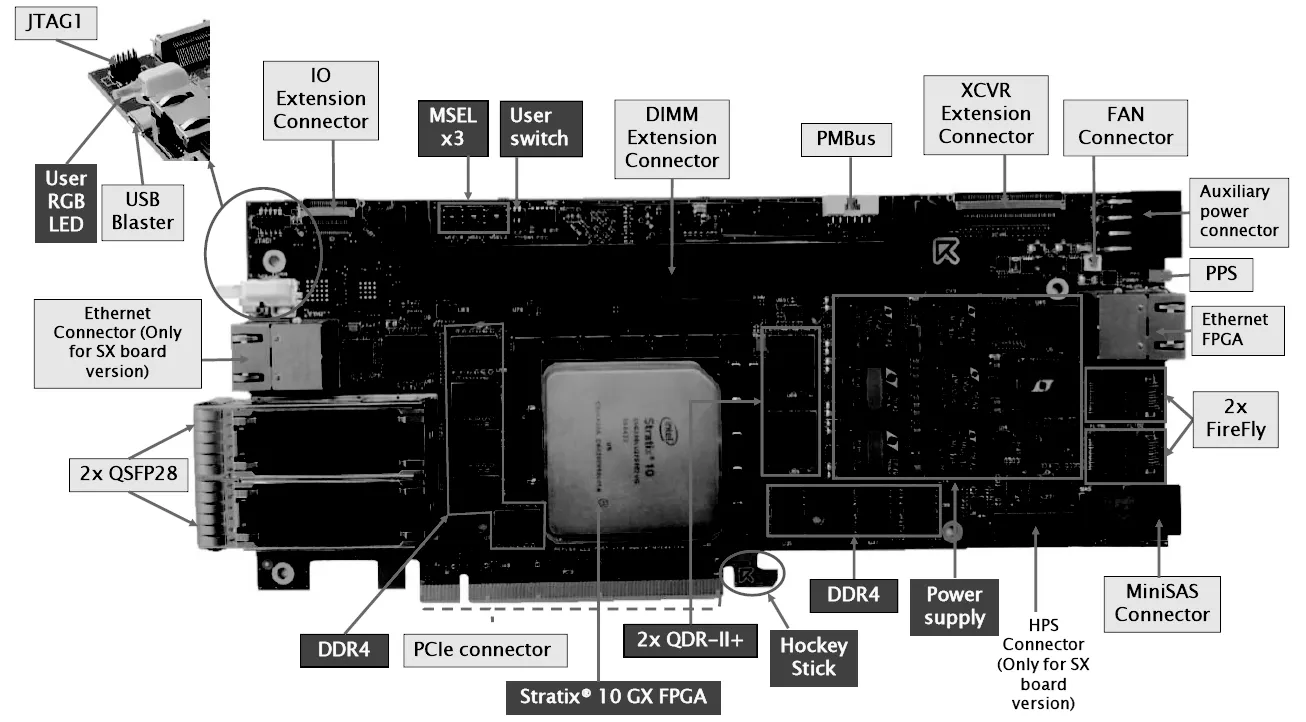

大型FPGA 设计在做硬件仿真加速时需要三类资源做支撑,一是丰富的存储资源用于存储大量的测试激励以及仿真比对结果;二是丰富的可编程逻辑资源用于实现仿真组件和映射DUT;三是大吞吐率的接口资源用于硬件加速板卡和其他设备进行数据交互。本文选用REFLEX CES 公司推出的XpressGXS10 硬件加速板卡。该板卡中搭载一颗Stratix®10 GX SOC 芯片,这款系统级(System On Chip,SOC)芯片采用14 纳米工艺,包含了两片相同的FPGA 核心和一颗四核64-bit ARM Cortex-A53,总的核心面积为1 400 平方毫米,每个核心拥有500 万个逻辑单元以及相应的I/O 单元。两个FPGA 核心通过Intel 新的EMIB 技术进行互联,数据带宽高达6.5 TB/s。此外板载高速串行连接和高密度内存,使得其适合于视频处理、机器学习、基因组学研究、金融风险分析等密集计算、高并发、高带宽场景,主要的板载资源有[8]:

(1)2x QSFP28 连接器,支持10 Gb/s、40 Gb/s、100 Gb/s 网络接口。

(2)1x PCIe Gen 3 接口。

(3)2x 8 GB DDR4 存储芯片。

(4)1x Stratix® 10 GX FPGA 芯片。

(5)1x Si5341 时钟芯片,1x Si5344 时钟芯片。

(6)1x DDR4 扩展接口。

具体板卡资源分布如图1所示。

图1 XpressGXS10 板卡

1.2 FPGA 硬件仿真架构

基于UVM 的仿真方法已经是比较完备的验证方法学,本文的重点主要是放在如何提高大型FPGA 仿真速度的问题上,即通过对仿真耗时的环节进行硬件加速来解决。FPGA硬件仿真架构如图2所示,主要由PC 和XpressGXS10 组成,两者通过PCIe(Peripheral Component Interconnect express)和JTAG(Joint Test Action Group)接口进行数据交互。其中PCIe 最大吞吐率可以达到15.75 GB/s,用于导入测试用例的输入数据以及仿真结果的读取等。JTAG 接口用于烧录仿真组件综合成的比特流文件。

图2 FPGA 硬件仿真架构

PC 上包含有仿真主控器,基于MATLAB 软件搭建的场景模型和参考模型。仿真主控器用于控制整个FPGA 的仿真流程,场景模型用于生成各种场景的测试激励,如功能测试和性能测试。功能测试主要是针对设计的功能特性做黑盒测试,生成对应场景的测试激励数据,用于检查功能错误或者遗漏问题;性能测试是生成多种正常、峰值以及异常负载的激励数据来对设计的各项性能指标进行测试,确定各种环境负载下的设计性能变化情况,从而不断提高设计稳定性和可靠性。参考模型是与DUT 具备相同功能的行为级模型。大型FPGA 设计的开发流程是设计团队和测试团队均基于需求说明书的理解搭建两套具备同样功能的不同级别的系统,设计团队基于Verilog 或者VHDL 语言搭建的系统就是正常需要投放市场的产品。测试团队基于高级语言如Python,System Verilog(本文采用MATLAB)搭建的系统称为行为级模型。当两套系统分别搭建好后,灌入相同的测试激励,比对相应的输出结果。如果两套系统的输出比对不上,则需要检查是仿真平台问题或者设计系统问题等,直至输出完全相同,仿真结束。这种做法是避免某一方对需求说明书理解偏差导致的功能设计问题。

XpressGXS10 用来映射DUT,实现各个仿真组件。仿真组件主要有DDR4(Double Data Rate Synchronous Dynamic Random Access Memory)控制器、驱动器、监视器、检验器、DUT 和仿真记录器。DDR4 控制器用于读取存储在DDR4 的测试激励、参考模型数据等;驱动器用于做DDR4和DUT 之间的数据位宽转换、跨时钟处理等,并通过可定制接口如AXI4(Advanced eXtensible Interface 4.0),SPI(Serial Peripheral Interface)将激励数据送进DUT;监视器用于采样DUT 仿真节点的输出,触发DDR4 控制器读取参考模型对应仿真节点的数据并将两路数据送进检验器。检验器用于比对两路仿真数据并将比对信息送进仿真记录器;仿真记录器将比对信息处理成易于查看的仿真结果并存储,仿真结束后由主控器读取。除此之外XpressGXS10 还包括存储扩展插槽、电源管理、时钟生成器等。

2 应用与仿真案例分析

基于上述提到的XpressGXS10 FPGA 硬件仿真平台,本文针对无线通信中OFDM(Orthogonal Frequency Division Multiplexing)系统进行了硬件仿真实现。OFDM 系统包含上行接收和下行发送两个处理流程。下行发送的流程是信道编码、比特交织、比特加扰、星座图调制、串并转换、快速傅里叶逆变换。上行接收是下行发送的逆过程。对外接口主要有以太网口,AXI4 和CPRI(Common Public Radio Interface),其中AXI4 接口用于接收OFDM 系统的配置参数,如比特交织长度、传输带宽、子载波频率间隔等,以太网接口和CPRI 用于用户业务数据的处理。针对上述OFDM 的处理环节均设置一个仿真节点,每个仿真节点会输出若干数据(由传输带宽和仿真时长决定),并拿去和参考模型的对应输出进行比对。其他仿真组件设计细节。

2.1 参考模型

基于需求说明书,采用MATLAB 开发OFDM 系统的行为级模型。

需求说明书的部分要求有:(1)支持数据速率6、9、12、18、24、36 Mbps;(2)支持调制方式BPSK、QPSK、16QAM、64QAM;(3)支持编码效率1/2、2/3、3/4;(4)每个OFDM 符号支持52 个子载波;(5)OFDM符号4 us 间隔;(6)保护间隔0.8 us;(7)导频数4 个OFDM 符号;(8)子载波间隔312.5 kHz。此外参考模型的交互接口、仿真节点位置和数量和FPGA 设计完全相同。当参考模型设计完成后灌入测试激励,将每个仿真节点的输出处理成文件并保存。

2.2 场景模型

基于MATLAB 搭建,用于生成各种OFDM 应用场景的模拟数据。

主要有用户业务数据和OFDM 传输配置参数,不同传输参数对应的业务数据也不同,每一种测试场景即对应一种传输参数和业务数据的组合。以一个功能测试场景为例,主要包含以下数据:(1)同一时隙内的三个用户语音业务数据。(2)部分传输有:2 个天线流数据;5 MHz 传输带宽;子载波间隔312.5 kHz;三个用户的业务块比特数分别为60 241,53 625 和49 681;比特交织长度32;2 号加扰序列种子;调制等级16QAM 等。性能测试场景的数据多以峰值或者超范围的参数组合为主,如需求说明书要求保护间隔0.8 μs,则具体配置成0.8 μs 或者0.9 μs,观察系统输出是否发生紊乱。将场景模型的输出数据处理成文件保存。目前针对该OFDM系统共开发了56个功能测试场景和19个性能测试场景。

2.3 仿真主控器

基于Linux C 语言开发,用于触发仿真各个节点流程、读取每个测试场景的仿真结果信息、生成仿真报告等。一次完整的FPGA 仿真需要跑完所有的测试场景,称为回归测试。回归测试用以确保原设计在缺陷修复、配置改变、代码更新后仍能符合要求正常的运行。回归测试的流程为:

(1)读取回归测试列表,获取测试场景名称。

(2)根据测试场景名称,触发场景模型,生成测试激励。

(3)对参考模型施加测试激励,保存各仿真节点输出。

(4)将仿真组件综合成比特流,烧录到XpressGXS10板卡。

(5)将测试激励和参考模型输出文件通过PCIe 接口导入到DDR4 存储。

(6)配置寄存器,启动仿真。

(7)仿真结束,读取仿真结果信息。

(8)检查回归测试列表是否读完,未读完则返回第一步,读完则进入下一流程。

(9)生成回归测试仿真报告,回归测试结束。

2.4 驱动器

基于VHDL 语言开发,用于读取DDR4 对应区域的传输参数和业务数据;并分别通过AXI4 接口和以太网接口将测试激励送入DUT,其中AXI4 接口时序如图3所示。写地址包含awaddr、awvalid、awready 三组线,当awvalid 和awready 同时为高电平时awaddr 携带的地址数据有效,写数据包含wdata、wvalid、wready、wstrb 四组线,当wvalid 和wready 同时为高电平时,wdata 携带的写数据有效,wstrb用于指示wdata 有效字节数,如当wstrb 为“1001”时,代表wdata 最高字节和最低字节有效。写回应包含bready、bresp 和bvalid,当bready 和bvalid 同时为高电平时,bresp携带数据有效,当bresp 为0 时代表这次写入成功,当bresp为非1 时代表写入错误[9]。此外AXI4 接口还可以用来读取DUT 内部寄存器,分析内部仿真状态。

图3 AXI4 接口时序

2.5 监视器

基于VHDL 语言开发,用于读取DDR4 对应区域的参考模型仿真输出文件;采样DUT 仿真节点输出,并实时将两路数据送至检验器。每个仿真节点均对应一个监视器和检验器用于适配不同时钟域和格式的比对数据。

2.6 检验器

基于VHDL 语言开发,用于比对监视器送来的两路仿真数据,并记录每个仿真节点的比对结果。当所有仿真节点比对结束后,将比对结果送至仿真记录模块。比对时序细节如图4所示,chk_ref_data 和chk_ref_req 来自参考模型,chk_ref_req 高电平时chk_ref_data 携带数据有效。chk_dut_valid 和chk_dut_data 来自DUT 对应输出。chk_counts 包含四个记录器,当chk_dut_data 和chk_ref_data 携带数据相同时,word_good_counter 加一,否则word_bad_counter 加一,chk_err 电平拉高。当这个仿真节点所有数据比对完后,chk_eof 电平拉高。

图4 DUT 和参考模型数据比对时序

2.7 仿真记录器

基于VHDL 语言开发,用于存放仿真的过程信息,仿真异常状态标志位,仿真节点比对结果等。仿真结束后,这些信息由仿真主控器通过PCIe 接口读取[10]。

各仿真组件设计好后,通过仿真主控器配置寄存器启动仿真,当所有仿真节点的数据比对正常则代表该测试场景仿真通过,开启下一个测试场景的仿真。经统计跑完75 个测试场景仿真总消耗时间在3 小时左右。对比基于UVM 的软件仿真则需要20 小时左右,可见本文所提FPGA 硬件仿真平台节省的时间是十分可观的。

3 结 论

借助XpressGXS10 硬件加速板卡的算力,本文提出了一种针对大规模FPGA 设计的硬件仿真平台。一方面参考模型,场景模型通过MATLAB 实现,保证了生成测试激励的灵活性,另一方面将运算比较耗时的仿真组件和DUT 通过硬件加速,极大减少了仿真时间。此外文章最后针对OFDM系统设计了相应的仿真流程,并介绍了该案例的仿真框架以及实现细节。本文提出的基于XpressGXS10 的硬件仿真平台可应用于各种大型FPGA 设计的仿真测试,也对未来实时快速仿真平台的搭建提供了参考。