基于FPGA的高速低噪声目标检测系统

2022-11-15陈浩林王擎宇卢振坤董艳珂

陈浩林,王擎宇,卢振坤,董艳珂

(广西民族大学 电子信息学院,广西 南宁 530000)

随着计算机视觉的发展,近年来目标检测技术被广泛应用于军工系统、安防系统以及精密仪器检测等领域,目标检测技术对图像处理速度和识别精确度的要求也与日俱增[1,2],要求图像算法尽可能占用较低的时间和空间复杂度,并要求硬件系统资源丰富以及处理速度足够快[3,4]。其实现方案通常采用指令计数器(Program counter,PC)端的软件实现,普通计算机的中央处理器(Central processing unit,CPU)主频虽能达到GHz级别,但受限于冯·诺依曼的体系结构,处理像素矩阵的速度较慢,而图形处理器(Graphics processing unit,GPU)的浮点运算虽然快,但体积和功耗相对较高[5,6]。

针对基于现场可编程门阵列(Field programmable gate array,FPGA)的视频图像目标检测技术,国内外的学者做了相关的研究工作。其中文献[7,8]分析了图像处理流水线思想和不同的图像格式对后续边缘特征提取效率影响的大小,并使用YUV、YCbCr或原始RAW相机输出格式来代替红绿蓝(Red green blue,RGB)格式,提高了算法系统在FPGA的运行速度。在数据存取技术方面,文献[9]针对数据存取速度是制约FPGA目标检测系统运行速度的重要因素问题,设计乒乓存储电路对数据进行连续存取,提高了数据存取速度。针对目标检测核心算法部分,文献[10]采用背景和帧间差分法来实现目标跟踪任务。虽然背景和帧间差分法对于静态镜头和非复杂动态目标具有良好的捕捉能力,但在搭载云台舵机的摄像头进行动态跟踪以及静态目标的搜寻情况下的表现还需改善。此外,基于FPGA的目标检测系统常采用空域点处理法,该方法在搭载云台舵机的摄像头进行动态跟踪以及静态目标的搜寻情况下表现较好,但由于空域点处理法对图像质量要求较高,对像素噪声比较敏感,因此对系统滤波算法提出了更高的要求。对此,文献[11]提出一种基于大尺寸单幅图像计算加速双边滤波的去雾状噪声的方案,对均匀分布的雾状噪声去除效果良好。文献[12]设计了快速中值滤波的FPGA实现,该方法在速度具有一定的优势,且处理一般椒盐噪点效果较好,但噪点较大或者噪声表现出一定连续性时去噪效果较为一般。文献[13]设计的系统应用了均值滤波算法,原理简单,易于实现,但容易受两极像素值和高浓度椒盐噪声影响,导致图像过于模糊和边界特征损耗较为严重。

针对滤波算法去噪问题,本系统提出了一种以3*3快速中值滤波和4*4快速分权均值滤波结合的双滤波算法,能够有效提高特征图像信噪比和目标检测准确度,为目标检测与跟踪领域提供了一种行之有效的新方法。

1 系统架构

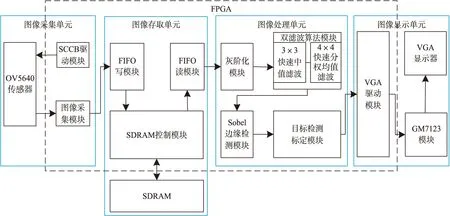

本系统所采用的核心芯片为Intel公司的Cyclone IV EP4CE10F17C8,开发环境为QuartusII 13.0,主要研究分辨率为800*480的彩色视频图像中目标的检测技术。硬件系统主要由图像采集、存取、处理以及显示4个单元构成,其系统架构图如图1所示。其中图像传感器的寄存器初始化由SCCB协议进行参数配置,数字显示接口(Digital video port,DVP)控制器对8位输入并行图像数据进行采集与位宽转换,并通过调用多个先进先出(First input first output,FIFO)的IP核进行时序同步处理,基于SDRAM手册设计SDRAM控制器对数据流进行实时存储于交换,在FPGA上实现相应图像处理算法,其中包括图像灰阶化算法、双滤波算法、Sobel边缘特征检测算法和目标检测标定算法,并根据VGA控制时序设计VGA驱动程序进行信息交互显示驱动。

图1 系统框架图

1.1 图像配置与采集单元

本系统采用OV5640图像采集传感器进行图像采集,并设计串行摄像机控制总线(Serial camera control bus,SCCB)协议对其进行OV5640寄存器工作模式、曝光时间、开窗大小等参数进行初始化配置。设计速度为400 kHz传输标准的SCCB,从机通过时钟线SIO_C的上升沿触发读取指令命令,配置信息通过八位SIO_D总线发送给从机,根据总线最后的写命令和地址位信息快速定位目标寄存器,紧接着进行数据写入,完成图像开窗大小800*480、RGB三通道输出、翻转和镜像等配置;其中SCCB状态的转换由状态机控制方法实现。

OV5640摄像头传感器像素数据输出协议为DVP,根据该输出协议本文设计了一种图像采集模块。

1.2 图像存取单元

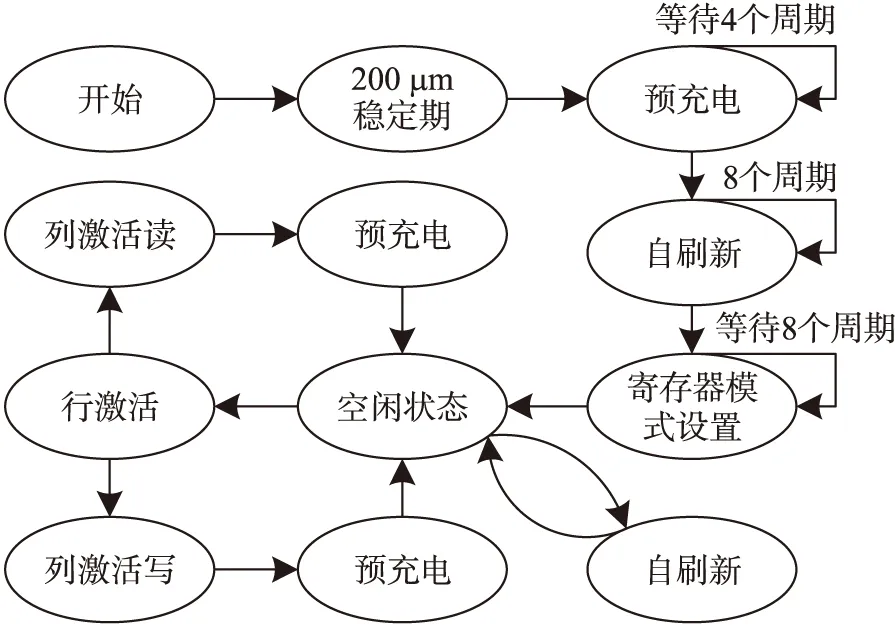

如图2所示,设计的SDRAM顶层模块包括FIFO乒乓存取模块、SDRAM控制模块和PLL锁相环模块;SDRAM控制模块包括状态控制、寻址以及数据输入模块[14,15]。SDRAM状态控制模块为核心单元,进行SDRAM初始化以及控制读写状态转换,采用三段有限状态机技术对复杂的状态转换进行有序控制,设计的SDRAM状态机状态转换关系如图3所示。

单个异步读写FIFO的数据存在排队问题,影响读写速率以及实时性,本文设计一种高实时性乒乓存储系统,在整个时间域上进行不间断存取数据,提高了系统实时性。

图2 SDRAM模块功能图

图3 SDRAM控制状态图

设计4个深度为512words,宽度为16 bits异步FIFO IP,将上一级pipeline图像数据打入FIFO_READ1,然后通过PLL倍频至100 MHz的时钟传存进SDRAM的BANK1区,与此同时FIFO_WRITE1读出数据,并利用错位时间命令FIFO_READ2读进数据,而后存进SDRAM的BANK3区,与此同时读FIFO_WRITE2依次读取,本系统由此实现数据的乒乓存取,提高数据传输的实时性。另外考虑系统传输路径延时情况,对SDRAM的时钟通过锁相环(Phase locked loop,PLL)进行90°的相位偏移,SDRAM乒乓操作如图4所示。

图4 SDRAM乒乓操作图

1.3 图像显示单元

设计了VGA时序控制和数据输出模块,其输出RGB888 pipline至DAC数模转换器GM7123,最后输出至支持VGA协议的显示器进行交互。在VGA驱动模块设计中,充分利用线性序列机的思想,分别设计深度为12的x和y方向计数器跟随矩阵像素,名为xcount_r[11∶0]和ycount_r[11∶0],以行、帧同步时序为作为VGA_BLANK置位的判断条件,接着输出有效数据,由此循环实现VGA以帧为单位的连续显示。

1.4 图像处理单元

基于FPGA进行算法设计,需依据硬件平台本身的资源可利用空间为资源上限进行设计,并移植MATLAB仿真算法RTL实现,然后对每一个模块进行功能验证、综合约束、静态时序分析、板级验证和在线调试。充分利用FPGA的流水线操作优势,达到同步处理与高速输出的效果,处理并行数据速率远高于CPU。

为实现目标检测系统,本图像处理单元需要对输入的彩色视频流数据进行一系列的处理。首先在基本保有原信息量的基础上,为减少像素数据位宽,提取Ycbcr的亮度分量进行灰阶化处理;其次,由于系统采集的图像数据随机噪声多,不经处理无法进行目标准确检测与标记,但普通单滤波算法无法满足本系统要求,因此提出并设计了双滤波算法进行滤波处理;目标边缘特征提取部分采用Sobel算子进行实现;最后设计了一种目标标定方法进行目标的标定显示。

1.4.1Ycbcr灰阶化实现

原始的彩色图像数值量大,不易进行运算,将彩色图像灰阶化实现很有必要,在降低图像位宽的同时,灰度图还保留了图像的细节特征,能有效减少运算量,提高数据处理速度,减少图像存储空间,便于后面的算法处理。

彩色图像灰阶化常用的方法有:三色均值法、最大分量法、加权平均法和转换到其他颜色空间法。本文采用加权平均进行图像灰阶化处理,将R、G和B三通道按照一定的权值比例映射到Y、Cb和Cr上,其中提取Y分量为亮度分量,其保留了图像完整的信息。由于硬件实现位数相同的需要,对输入RGB565采用末尾补0的方式输出RGB888,依据BT709协议,分量信息提取如式(1)所示

(1)

由于FPGA不支持浮点运算,因此需要对计算过程关键数倍乘整数化,对式(1)等号右边乘以256后如式(2)所示,输出Y后再复原,为减少FPGA片内运算单元,本处采用移位寄存器实现除法运算功能,Y≫8,提高运算速度,减少计算时延。经过4个时钟周期后可依次输出Y[7∶0]灰阶图像素点。

(2)

1.4.2 双滤波算法设计及其实现

因图像采集系统采集进来的实际图像数据随机噪声繁杂,需要设计针对性的滤波算法进行滤除,常用的空域单滤波算法有:中值、均值、高斯、巴特沃斯等滤波算法。其中中值滤波对椒盐噪声抑制效果较好,但对于表现出一定连续特性的高斯噪声滤除效果较为乏力。均值滤波算法有较好的平滑效果,对表现出一定连续性的高斯噪声平滑效果比中值滤波好,但高浓度椒盐噪声对平滑效果影响较大,容易导致感兴趣特征区域过度模糊或丢失,影响后续的特征提取,以至于导致目标检测效果不佳。因此本系统提出一种双滤波算法,采用快速中值滤波和快速分权均值滤波联合算法进行噪音滤除,在滤除大部分椒盐噪声的同时,同时对高斯噪声进行有效的压制,其中快速分权均值滤波比原有均值单滤波算法更能保护图像细节,以至于更精确地对目标进行特征提取和跟踪标定[16]。

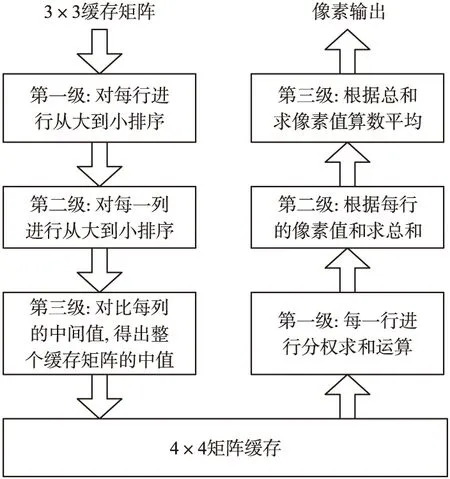

中值滤波是一种非线性低通滤波器,中值滤波器能够有效去除孤立点的椒盐噪声,并能有效保护图像高频部分的细节,但容易造成图像的不连续性,以及对非孤立噪声难以滤除[17]。本系统前置滤波采用3*3卷积核模板进行中值滤波,应用shift register IP核进行3行缓存方式临时动态存储,对模板内的9个数值进行快速排序硬件化实现,并取中间值代替实时位置像素点,实现中值滤波效果,3*3卷积核生成模板如图5所示。

图5 3*3快速中值滤波模板

常规的中值滤波算法是对整个卷积核的数据进行遍历排序求中值,这种方法工作原理虽然简单,但是其运算速度慢,时间复杂度较高,严重影响系统性能。本系统采用三级流水线进行中值计算,仅约90 ns即可完成一个像素的中值的计算,提高系统实时性。其中第一级对三行分别通过选择电路进行数值大小判别,得出一行的最大、中间以及最小值,同理分别求出第二行和第三行;第二级流水线对每行的最大、中间以及最小值再进行由大到小的排序;第三级再对比每一列的中间值推算真实中间值,根据可能的3种情况进行多路判断输出。

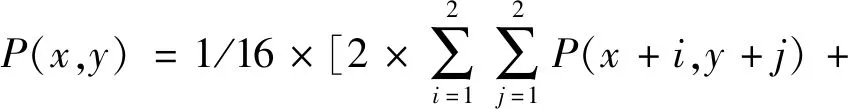

均值滤波器也是一种低通滤波器,能够平滑大部分集中在幅度谱高频和中频段的噪声,具有较好的平滑效果。针对通过中值滤波后已去除大部分孤立的大值椒盐噪声点的数据,再进行均值滤波,将提高图像平滑后的图像质量,但均值滤波器不可避免的会对图像边缘造成不同程度的破坏[18-21],因此本系统利用shift register IP 核设计一种4*4快速分权均值滤波器。4*4快速分权均值滤波模板如图6所示,在成功滤除大量随机噪声的同时,保护边界特征,不影响目标检测的精度。其数学表达式如式(3)所示,P(x,y)表示4*4卷积核的首个像素点,由式(3)实现图像分权均值滤波功能。

图6 4*4快速分权均值滤波模板

(3)

如图6所示,首先设置一个四通道,宽度为8位,深度为800的每行可溢出数据的移位寄存器,数据随33.3 MHz的CLK时钟信号逐个输入,溢出部分传递到Ⅱ形成4*4均值滤波模板,对Ⅱ各位置的数值进行Ⅲ步骤所示的分权计算。对四角的像素进行去除操作,紧接着对中心2*2的像素数据进行2倍乘操作,这样做的好处是减少4*4均值计算模板带来的边缘模糊,方便后续的算法处理。

此部分通过三级流水线进行实现,其中第一级流水线对每行进行分权求和运算,第二级对每行的和进行求总和,第三级对总和值求平均。FPGA 调用乘除运算耗费时间较长,面积和功耗较高,在第一级内用加法资源代替2乘计算,在第三级作均值求平均的除法操作时,充分利用FPGA移位寄存器的便利性,去除输出口mean_data低三位,既是mean_data≫3,达到除以16的等价效果,并有效减少了系统时延。

由快速中值滤波和分权均值滤波算法共同组成的双滤波算法FPGA实现流程如图7所示,可实现可调控像素位宽的输入输出控制,整个流程采用流水线思想进行设计,有效提升算法在FPGA上运行时的最高主频,提高系统运行速度,采用时序逻辑可以有效减少竞争冒险现象以及较好的滤除毛刺,减少亚稳态的产生以及传播,以保证时序电路的质量。

图7 双滤波算法FPGA实现流程

1.4.3 Sobel算子实现

图像边缘检测技术是图像处理和计算机视觉等领域中最基本的技术,其效果直接影响着后续图像识别的准确性。目前图像边缘检测技术大致分为三类:第一类是借助于空域差分卷积或类似卷积的运算来实现的方法,第二类是从能量的角度考虑以能量最小化为准则的分割算法,第三类是以小波变换为代表的分割算法[22]。本系统采用的边缘检测算法为第一类的Sobel算法,来提取感兴趣区域(Region of interest,ROI)区域的边缘。

假设连续函数为f(x,y),函数在(x,y)处的梯度是具有方向和大小的梯度矢量,如式(4)所示

(4)

为了提高运行速率,采用简化计算方法,如式(5)所示

(5)

运算后的f(x,y)如式(6)的矩阵数据所示,其中满足{f(x,y)|x∈[1,m],y∈[1,n]}。

f(x,y)=

(6)

计算出的grad[f(x,y)]值即为图像的边缘数据,因为式(6)是对连续的图像的边缘信息。在实际应用中,采集的图像为一定像素大小离散数据,因此在图像处理中,常用相邻或间隔像素差分值来代表图像的边缘信息。而Sobel算子是对离散数据进行加权计算,采用3*3的分别为水平方向和垂直方向的卷积模板,利用模板与对应的图像数据进行加权计算,这2个方向模板分别为水平方向和竖直方向边缘检测。

其硬件实现步骤如下:

第一级将移位寄存器shift register溢出的3*3实时数据与垂直和水平梯度方向3*3的矩阵算子作对应值作卷积运算;

第二级分别对水平和垂直卷行积结果进行相加求和;

第三级调用SQRT IP核进行开方求实时像素梯度值,作为图像的灰度值,并设定阈值Abs_mag,取值20 1.4.4 目标标记 目标标记的方式为外接最小矩形框,这个矩形框可以跟随目标自动移动,达到目标标定跟踪的效果。 其实现过程是:基于滤波算法以及形态学边缘检测后的边缘特征灰度图像上,根据FPGA流水线思想,从(0,0)开始到最后一位像素值进行遍历,并匹配每一位像素,每当遇到一个有效数据,比当前存储的横坐标最大值大及最小值小,纵坐标最大值大及最小值小时,则将其同步计数器所产生的坐标数据和其像素值进行存储,最后得到每一帧图像的目标四个最边界有效坐标点,以四者为其边缘限定进行矩形框框定,并通过平均思想求得近似形心(Central_X,Central_Y),可以根据其离中心像素(400,240)的差值来确定位置,并输出相应的PWM波形来控制二自由度云台舵机进行目标的物理跟踪,直到形心离中心点x方向为±5,y方向为±5内,视为目标收敛,舵机停止运动。 系统主要包括图像采集、图像存取、图像处理以及图像显示四大模块,首先通过MATLAB软件进行系统仿真,计算系统运行速度,并与FPGA进行速度对比,然后对图像处理的算法效率分别进行仿真比较,最后对系统进行FPGA板级验证效果对比。 PC端硬件系统核心为i7-7700CPU,最高主频3.60 GHz,在PC端MATLAB中测试十组800*480的图像,调用tic、toc运行时间函数,统计运行时间,根据试验数据求出平均速度为0.455 s,FPGA系统运行目标检测任务速度可达0.016 s,FPGA是PC端运行速度的28.4倍,具有一定的速度优势,。 为了检验系统去噪效果,采用峰值信噪比(Peak signal noise ratio,PSNR)作为衡量噪声指标[23],其值越高,表明在同等情况下去噪效果越好。由于目标检测标记的准确度直接与边缘特征图的质量相关,将4种不同的滤波算法对同一张加了不同椒盐浓度的图进行滤波,并将边缘检测后的特征图进行信噪比分析,MATLAB仿真测验的结果如图8所示。 图8 各算法峰值信噪比 由图8可分析出滤波后的图像效果:在噪声主要发生带即椒盐噪声浓度为20~70%之间,采用的5*5高斯滤波以及传统4*4均值滤波表现欠佳,3*3中值滤波表现总体上优于5*5高斯滤波以及4*4均值滤波,但双滤波算法总体上优于其他3种滤波,计算并统计图8的平均信噪比,算得双滤波算法比其他3种单滤波算法的平均信噪比高出约2.6倍,具有一定的优势。通过对整个系统流水线Register延迟计算,得出正常传输状态下数据从OV5640摄像头输入到VGA显示响应过程延迟约为10.742 μs,而人眼可感知视觉延迟需到毫秒级别,因此本设计满足系统实时性要求。 将主观评判对比分为两组,在同一带污渍墙壁背景下,(a)、(b)组和(c)、(d)组分别是第一和第二组,有目标组目标为二自由度舵机云台,如图9所示。 图9 试验结果对比 图9中,(a)和(b)对比了双滤波算法和3种单滤波算法中平均信噪比最高的中值滤波算法噪声滤除效果,若滤波后依然有噪声,则噪声会被绿色框标记显示;(c)和(d)对比了双滤波算法和中值滤波算法在有目标条件下,对比目标检测的准确度,突显出滤波算法的优劣。 首先,从图9(a)中可以观察到,使用双滤波算法无包围盒产生,即无信号被检测,而图9(b)产生包围盒,表明滤波后依然有随机噪声,引起误差。从图9(c)中可以观察到,二自由度云台舵机被包围盒准确标记,而图9(d)的二自由度云台舵机被过度标记,无法定位具体目标位置。 由FPGA板级验证测得,根据仿真信噪比排名次优的中值滤波算法无法满足实际要求,目标标定效果差,而双滤波算法可以满足系统要求,能够像如图9(c)准确跟踪目标。因此,双滤波算法具有更好的去噪效果,能显著提高后续目标检测与标记的精度,双滤波算法比其他3种滤波算法适合本目标检测系统,具有较高的应用价值。 针对目标检测系统对速度和精度要求高的问题,本系统采用了FPGA平台进行处理,利用其高效的并行计算以及流水线架构,有较高的速度优势,并与PC端MATLAB仿真进行对比,突出本系统速度优势。本文提出的双滤波算法,在系统中去噪效果较好,设计的双滤波算法用于特征图比其他3种单滤波算法的平均信噪比高出约2.6倍,目标检测精度高,为目标检测与跟踪领域提高了一种行之有效的新方法。2 仿真及试验验证

2.1 算法仿真

2.2 试验验证

3 结论