一种具备良好电磁兼容性的晶振滤波电路设计*

2022-10-31张子春刘婷婷赵勤学

张子春,刘婷婷,王 滨,赵勤学

(航空计算技术研究所,陕西 西安 710065)

0 引言

电子设备的电磁兼容性指的是设备自身能够维持高效能工作并且在共同的电磁环境下不干扰其他设备正常工作的能力。相对于地面电子设备电磁环境而言,航空计算机所处的电磁环境更加恶劣。此外随着我国航空工业的发展进步,航空计算机的功能愈发复杂,计算机系统数据处理的速率越来越高,相应对计算机系统的电磁兼容性要求越来越严格。

计算机系统中几乎所有的微处理器、CPLD/FPGA、以及DSP等数字集成芯片都采用晶振电路为系统提供时钟脉冲。晶振电路被誉为计算机系统的“心脏”,其电磁兼容性能的优劣直接影响计算机系统的工作速率和精度[1]。

计算机系统中的多个设备同时工作时会引起很高的电磁辐射,晶振电路作为系统时基,需要持续性输出方波信号,通常是系统中最容易产生电磁辐射的部位。如果晶振电路设计不合理,其产生的电磁干扰将愈发严重,使系统处于紊乱工作甚至瘫痪状态。针对现有的晶振电路缺乏规范化设计,尤其是在PCB板中的设计很少考虑到晶振的电磁兼容性,以致于在系统电磁兼容实验中经常出现晶振对应频点及其倍频点电磁辐射超标的问题,因此本文将以晶振滤波电路为例,研究晶振电路的最佳滤波方式,寻求具有完备电磁兼容性的晶振滤波电路设计,以此提高晶振电路的EMC性能。

1 晶振原理及滤波电路设计

石英晶片安置在一个支架上,通过电路产生电极,加以金属外壳进行封装,就形成了石英晶体谐振器,也叫晶振[2]。常见的晶振电路基本组成框图如图1所示,主要包括以下几个部分:供电电路,滤波电路,振荡电路和匹配电路[3]。由于计算机系统上电后晶振电路持续性工作为系统提供时钟信号,晶振的电磁辐射问题很严重,为了降低晶振电路的电磁辐射,提高系统电磁兼容性,常用的方法有改善PCB板布局和布线、提高系统屏蔽性能、改变接地方法以及设计滤波电路等。

图1 晶振电路基本组成框图

电源系统在为晶振提供能源输入的同时,也将电源系统的噪声耦合到晶振电路上,所以在电源输入端必须设计滤波电路,在源头降低晶振的电磁辐射[4]。为了在晶振设计阶段降低晶振电路引起的电磁辐射,要求晶振的滤波电路根据输出时钟信号的频率进行特定设计,在PCB走线时,要求滤波电路尽量靠近供电电路,走线尽可能缩短等等,此外要求晶振电路有完整的参考平面[5]。

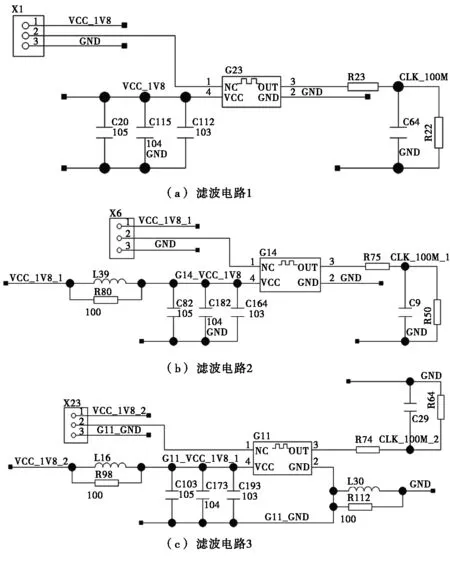

晶振的无源滤波电路主要通过电容、电阻和电感相组合的方法进行多种设计。为了研究滤波性能和电磁兼容性俱佳的晶振滤波电路,本文主要设计了三种滤波电路,如图2所示:图2(a)晶振供电端加三级电容滤波,滤波电容地与晶振地共地;图2(b)晶振供电端三级电容加电感电阻混合滤波,滤波电容地与晶振地共地;图3(c)晶振供电端三级电容加电感电阻混合滤波,滤波电容地与晶振地通过电感电阻并联接地。晶振电路滤波电路设计不好,在相同结构件屏蔽性能下,有可能导致晶振电磁辐射发射超标。

图2 晶振三种滤波电路

2 实验结果及分析

2.1 滤波电路的滤波效果分析

输入滤波电路用来降低电源传输路径上的噪声电平,进而降低电源线上的电磁辐射。对于晶振电路而言,设计完备的滤波电路可以从源头降低电磁辐射。三组电路采用同种型号晶振产生频率为100 MHz的信号,在PCB中采用8层板设计,TU752为介质材料,铺以1盎司铜层,均采用完整的电源和地平板作参考层。通过提取整板参数、定义端口网络、计算S参数模型,进行三种滤波电路滤波效果对比。

采用仿真工具,对晶振电路PCB板进行无源特性S参数提取,再通过三种滤波电路对电源系统进行滤波处理,最后添加晶振器件驱动模型进行电路信号仿真,到达晶振供电pin脚处的电源信号如图3所示。通过对比发现滤波电路1滤波后的电源信号维持在1.8V附近且电源抖动较小,滤波电路2效果次之,滤波电路3效果最差。滤波电路1通过对晶振的电源输入进行滤波,有效降低了输入电源的噪声和抖动,从晶振输入端降低了电磁辐射。晶振输出端pin脚处的信号对比如图4所示。通过晶振输出信号的上升沿及保持时间对比发现,滤波电路1对应晶振输出信号的上升时间最短,保持时间最长,上升时间短有利于信号判别,保持时间长更有利于数据信号的采集处理,所以滤波电路1的滤波性能更好,滤波电路2次之,滤波电路3最差。

图3 晶振输入端信号

图4 晶振输出端信号

2.2 晶振电路EMC分析

为了直观反映不同滤波电路对于晶振电磁辐射的影响程度,将上一节中晶振电路的信号仿真结果调用进行PCB板电磁辐射仿真,根据国军标要求设置1MHz~2.2 GHz仿真频段,在PCB板表面3 mm处空间区域进行场级仿真,得出不同滤波电路对应的晶振磁场强度,仿真结果如图5所示。

采用电磁仿真工具,将得到的晶振电路信号参数调用并且进行磁场分析计算,仿真了从1 MHz~2.2 GHz频点对应的磁场辐射结果,包含了时钟信号的基频以及11倍频频点,选取基频100 MHz处的磁场辐射结果进行对比。为直观表示晶振电路的磁场强度,分别就晶振的电源pin、使能pin、地pin以及输出pin处的磁场大小在表1中进行显示。对比分析结果可以得到,采用滤波电路1滤波后晶振电源pin、使能pin、地pin以及输出pin处磁场辐射均最小,滤波电路2效果次之,滤波电路3效果最差。所以滤波电路1的电磁兼容性更好,滤波电路2次之,滤波电路3最差。

表1 晶振pin处磁场强度

3 结论

计算机系统产生电磁干扰的三个要素为:电磁干扰源,干扰传播路径和易干扰设备。晶振属于产生电磁干扰的元器件,极易对系统其他设备产生电磁干扰,影响整个系统的性能。对晶振的滤波电路进行规范设计可以有效降低晶振电路辐射超标的风险,使系统满足国军标规定的电磁辐射要求。本文中晶振采用供电端加三级滤波电容,滤波电容地与晶振地共地的滤波电路可以有效降低电源系统噪声耦合到晶振电路的可能性,从而提升晶振信号的精度,降低晶振电路的磁场辐射强度,最终提高航空计算机系统的可靠性。