一种低功耗实时时钟RTC设计

2022-09-09戴澜周子坤

戴澜 周子坤

(北方工业大学 北京市 100144)

1 引言

实时时钟RTC是一种提供精确时间信息的集成电路模块,具有精确性和低功耗的特点。RTC在众多应用场景如安全系统、电表、工业设备、测量设备、办公设备、医疗设备中都作为独立的时间信息源。随着RTC更多的被应用与可穿戴设备或低功耗移动终端设备,对其低功耗设计的研究愈发受到关注。

国内对RTC低功耗设计的研究主要集中在对同步时钟门控和低功耗UPF设计方案的研究上。这两种设计方法都属于同步电路的低功耗优化方案,需要增加特定的电路结构实现时钟域和电源域的划分并增加了芯片面积。

Link-joint异步自时钟电路模型是一种基于异步握手信号流水线结构的通用异步握手电路模型。这种异步电路模型相对于同步电路具有更低的开关活动性和更加灵活的电路结构设计方法。目前少有论文通过引入该异步电路模型提升RTC的低功耗性能。

本文通过使用Link-joint电路模型设计RTC的数据通路和控制通路,使其电路结构更加简化,并降低了开关活性和电路面积,从而在设计层面降低了RTC芯片的总功耗。

2 Link-joint异步自时钟电路模型

Link-joint异步自时钟电路模型是一种由握手控制Link单元和流控制Joint单元组成的异步握手电路模型,如图1所示。

图1:Link-joint异步自时钟电路模型

Link单元包括数据部分和控制部分,Link单元的控制部分是一个Link握手信号控制器。Link握手控制单元有两个输入信号Fill、Drain和两个输出信号Full、Empty,其中Fill信号也作为Link单元内数据部分的本地自时钟信号。

Fill和Drain信号以上升沿的为有效触发信号,分别由于Link单元的“填充”和“排空”,Full和Empty以高电平输出为有效状态输出。对于同一个Link握手控制器,它的Full和Empty始终是相反的。如果Full=1,代表Link单元的状态是“满”,所控制的数据输出有效,当Empty=1时,表示Link单元的状态是“空”,表示所控制的数据输入有效。

Link控制单元一般是一个SR锁存器,也可以是Click单元或MouseTrap握手单元。Link单元的数据部分可以是寄存器或者锁存器,有时根据设具体设计需要,Link单元也可以没有数据部分。

Joint单元是控制通路的流控制模块,用于控制握手信号和状态在流水线前后级Link单元间的专递。对于简单的直线型Link-joint异步自时钟微流水线,它的Joint单元就是简单的二输入与门,对于具有分支和循环结构的复杂控制通路,Joint单元的逻辑可以通过状态转换表分析产生。

与同步电路的静态时序分析STA方法不同的是异步自时钟电路的时序分析是基于相对时序分析RTA进行的。并且电路的时序约束也需要通过相对时序约束RTC进行描述。

与同步电路模型的状态机加数据通路的设计方式不同,异步Link-joint电路模型使用Link和joint单元构造自时钟握手信号控制网络,简化了电路结构的复杂度和器件开销,在保证电路功能和时序约束的同时,最大程度上减少了流水线中寄存器和锁存器的数量,并增加了系统设计的灵活性。

3 RTC的低功耗设计

3.1 异步自时钟计数器

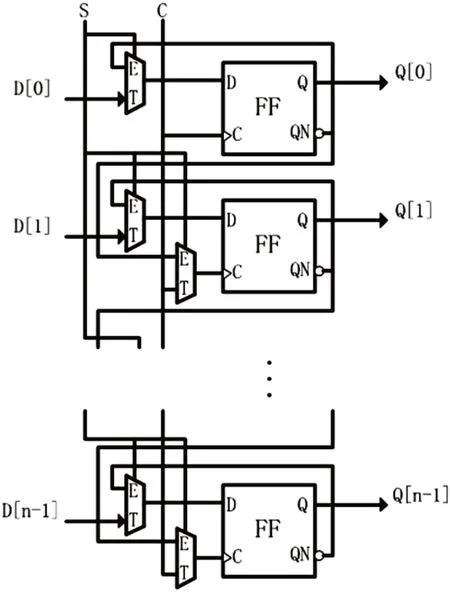

基于Link-joint电路模型的异步自时钟计数器分为控制通路和数据通路两个部分,它的控制通路由Link和Joint单元组成,数据通路部分则是一个异步计数器链,如图2所示。

图2:异步累加计数器链

异步计数器链由一组寄存器链和两组数据选择器构成,计数器有计数和设定两种工作模式,并通过输入信号S控制,计数器的时钟输入C在计数模式和设定模式下分别作为寄存器组的进位信号和同步设定控制信号。

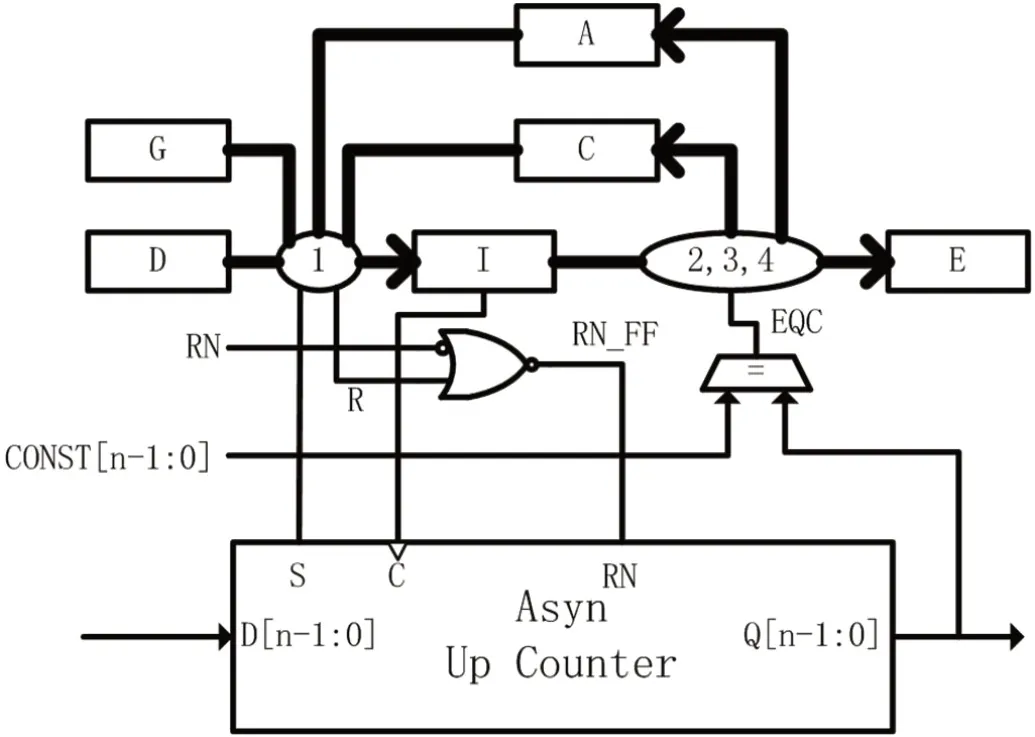

异步自时钟计数器的控制通路通过具有条件分支的循环Link-joint环路连接实现,如图3所示。

图3:自时钟计数器的控制通路

每一个计数器的控制通路有一个时钟采样输入Link单元G,用于采样输入时钟信号或连接上一级计数器的进位Link。设定输入Link单元D用于保存计数器的设定数据并触发计数器进入设定模式,它的Full信号连接异步计数器的设定选择信号S。两个没有数据部分的标志Link单元A和C分别表示计数器的数据更新和清空操作。累加Link单元I作为累加器自时钟信号的产生单元,它的Fill信号连接异步计数器的时钟输入C。进位标志Link单元E用于表示计数器的数值已经达到所要计数的数值,是下一级计数器的时钟采样单元。

控制通路的有Joint单元1、2、3和4,分别由于触发Link单元I,C,A和E的“填充”。控制通路存在3个分支和两个循环,分别是清空进位环路和累加环路。清空进位环路由Link单元G、I、C和E组成,累加环路由Link单元G、I和A组成,数据比较器EQC用于比较计数器的输出是否等于计数终值的设定输入CONST,当计数器数值不等于计数终值EQC为0,此时计数器处于累加模式,控制通路的累加环路处于开启状态,当计数器的数据等于计数终值时EQC变为1,计数器进入清空进位模式,清空进位环路开启。

不论控制通路处于清空进位模式还是累加模式,只要Link单元D的状态变为“满”,计数器都会进入设定模式,“满”状态直接通过Link单元D转递至Link单元I。

3.2 RTC整体设计

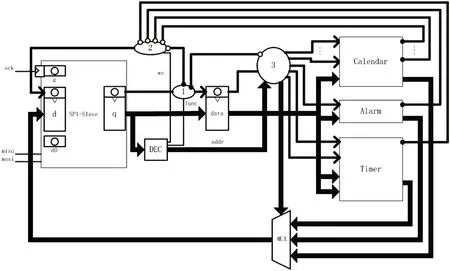

本RTC使用异步SPI从模块作为芯片和外界其他系统的数据输出接口,通过SPI接口可以对RTC进行立即数设置和指令推入,同时通过SPI接口也对主控制设备返回指令的执行结果,RTC整体控制通路如图4所示。

图4:自时钟计数器的控制通路

除了SPI从接口模块,RTC内部还有指令解码模块,立即数缓存,异步自时钟计数模块,异步自时钟闹钟中断模块,定时器时钟选择模块,异步自时钟定时中断模块和输出数据选择器。这些异步自时钟模块各自的控制通路以Link单元作为接口,RTC内部通过流控制网络将它们的控制流连接成为一个整体Joint自时钟控制单元。

3.3 Link-joint异步电路综合

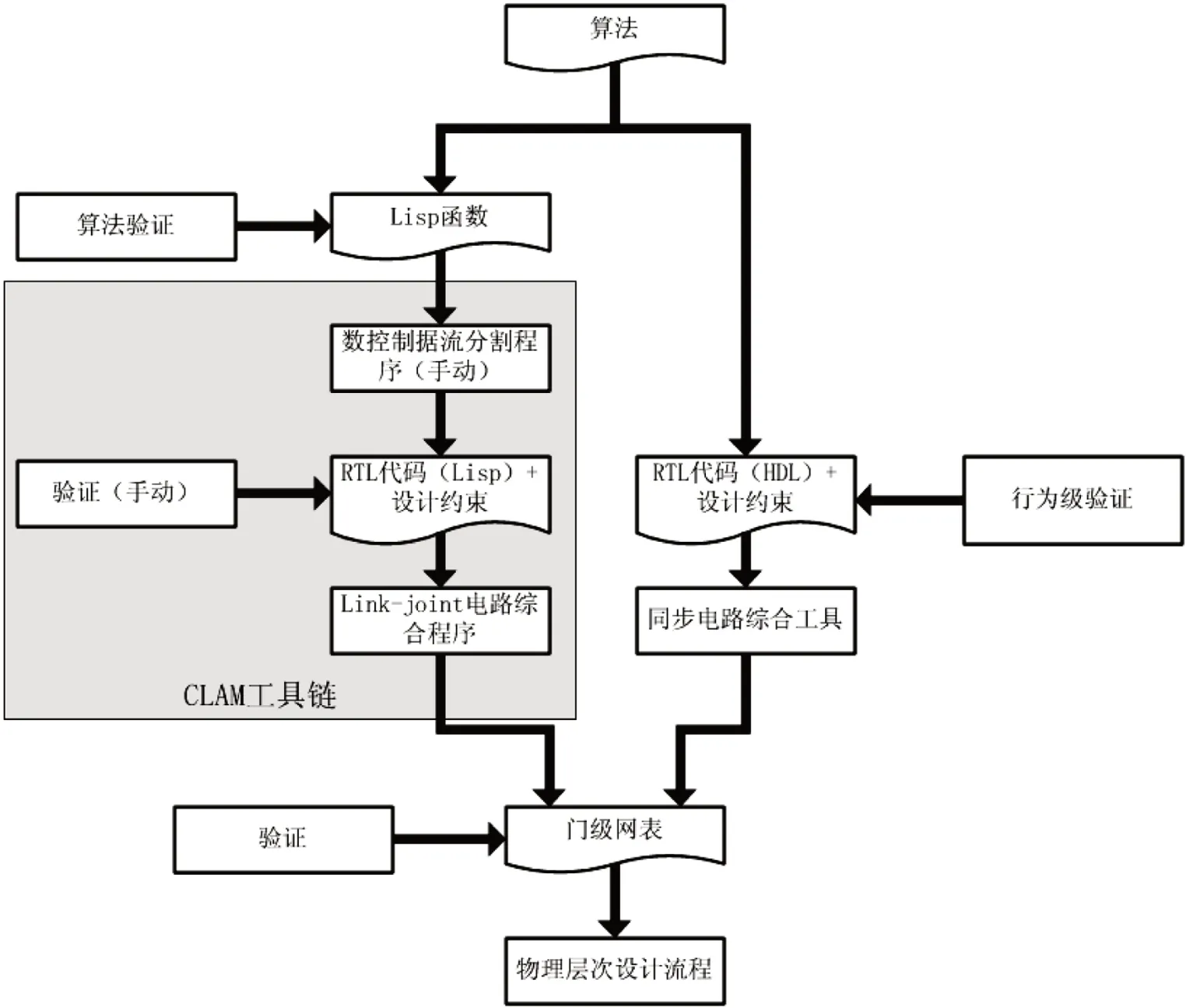

本异步RTC的Link-joint异步自时钟电路系统设计使用Lisp语言开发的CLAM工具进行综合,基于CLAM工具的综合流程如图5所示。

图5:CLAM异步电路自动综合流程

CLAM使用Lisp语言对异步自时钟控制通路的结构和状态转换行为进行RTL描述,数据控制流分割程序通过识别RTL描述中的Link定义和状态转换关键字分析和产生自时钟数据通路的拓卜结构和各个Link单元的状态转换表。同时基于Lisp语言的RTL描述也对转换过程中各个Joint单元所绑定的计算单元的延迟进行设定,以确保综合结果所实现的功能的正确性。最终Link-joint电路综合器根据数据流分割程序和延迟匹配程序所产生的状态转换表和延迟绑定信息生成控制通路的电路网表。

本异步自时钟RTC的控制通路和数据通路通过CLAM异步工具进行综合,并使用函数化的设计方法将各个异步模块进行参数化定义,逐模块进行设计综合和仿真验证,最终通过函数调用的方式将各个模块的异步控制网络在RTC顶层模块的总体控制通路的设计中进行合并,产生最终的综合结果。

4 实现结果与结论

本异步方案实现的RTC,使用Lisp语言编写RTL代码,通过CLAM平台对RTC的计时模块和整体的功能进行仿真验证,并与寄存器级相同的使用Verilog HDL语言设计并通过Synopsys的DC工具综合产生的同步RTC进行结果比较,显示其功能正确性并对比它们的低功耗性能。

本文使用Synopsys的PT工具来进行功耗分析。分析时需要布局布线后的网表文件、库相关文件和翻转率saif文件作为输入。本文不同方案的RTC都采用SMIC 55nm工艺库,同时在tt工艺角、电压1.2V、温度25℃的条件下,异步方案采用CLAM工具链进行综合,同步方案采用Synopsys的DC进行综合,然后两者的综合结果通过Synopsys的ICC进行布局布线并得到具有延迟信息的网表文件,翻转率文件通过后仿真得到,其中包含电路各个节点的翻转频率和次数等信息。由于受到仿真精度和速度的限制,后仿真中1Hz的时钟输入连接1MHz的时钟信号。表1显示了在1MHz时钟频率下的RTC计时模块面积和PT报出的功耗评估结果。

表1

异步RTC的计数模块的总面积为3054.6μm,其中计数模块的面积为922.32μm。在1MHz的时钟输入频率下,功耗分析的结果显示,异步RTC的计时模块相对于同步实现的开关功耗减小了约81.41%,短路功耗减小了86.06%,静态功耗减小了27.78%,总功耗减小了85.08%。由此可知,异步RTC的面积和功耗均相对于同步RTC有大幅度降低。

5 总结

本文基于Link-joint异步自时钟电路模型设计了一款小面积低功耗实时时钟RTC,提出了基于状态转换表的Linkjoint握手网络的设计和综合方法,并通过该方法实现了一种小面积低功耗的自时钟计数器和计时单元。通过异步电路模型和设计工具实现的RTC计时模块相对于同步实现,面积和功耗均大幅降低。