微波信号处理板全国产化硬件设计

2022-09-09赵亚斌

赵亚斌

(中国电子科技集团公司第二十研究所 陕西省西安市 710068)

1 系统组成

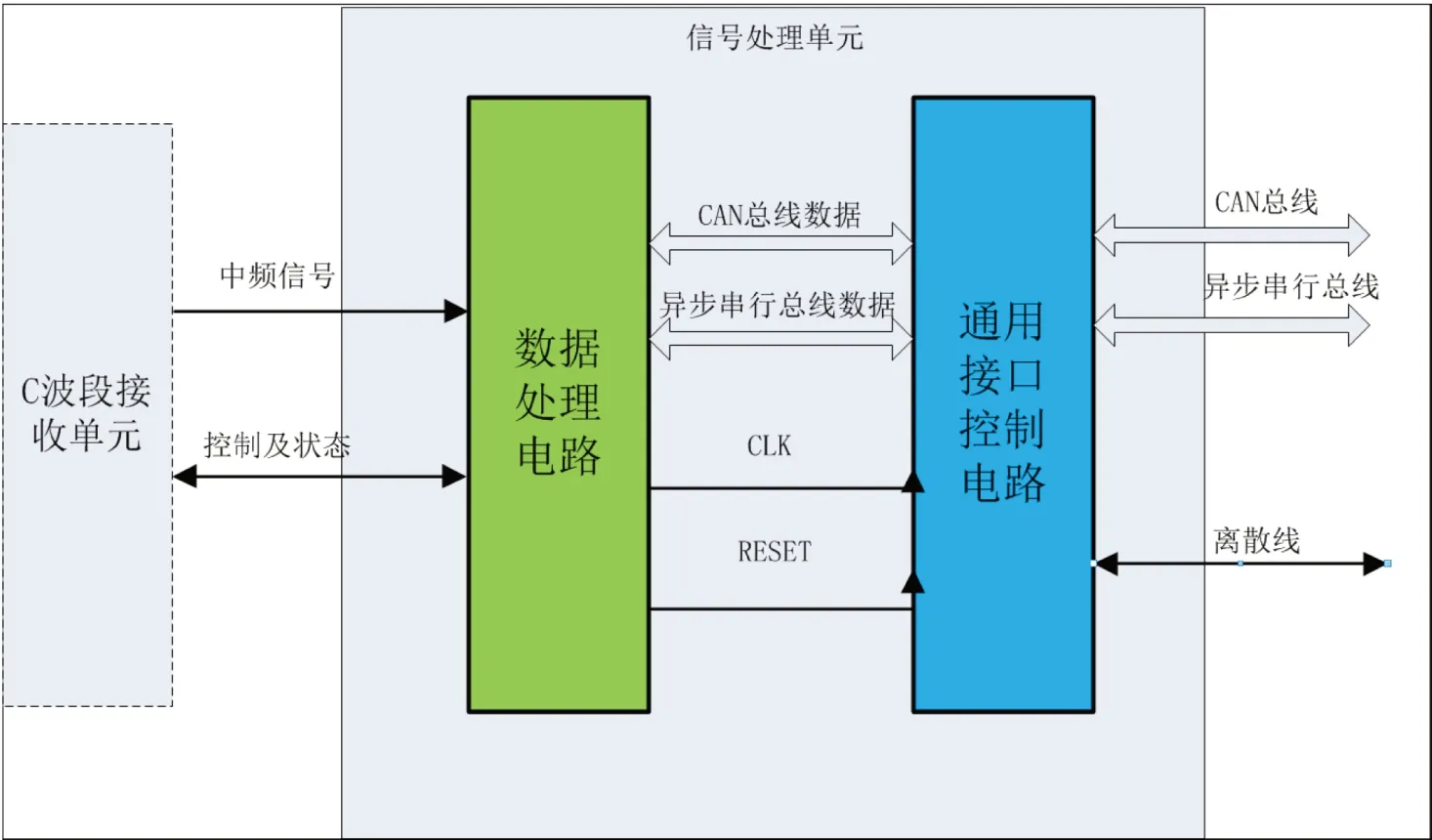

微波信号处理板由数据处理电路和通用接口控制电路组成,数据处理电路采用高速A/D转换器、大规模FPGA、DSP作为基本电路构成方式,另外包含存储电路、状态监测、总线接口、AGC控制、电源和时钟等电路功能;通用接口控制电路完成与系统总线之间LVDS异步串行总线和CAN总线数据传输通信,对外支持2路LVDS异步串行总线和2路CAN总线(A、B冗余备份)接口。数据处理电路由A/D转换电路、DSP和FPGA组成的基带解调处理电路和功能信号处理电路组成。主要用来完成70MHz中频信号的采样、数据处理及存储、状态监控和增益控制等。系统结构示意图如图1所示。

图1:系统结构示意图

2 硬件设计

本系统选用1片深圳国微公司的SMQ4VSX55FF1148,1片成都华微公司的HWD6SLXSIP-A以及1片国防科大的FT-C6416为处理核心。存储芯片(FLASH)选用深圳国微的SM29GL512M以及SM48LC32M16M。采用中电58所的JAD9268-100作为采样70M中频信号的A/D转换芯片,并选用D/A转换电路选用中电24所的SDA7226实现AGC模拟量的产生和自检调幅信号的产生,电源模块则选用国产化的HCE4644。

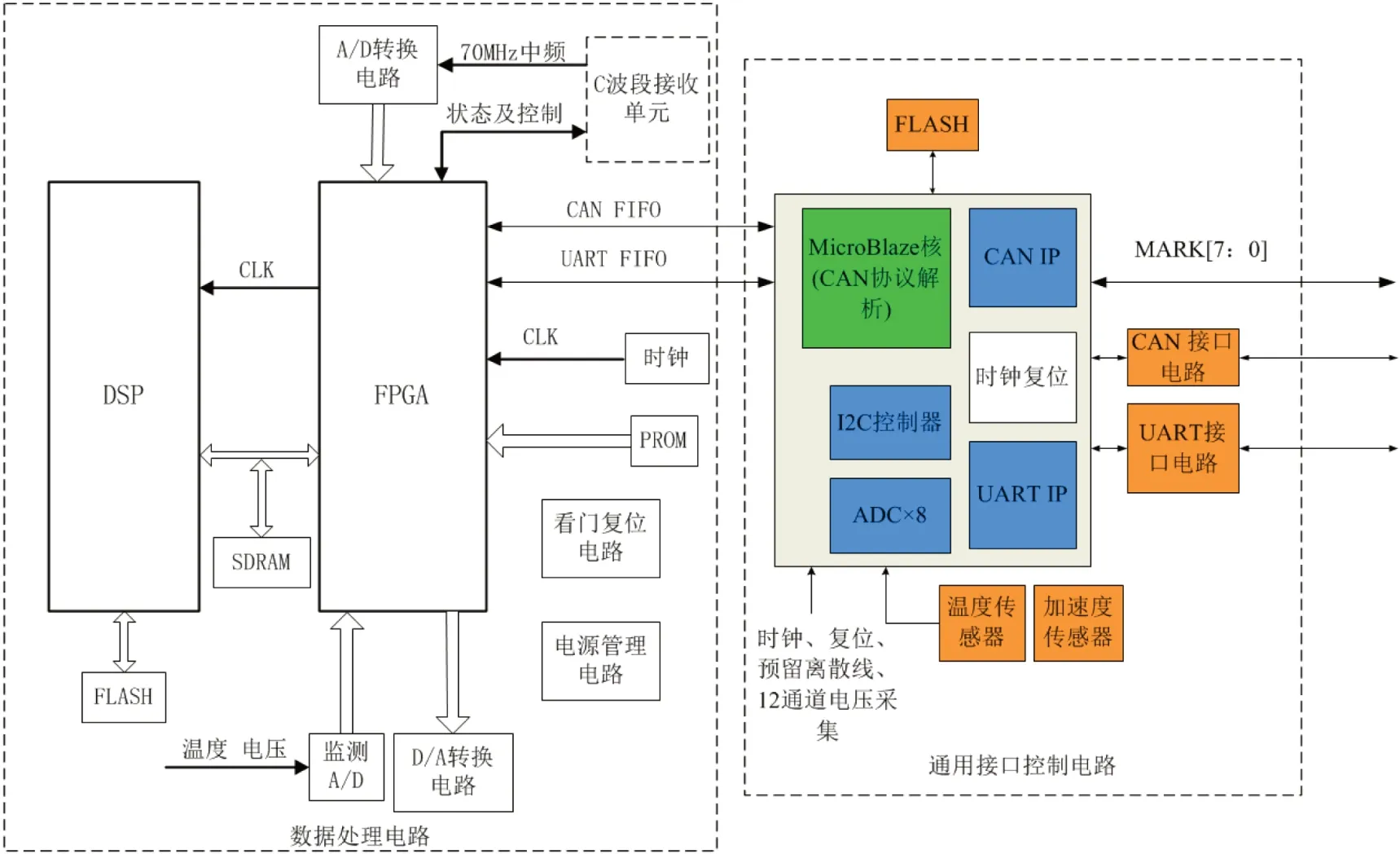

本系统设计了1路A/D转换电路,完成70MHz中频信号A/D采样;设计了基于FPGA+DSP架构的数据处理电路,其中,FPGA可以完成测角功能的数字滤波、信号抽取、幅度解调、相位解调、峰值检测、时间测量、信号鉴相等数字信号处理,执行数字信号处理器的底层控制软件,构建双口RAM、产生硬件逻辑控制和工作时钟分配等控制信号。而DSP根据巴克码功能定时和功能识别码启动功能置信度判决,进行往、返扫描波束脉冲时间间隔的测定和角度解算;进行着陆或着舰坐标变换,产生飞机相对着陆点或着舰点的方位、仰角和距离信息。设计了监测A/D电路,监测信号包括温度传感器监测信号、工作电源监测信号和C波段接收单元传递来的模拟量监测信号,其中关键器件(如FPGA、DSP等)应安装温度传感器,并将其安装于发热芯片大面积覆铜的焊盘附近;设计了D/A转换电路,实现AGC模拟量的产生和自检调幅信号的产生;设计了存储电路。PROM在进行FPGA的程序调试时使用,SDRAM储存DSP运行过程中的动态变换数据,FLASH中储存全部FPGA程序和DSP程序,可以存储当前工作模式、工作参数和故障代码;设计了异步串行FIFO和CAN FIFO电路,完成与通用接口控制电路之间的数据通信;设计了看门复位电路,完成看门狗、上电复位功能,具有手动复位功能,同时可接受外部系统对模块的统一复位;设计了电源管理电路,完成电源滤波、电源保护、电平监测、DC/DC转换和加电控制功能;设计了时钟电路,提供数据处理电路的时钟供给;设计了自检电路,满足系统对加电自检、周期自检和启动自检的需求。本板电源采用连接器提供的数字5V电源,二级电源转换主要为上述芯片供电。硬件结构如图2所示。

图2:硬件结构图

2.1 通用接口设计

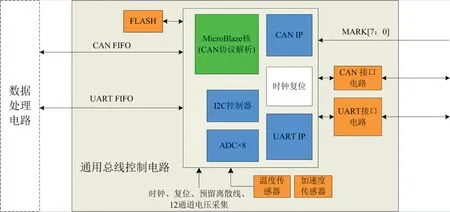

本板对外有两路低频接口,1路是对外低频接口,另1路是与C波段接收模块之间的低频接口,为低频与射频混合连接器,射频接口用于传输70MHz中频信号。通用接口包含LVDS异步串行总线,2接收,2发送,收发具备使能控制且速率可调,默认3.125Mbps,LVDS差分信号经Buffer后以单端形式连接到FPGA,用以测量数据、记录数据的上传,基于FPGA的LVDS异步串行和CAN协议解析和数据交互电路和相应的配置和管理功能;CAN总线,2路CAN总线接口互为备份,传输速率为1Mbps实现模块的状态管理,如BIT检测、健康状态查询及结果回传、电子标签查询及结果回传和模块日志查询及结果回传等,LVDS异步串行总线和CAN总线总线驱动电路,实现2路LVDS异步串行总线和2路CAN2.0B总线(A、B冗余备份)总线与系统之间的通信,1路CAN FIFO和1路UART FIFO接口,经协议解析处理后的总线数据通过FIFO接口与数据处理电路进行交互。写入发数 FIFO实现总线数据的发送,读取收数FIFO实现总线数据的接收;模块识别编码接口,用于识别信号用于识别模块在系统中的插槽编码;调试接口,包括FPGA的JTAG接口和必要的测试口,DSP的JTAG接口和RS232调试口。调试接口在信号处理单元上设计成较方便使用的插针或连接器,便于与仿真器连接;并设置其他用户接口包括时钟、电压采集、调试接口和备用接口等。通用接口控制电路原理框如图3所示。

图3:通用接口控制电路原理框

2.2 FPGA+DSP架构电路设计

FPGA与DSP主要完成本板的数据处理功能。数据处理功能要求与C波段接收单元和信号处理软件配合工作,完成对数字中频信号的处理,实现微波着陆着舰方位、下滑信号接收和角度解算功能;具有异步串行总线数据和CAN总线数据的FIFO协议通信功能,与通用接口控制电路之间完成总线数据交互;具有加电、周期、启动自检功能,与信号处理软件配合能够实现对信号处理单元工作电压、工作温度及其他模拟信号的监测上报功能。具有通过接收控制指令数据测试LVDS串口状态功能,上报LVDS串口状态(加电、启动自检功能)。具有上电读取FLASH、EEPROM器件信息功能,进行校验和测试,并能够上报接口控制电路状态(加电、启动自检功能);具有通过异步串行总线实现DSP软件远程加载功能;具有程序运行监测功能和硬件复位功能;提供软复位接口,用于功能软件实现软复位。

FPGA完成测角功能的数字滤波、信号抽取、幅度解调、相位解调、峰值检测、时间测量、信号鉴相等数字信号处理,执行数字信号处理器的底层控制软件,构建双口RAM、产生硬件逻辑控制和工作时钟分配等控制信号。FPGA系统时钟为100MHz;中频采样时钟为25MHz。时钟缓冲器GM8543扇出的50MHz时钟作为中频信号采样时钟,该时钟在FPGA内部经过PLL倍频为100MHz的时钟作为FPGA的系统工作时钟。本板的FPGA的加载方式为Continuous SelectMAP Data Loading,FPGA完成上电自我初始化后,INIT_B信号释放,FPGA采用模式管脚M[2:0],确认采用哪种模式进行程序加载,当FPGA采样M[2:0]=011时,CCLK输出时钟,配置数据从配置FLASH中读入FPGA,配置成功后,释放DONE,DONE信号变高表明程序加载成功。SMQ4VSX55FF1148采样70MHz中频信号并进行处理分析、通过模转换器产生1路用于通道AGC控制的模拟电压和1路用于自检的模拟电压、与通用接口控制电路通过1个CAN总线的FIFO接口和1个UART总线的FIFO接口进行数据通信、与DSP通过32位EMIF总线进行数据通信。

DSP根据巴克码功能定时和功能识别码启动功能置信度判决,进行往、返扫描波束脉冲时间间隔的测定和角度解算;进行着陆或着舰坐标变换,产生飞机相对着陆点或着舰点的方位、仰角和距离信息。FT-C6416和TMS320C6416TBGLZA8完全兼容,主频720MHz;综合运算性能5760MIPS;支持8/16/32/64 位数据,支持40 位长整数运算;8 个高度独立的功能部件,各功能单元独立执行,大大提高运算能力;2个EMIF 接口,含有1个64 位EMIFA和1个16 位EMIFB:支持多种外部存储器的无缝接口,包括SBSRAM、SDRAM、ZBT SRAM、FIFO 和异步存储器等;

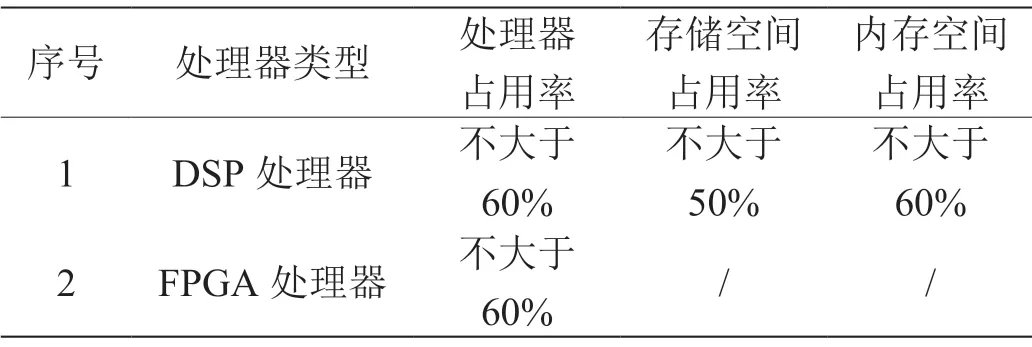

硬件资源占用率如表1所示。

表1:硬件资源占用率

2.3 时钟管理设计

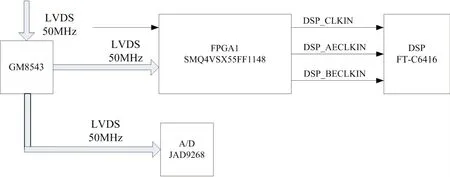

微波信号处理板卡上的FPGA、DSP、ADC、DAC都需要能够产生特定频率的时钟才能够正常工作。所以时钟的设计也是本板的重点之一。经过时钟缓冲器GM8543输出的两路50MHz差分时钟作为中频信号采样时钟,一路时钟在FPGA内部经过PLL倍频为100MHz的时钟作为FPGA的系统工作时钟,另一路供给JAD9268-100使用。DSP的时钟由FPGA内部供给,由于FT-C6416系统的工作时钟为500MHz,由此可设定CLKIN=25MHz,PLL倍频因子为20。时钟单元如图4所示。

图4:时钟单元

2.4 电源模块设计

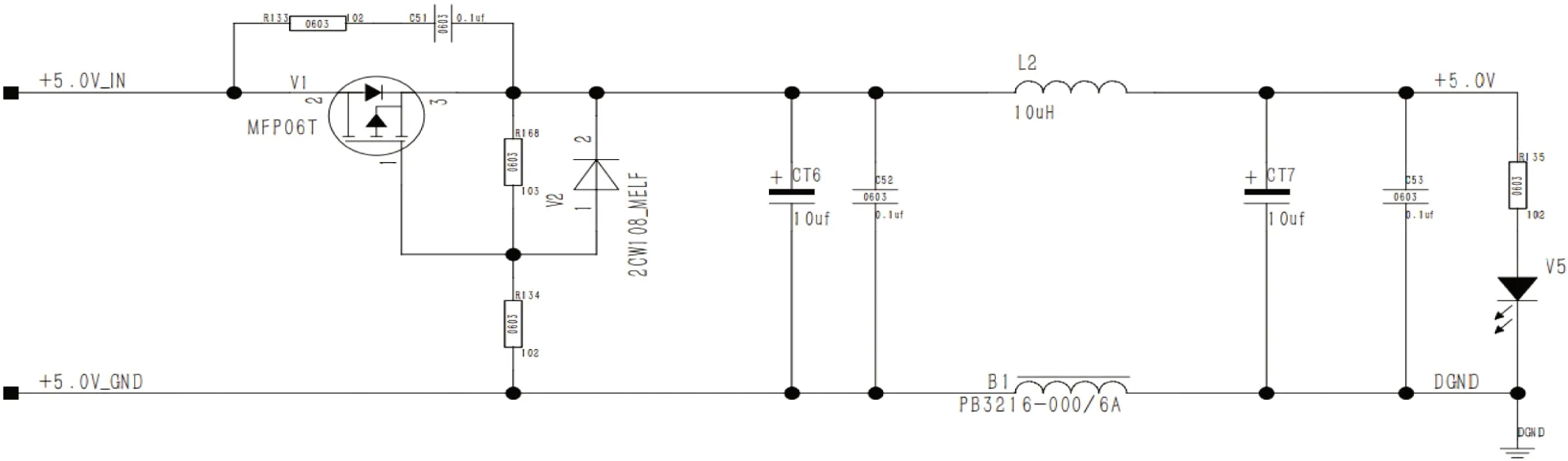

电源单元主要功能是将外部输入的5V电源转换为内部各个芯片的工作电源及电源的上电时序控制。电源单元的特性具有隔离:电源输入和输出地滤波隔离;

短路保护功能:具有输入短路保护功能(例如:输入端加保险丝),当用电设备输入端发生短路时,可以及时与供电电源断开,避免供电电源输出端短路保护引起使用此供电电源的其他用电设备无法正常供电;在供电输入端电压反极性条件下,信号处理单元可以不工作,但不影响信号处理单元以后的性能;瞬时掉电:输入电源出现≥100ms 掉电脉冲时(电源电压≤1V),用电设备在电源恢复正常后可以自动重启正常工作。电源滤波要求:为了有效减少电源线上的电磁干扰问题,电源输入端需加 EMI滤波措施。电源模块选用HCE4644MB来输出所需要的各种电平,通过对HCE4644MB的PGOOD以及RUN管脚的相互连接来实现FPGA的上电顺序,这里推荐上电顺序为VCCINT->VCCAUX->VCCO。以此推荐的上电顺序加电时,在加电过程中,IO引脚仍然保持在高阻态。每种电源的上电爬升时间应在0.2ms~50ms之间。FT-C6416的内核和I/O的上电没有确定的时序要求,如果一个电压低于正常的工作电压时,另一个的电压的上电时间不能大于1S,为了保证DSP正常初始化,上电期间RESET管脚必须保持低电平,直到PLL稳定。该电源模块共用到1V、A1.8V、1.8V、3.3V、A3.3V、D5V等6种电平,另外,输入电路也进行了防反接及滤波电路设计,如图5所示。

图5:电源示意图

2.5 ADC/DAC模块设计

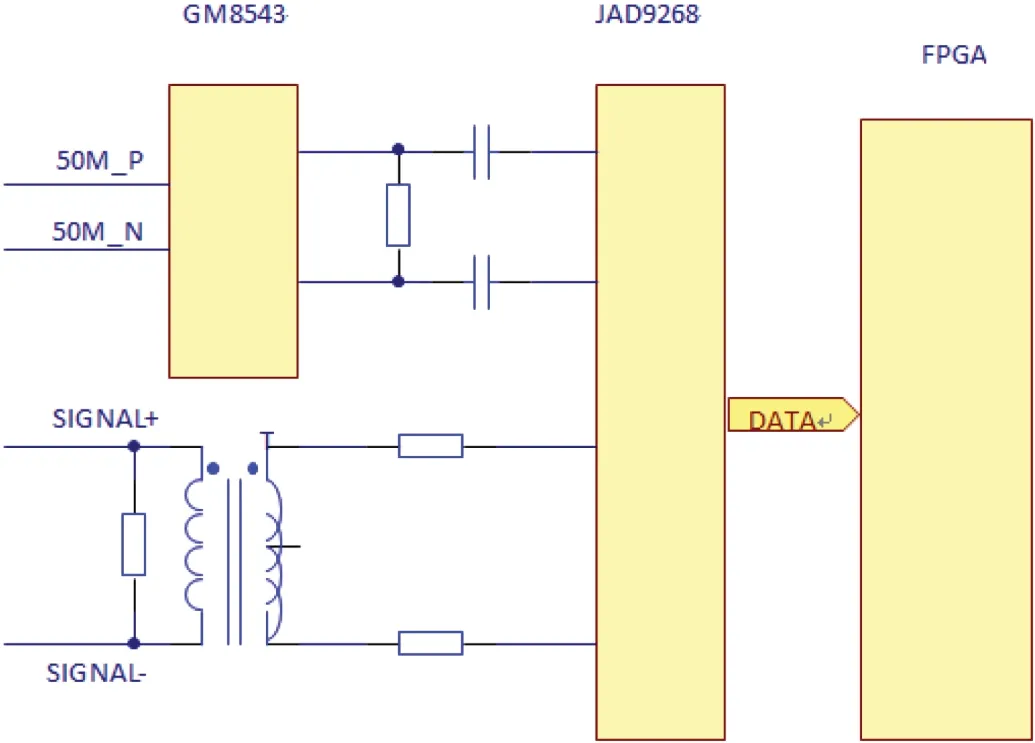

A/D转换电路主要用于完成70MHz中频信号A/D采样。D/A转换电路主要用于实现AGC模拟量的产生和自检调幅信号的产生,A/D转换器选用58所的16位模数转换器JAD9268-100,该器件输出有LVDS和COMS两种模式,本设计中采用LVDS模式。逻辑设计时将高12位作为有效数据替代原程序中的相应数据。ADC采样率为50MSPS,信号幅度为-5dBm~0dBm,图6为ADC单元原理框图。

图6:ADC单元原理框图

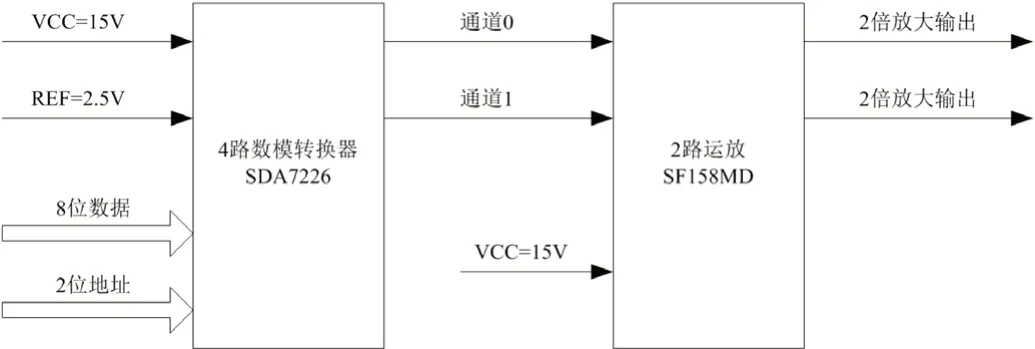

DAC单元采用24所的4路模数转换器SDA7226,该芯片经地址选通输出2路模拟信号,经运放SF158MD放大2倍输出,DAC单元原理框图如图7所示:

图7:DAC单元原理框图

3 结束语

该信号处理板以DSP和FPGA为核心器件,主要用来完成70MHz中频信号的采样、数字信号处理解调解算、总线端口通信与控制、状态监测和增益控制等。用国产化器件代替了进口器件,增强了自主性。经实测后,各项功能正常,能够满足预定的技术目标,功能完备。