基于Multisim的数字钟电路设计

2022-09-09孙孟雯陈影张淼范毅军胡云朋

孙孟雯 陈影 张淼 范毅军 胡云朋

(陆军军事交通学院 天津市 300130)

电子计数器是一种计算输入脉冲的时序逻辑网络,被计数的输入信号就是时序网络的时钟脉冲,除计数功能外,其还可以完成其它特定的逻辑功能,如测量、定时控制、数字运算等等,在很多电子设备中都有广泛应用,如转速测量显示电路,数字电子钟等。

随着数字化的信息技术大潮,电子技术获得了飞速发展。在计算机技术的推动下,电子系统设计所采用的技术越来越先进,同时也使电工电子技术进一步得到提高。这其中,融合了计算数学,优化理论等多学科精髓发展起来的电子设计自动化即EDA 技术,是现代电子设计技术不可或缺的部分。依托强大的电子计算机性能,通过虚拟的电工元器件,虚拟电子与电工仪器和仪表,实现了电路的编译,化简,优化和仿真等工作,简化了设计流程,提高了效率。

在众多EDA 软件中,Multisim 以其丰富的元器件库,迅捷的仿真,分析等功能,获得了广泛使用。在传统的学习环境中,受限于场地和设备等因素,很多实验无法进行,利用仿真软件和第三方元器件库,则可以极大地降低学习成本和实验难度,使电路设计和验证顺利展开。

本文基于集成计数器设计数字钟电路,针对不同电路要求,提出了不同设计方案,进行了讨论,利用Multisim 仿真软件,通过调整电路参数观察电路仿真结果,验证电路原理,同时也直观的了解不同设计方案的现象和影响。

1 集成计数器功能介绍

本文讨论“时-分-秒数字钟电路”的设计和仿真,电路由时个位和时十位计数器,分个位和分十位计数器,秒个位和秒十位计数器构成。其中“时”计数器为24 进制,“分”和“秒”计数器均为60 进制。电路采用74LS161 集成计数器来实现计数单元的功能。

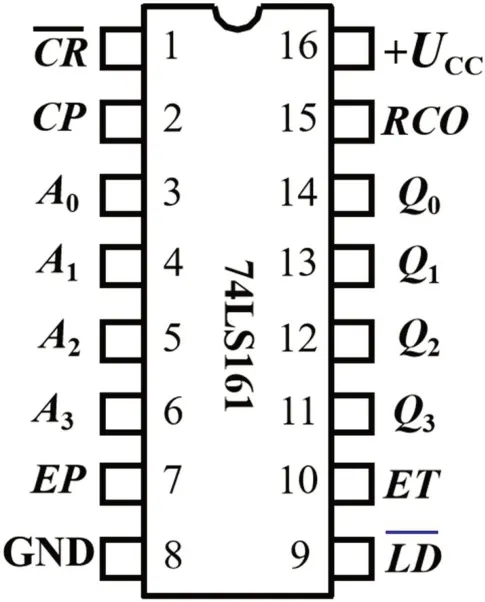

74LS161 芯片是具有异步清0、置数、计数和保持等功能的4 位同步二进制加法计数器,常见封装方式为双排插件式。图1 标示出了其引脚排列。

图1 :74LS161 引脚图

由表1 可知74LS161 有如下功能:

表1 :74LS161 功能表

2 计数器实现途径

分(秒)计数器为六十进制,其实现的计数循环是00 →01 →…→59 →00,即当数字钟计数到23 时59 分59秒时,在下一个CP 脉冲来临时,数字钟置零重新计时。时计数器为二十四进制计数,其计数规律是00 →01 →…→23 →00。74LS161 芯片可以使用“异步清零法”和“同步置数法”两种方法实现上述循环。

2.1 清零方式

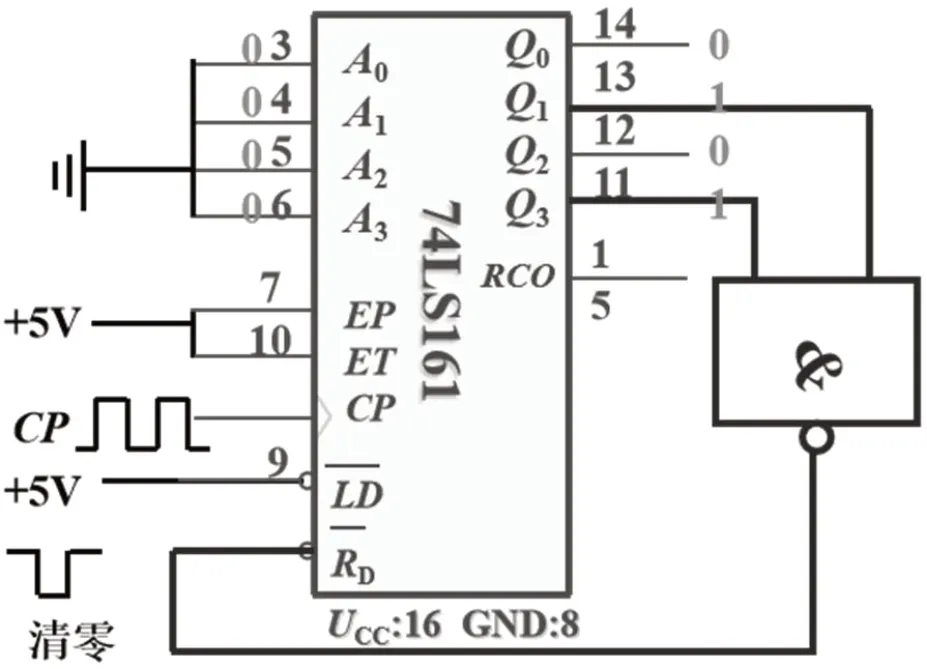

2.1.1 异步清零法

图2 :异步清零法电路原理图

图3 :异步清零法状态图

2.1.2 同步置数法

图4 :同步置数法电路原理图

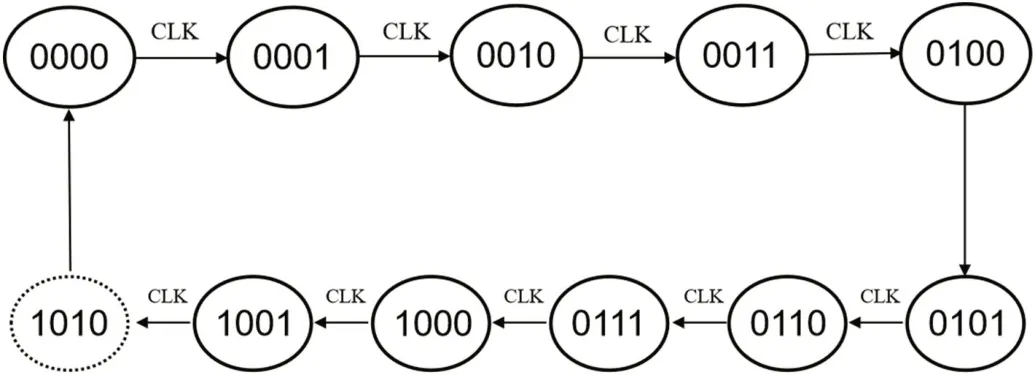

图5 :同步置数法状态图

2.2 级联方式

无论是时还是分秒计数器,可以按照一定方式,把多个计数器连接起来,从而增加计数的范围,将小进制计数器级联为大进制计数器。采用两片74LS161 级联实现个位和十位的计数,其个位和十位均接成十进制计数器,再通过前述清零法或者置数法跳过多余的状态,形成24/60 进制计数器。这种设计方法比较简洁,连线较少,且在实际操作时具有更多的灵活性与多样性。

2.2.1 串行级联

串行级联,即“个位”计数器连接外部CP脉冲信号;而“十位”计数器不连接外部CP 脉冲,而是将“个位”计数器的某些信号,作为自己的CP 脉冲。

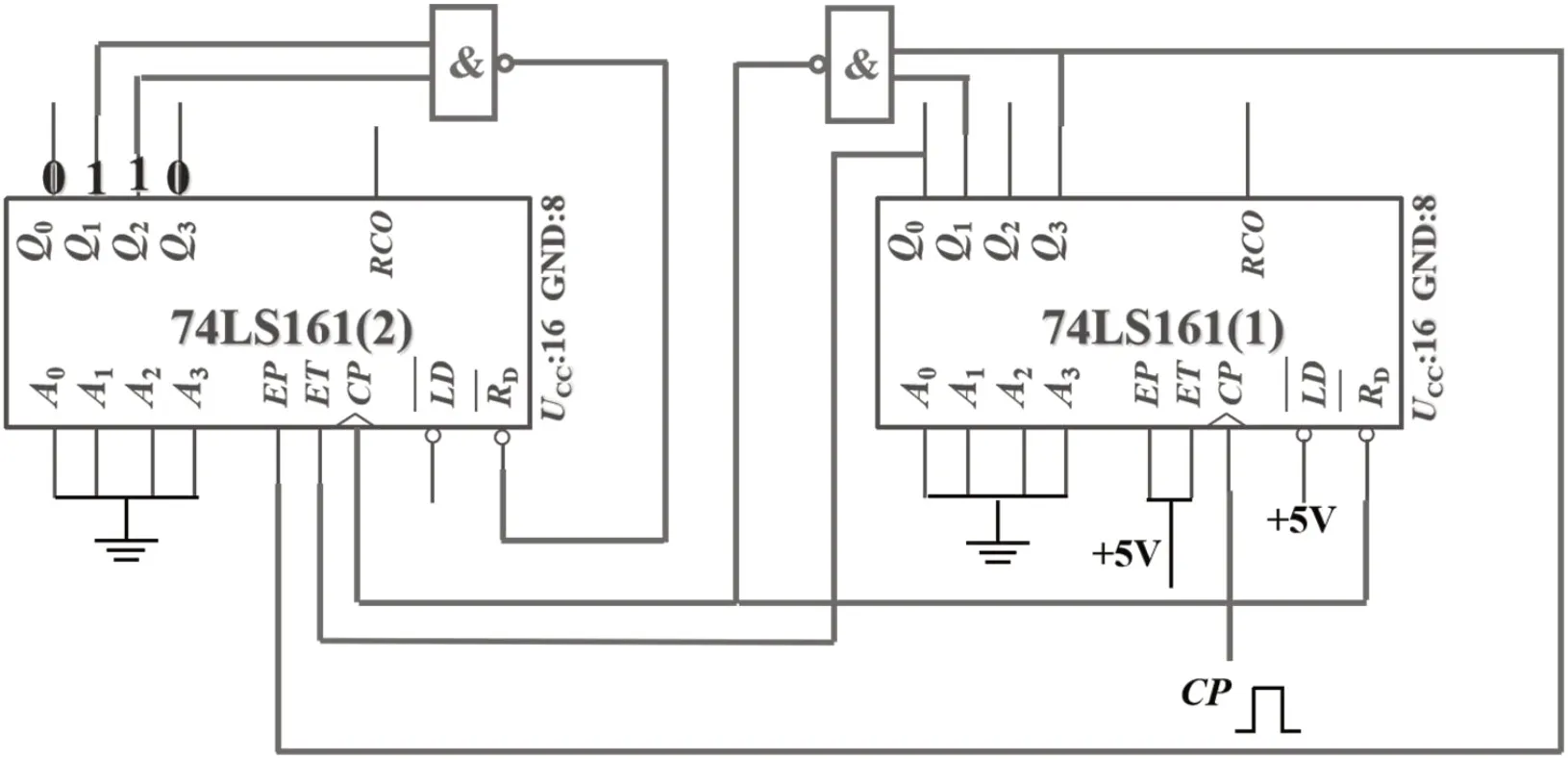

以60 进制计数器为例,低位计数器的进位信号经非门译码后作为高位计数器的时钟脉冲信号。个位每十次计数后重新计数,且十位计数器需计数一次,十位的脉冲信号需要由个位计数器提供。将低位计数器的Q和Q经过一个二输入的与非门,送入“十位”计数器的CP 端。当个位计数器的输出QQQQ=1001 时,十位计数器CP 端为低电平,下一个状态,个位计数器的输出QQQQ=1010,十位计数器CP 端为高电平,CP 端由低电平变为高电平,出现了上升沿信号,十位计数器进入计数状态(十位计数器的CT,CT始终连接高电平),计数一次。60进制电路原理图如图6所示。

图6 :60 进制电路原理图

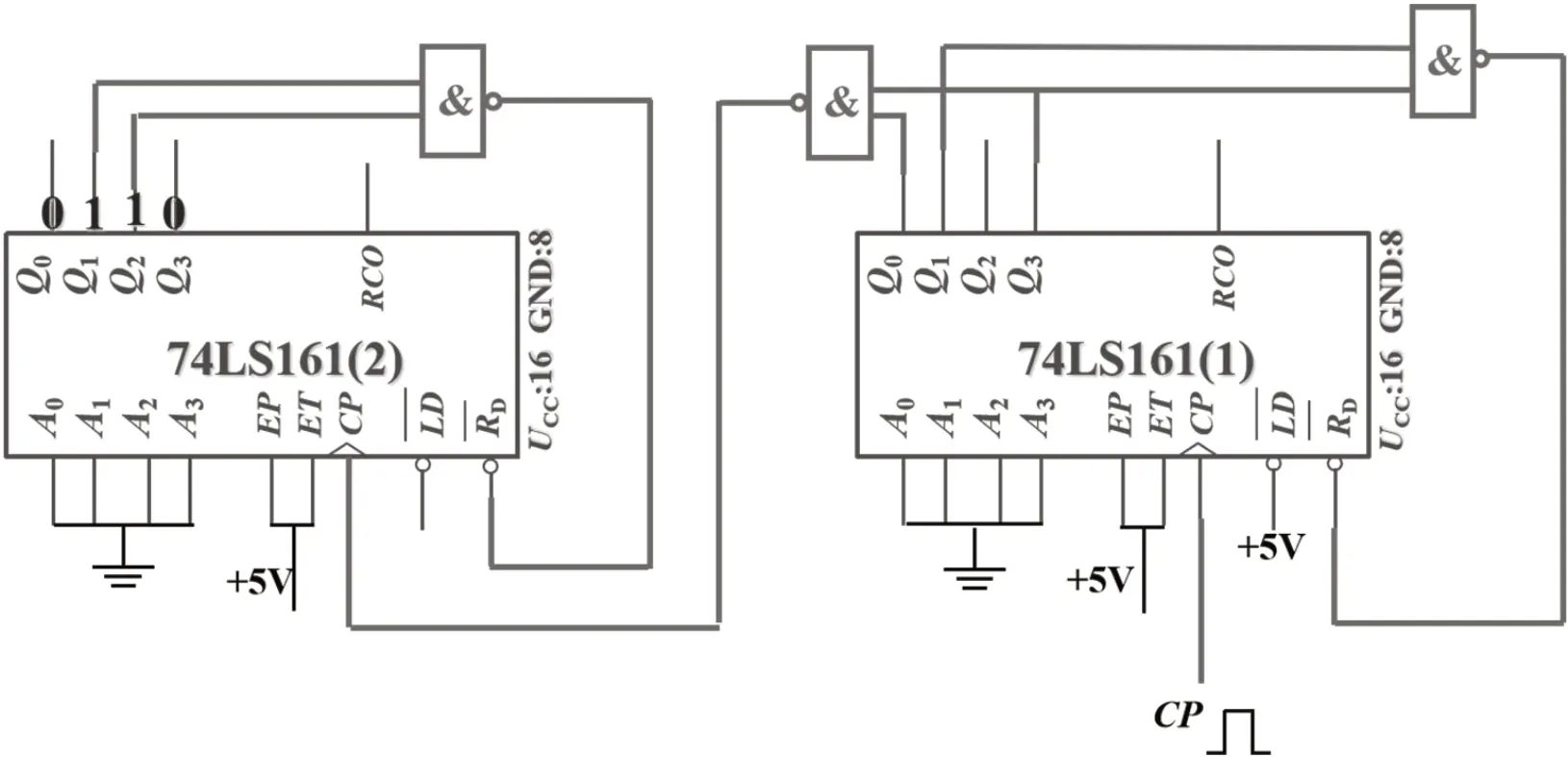

2.2.2 并行级联

并行级联,即外部时钟信号,同时连接“个位”计数器CP 端和“十位”计数器的CP 端。以24 进制计数器为例,每次CP 脉冲来临,个位计数器计数一次,如果依然如上述串行级联接法,十位计数器的CT,CT始终连接高电平,那么十位也将在每次CP 脉冲信号来临时计数一次,不符合功能要求。为了避免此问题,十位的CT,CT连接个位计数器的Q和Q端,当个位计数器的Q和Q端同时为1,即个位到达QQQQ=1001 状态时,CT=CT=1,十位计数器计数一次。24 进制电路原理图如图7 所示。

图7 :24 进制电路原理图

3 电路仿真

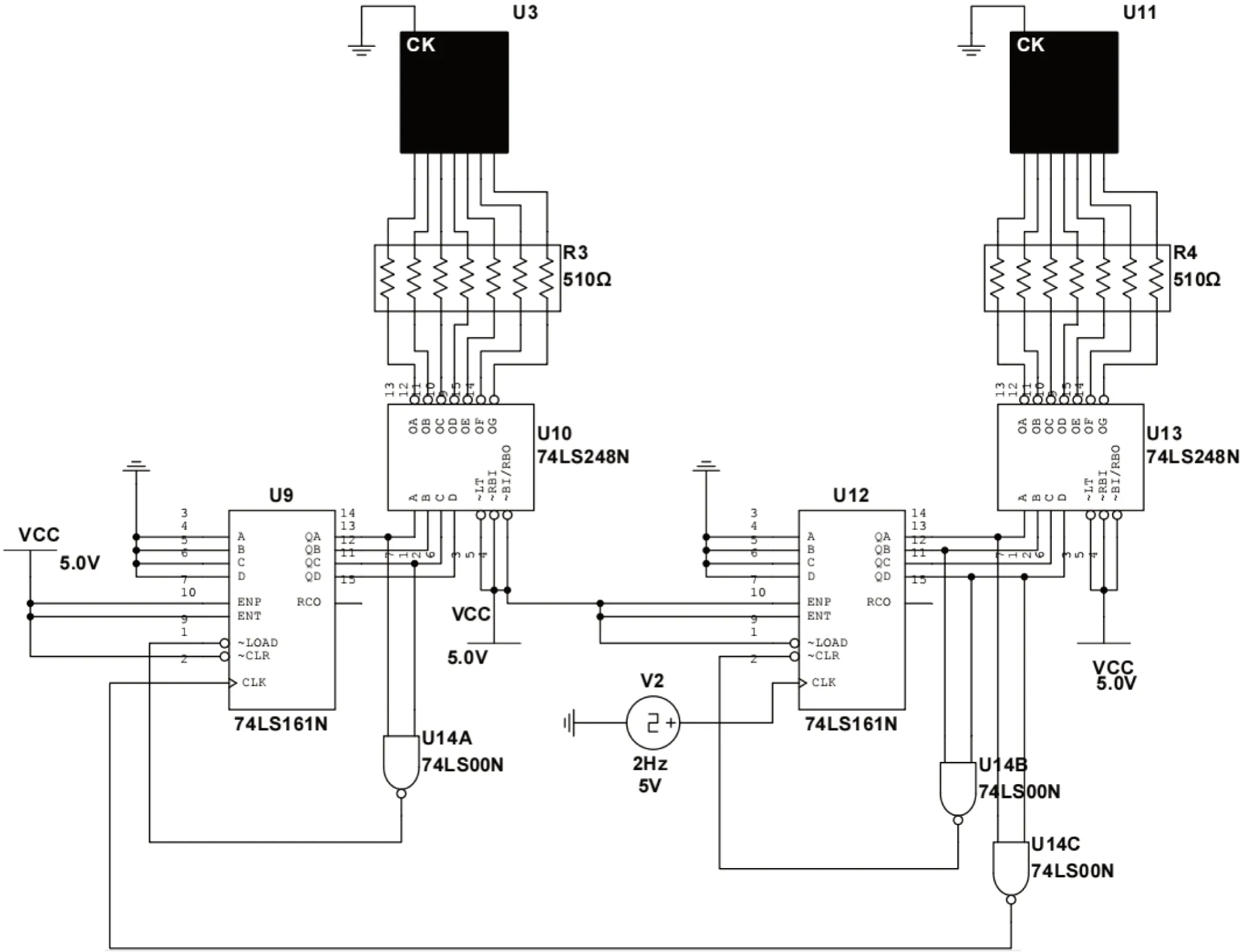

前文介绍了计数器的循环方法,以及各计数器间的级联方式。为了验证电路设计方案的可行性,使用EDA 软件Multisim 进行仿真,配合使用74LS248 芯片,一种有着内部上拉电阻、带BCD 输入的4 线七段显示译码器,线路结构型式为54/74LS248,其输出为高电平有效,因此对应的半导体数码管应为共阴极。将74LS161 的输出端分别与译码显示器的输入端相连,之后连接数码管显示计数结果。

按照模块化设计思想,分别连接“时”、“分”和“秒”计数器模块。如图8 所示,六十进制“分”/“秒”计数器,其中高位计数器使用QQQQ=0101 进行置数循环,个位计数器使用QQQQ=1010 进行清零循环,两个计数器使用串行的方式进行级联,高位进行置数操作时,需要低位计数器的Q和Q端进行“与非”运算,其结果作为高位的CP 脉冲信号。这样,当低位计数器QQQQ=1001 且高位计数器QQQQ=0101 时,等待外部下一个CP 脉冲来临,低位计数器QQQQ=1010,高位计数器CP 脉冲有效,进行置数为0000 操作。

图8 :六十进制计数器

图9 :二十四进制计数器

4 总结

使用集成计数器进行任意进制计数器设计时,需要注意清零,置数和级联方案的选取。使用Multisim 仿真软件,可以直观地观察电路运行结果,通过不断的测试和调整,可以验证方案的正确性,便于及时发现,修改错误,简化实验步骤和难度。在实际电路的设计中,也要注意芯片的选择。不同的芯片参数会导致不同的结果。因此,在使用集成计数器设计任意二进制计数器时,需要结合电路要求,根据电路的实际应用选择器件类型,采用合适的连接方式。