一款相控阵雷达时序控制器的设计与实现

2022-09-02魏汇赞吕宇宙王铭伟

魏汇赞,吕宇宙,王铭伟,郭 畅

(1.上海航天电子技术研究所,上海 201109;2.北京华清瑞达科技有限公司,北京 100080)

传统的机械扫描雷达主要依靠转动雷达天线实现波束的扫描,从而完成对目标的搜索与跟踪。随着战场环境的日益复杂,当面对高速、多批次、不同俯仰角目标时,机械扫描雷达显得有些力不从心[1]。不同于传统的机械扫描雷达,相控阵雷达以电子方式控制波束,从而改变波束指向。因此,相较于机械扫描雷达,其具有波束指向灵活、可靠性高、抗干扰能力强等优点,并成为目前的主流体制雷达[2]。

相控阵雷达能够根据战场环境以及人工干预命令,完成对雷达时间、能量、波束、波形、频率等资源的分配,排布调度波位,产生相应的时序控制信号,对重点目标与区域分配更多的时间与能量,实现对重点目标的快速发现与稳定跟踪[3-6]。其中,不同调度波位中所带有参数(信号处理方式、发射脉冲数、捷变频控制、发射脉冲宽度、发射脉冲重复间隔等)不尽相同,这对时序控制器提出了极高的要求。该文基于此,设计了一款高性能的时序控制器。

1 时序控制器的硬件设计

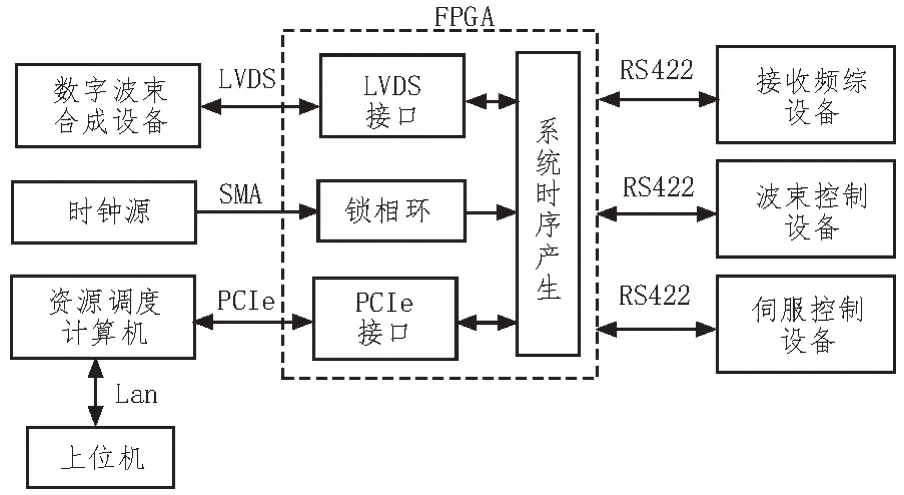

时序控制器作为雷达正常工作的节拍器,需要协调雷达各个分系统进行稳定有序的工作。因此,其需要具备以下性能要求:1)多个高速传输接口;2)高质量的时钟源;3)较强的信号处理能力。基于以上性能要求以及某型雷达研制需求,设计了如图1 所示的硬件结构图。

图1 时序控制器的硬件结构图

该时序控制器主要由一片高性能的现场可编程门阵列FPGA(Filed-Programmable Gate Array)芯片、一片高性能的中央处理器CPU(Central Processing Unit)以及多种外围接口硬件电路所构成。其中,FPGA 芯片采用了Xilinx 公司的Xcku040-ffva1156-1-i,该芯片拥有28 个高速收发器端口(最高速率支持12.5 Gb/s),726 000 个逻辑单元、2 760 个信号处理单元以及520 个输入/输出引脚。因此,该芯片满足了时序控制器中各项性能需求,因此将其用于系统时序信号的产生以及各路数据的通信交互。CPU采用英特尔公司的I7-3517UE,该芯片的主频可工作在1 333 MHz。该CPU可用于相控阵雷达中的资源调度,负责计算雷达的时间、能量、波束等以及向各个分系统分发调度命令,同时接收与转发上位机下发的人工干预命令以及上传各个分系统的Bit状态。其余的接口硬件电路主要包含高速串行计算机扩展总线标准PCIe(Peripheral Component Interface Express)接口[7]、低压差分信号LVDS(Low Voltage Differential Signaling)接口[11]、RS422 接口[12]。其中,PCIe 接口用于FPGA 与CPU 之间的通信,采用PCIe 3.0 标准,通道数为4,最高速率支持5 Gb/s。LVDS 与RS422 是两种不同的电平标准并分别适用于不同的场景,其中LVDS 适用于单板内或者板与板之间的信号传输;RS422 电平幅度稍微大于LVDS,抗干扰能力也比LVDS 强一些,适用于远距离的信号传输。由于雷达分系统众多,为了保证通用性,采用了两种对外接口电平标准。

2 时序控制器的功能设计

2.1 时序控制器的功能结构

根据具体的任务需求,设计了如图2 所示的功能结构图。其主要由LVDS 接口模块、系统时序产生模块、PCIe 接口模块等组成。其中,锁相环模块用于外接高质量时钟源,根据时序信号的具体要求锁频至相应的时钟频率,并将该时钟信号作为主时钟;PCIe 接口模块用于接收资源调度计算机下发的调度报文与人工干预报文;系统时序产生模块根据资源调度计算机下发的报文产生相应的时序信号,并通过LVDS 接口与RS422 接口发送至各个分系统(数字波束合成设备、接收频综设备、波束控制设备、伺服控制设备等)。

图2 时序控制器的功能结构图

2.2 系统时序产生模块的设计

系统时序产生模块是整个时序控制器的核心。考虑到控制参数的多样性以及模块的通用性,在设计中采用了参数化、模块化的设计思路,时序信号的产生以及控制参数全部支持动态重配置。

当系统时序产生模块接收到资源调度计算机发送的报文时,按照约定的报文协议进行解析以获得相关控制参数(工作模式、波位码、信号处理方式、码型及脉宽、发射脉冲个数、发射脉冲重复间隔等)。值得注意的是,为了避免报文传输出现错误从而导致系统时序出现紊乱的问题,在只读存储器ROM(Read-Only Memory)中存放了各种工作模式下的默认报文,以便于当报文传输出现错误时使用。其中,报文的准确性可以根据包头、包尾以及校验码进行判断。图3给出了雷达工作的基本时序图。其中,τ表示发射脉冲宽度,并且各个时序信号都是低电平有效。

图3 雷达工作基本时序图

2.3 LVDS接口模块的设计

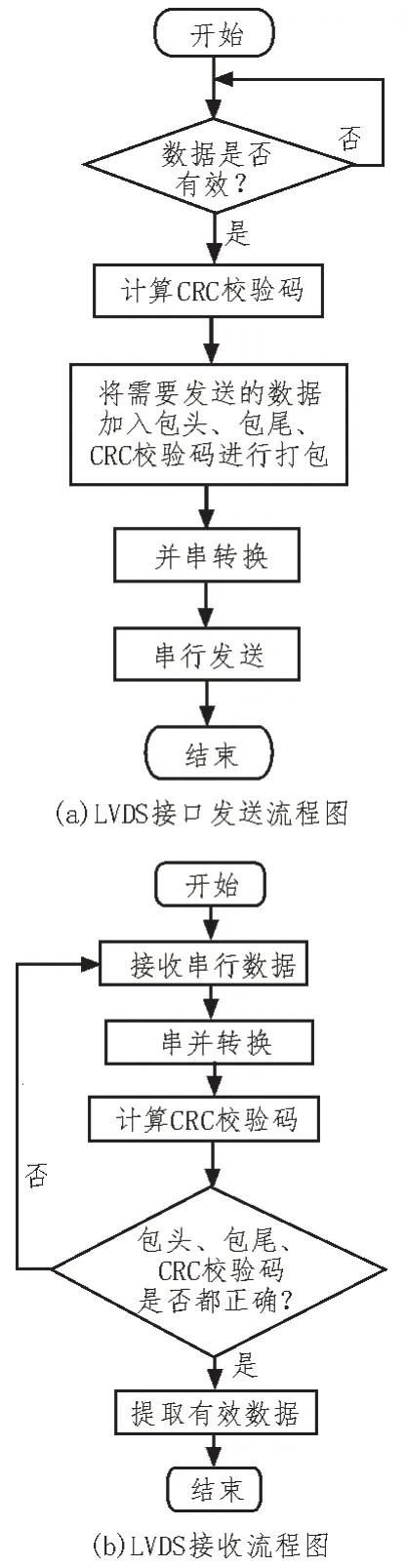

LVDS 接口模块用于发送与接收时序控制信号。在该设计中,由于硬件设计原因,只分配了两对LVDS差分线用于与数字波束合成设备进行时序传输。但实际上,数字波束合成设备正常工作所需的时序信号数量大大超出了2 个。因此,只能将多个时序信号经过并串转换进行传输。值得注意的是,这种传输机制需满足时序信号的变换率远远小于LVDS 传输速率。例如,时序信号每0.125 μs进行一次高低电平变换,LVDS传输速率为2.7×105bit/s,那么LVDS 一次传输的极限是30 个数据,否则将造成时序信号传输的遗漏。同时为了保证数据传输的准确性与可靠性,还需加上包头、包尾以及校验码,并且只有当发送端与接收端的包头、包尾、校验码保持一致时才能判定数据有效。因此,在保证传输可靠性的同时,所能传输的时序数量也将大大减少,但还是能保证将数字波束合成设备需要的时序信号全部进行传输。

图4给出了LVDS接口发送与接收时序信号的工作流程图。在发送端,首先对需要发送时序信号的有效性进行判断,如果数据有效,根据需要发送的数据计算得到相应的CRC(Cyclic Redundancy Check)校验码[8]。其中,相较于传统的奇偶校验码PCC(Parity Check Code)只能校验一位错误,循环冗余校验码的检错能力更强,可以检测出多位错误,因此,在该设计中采用CRC 进行校验。包头与包尾的数据可以根据具体的设计要求进行定义。例如,LVDS 发送端发送一包28 位的数据,这一数据由4 位包头数据+10位时序信号+10 位CRC 校验码+4 位包尾数据所构成。LVDS接收端,需要将串行数据转换成并行数据,当检测到包头、包尾时,进行数据提取,并进行CRC 校验。

图4 LVDS接口收发流程图

当计算得到的CRC 校验码与接收得到的CRC校验码一致,则表明该包数据有效,否则丢掉。由此,完成了整个LVDS 接口的发送与接收。

2.4 PCIe接口模块的设计

PCIe 接口模块用于实现计算机与FPGA 之间的通信。在具体的软件实现上,直接调用了Xilinx 公司提供的相应IP 核[9-10]。同时为了便于后续的使用,在IP 核外围添加了面向用户的端口。图5 给出了PCIe 接口模块功能结构图。其主要由用户端、直接内存操作DMA(Direct Memory Access)状态机以及PCIe IP 核所组成。

图5 PCIe接口模块功能结构图

其中,用户端口主要包含寄存器端口、中断端口以及随机存储器端口。寄存器端口分为128 个读寄存器与128 个写寄存器,读寄存器供用户向计算机发送数据,用户负责输入数据,计算机负责读取;写寄存器供计算机向用户发送数据。中断端口主要包含中断信号与32 位中断寄存器。用户若想发送中断信号,只需将中断使能一个时钟周期即可,同时对中断寄存器赋值,用户通过中断寄存器的值判断其类型。随机存储器端口主要包含两个32 kB 深度、32 bit 位宽的标准Block RAM 的读写端口,通过计算机来切换读写两个RAM。

DMA 控制器用于控制整个数据链路的发送与接收。当上电复位后,DMA控制器首先读取计算机下发的内存首地址以及计算机下发的开辟内存空间大小。当计算机需要向用户端发送数据时,PCIe IP首先接收相应的数据,并通过AXI总线通知DMA控制器进行读内存操作,DMA 控制器读取相应的数据,并根据数据类型将数据写入RAM 或REG中。当用户端需要向计算机发送数据时,用户将数据放入RAM 或REG中,然后再发送中断信号通知计算机进行数据的读取,计算机收到中断信号后下发写内存指令,DMA控制器读取用户数据,并将数据通过AXI总线写入到计算机内存中。

3 时序控制器的功能测试

将编译后的程序在线加载至FPGA 中,通过ILA核对相关数据进行抓取。其中,控制命令参数如下:信号处理方式为动目标检测MTD(Moving Target Detection),发射脉冲数为18,发射脉冲宽度为50 μs,发射脉冲重复周期为330 μs。经过数据抓取发现,实际的时序信号TRP、TRP1、TRP2、TRP3 之间的时间间隔与图3 基本保持一致,并且各个发射参考脉冲与下一个发射参考脉冲之间的时间间隔与控制命令参数保持一致。因此,该时序控制器能根据命令参数正确地产生相应的时序信号。

4 结论

该文完成了一款高性能的相控阵雷达时序控制器的设计与实现。该时序控制器采用了PCIe 接口外加FPGA 的实现机制使得时序信号的产生具备参数化、可编程化的优点,并满足了相控阵雷达对不同俯仰以及不同方位的相扫需求。另外,该时序控制器还具备多个对外高速稳定的传输接口,满足了相控阵雷达中多个分系统对接口的需求。该时序控制器已经应用于某型预研雷达中,取得了良好的验证效果。