传统芯片进入瓶颈,堆叠式芯片唱主角?

2022-08-26桫椤

桫椤

在计算机发展的历史上,计算机性能的提升主要依托于其搭载的处理器的进步,主流方式是提升芯片(Microchip)的先进制程来提升其性能,使芯片制程从14nm到5nm不断缩小,同样大小的芯片中装入更多晶体管来提升其运算能力。

但芯片的制程不可能无限缩小,未来有更多的堆叠芯片产品将会出现。工程师实现这一目标的一种方法是将微芯片堆叠在一起,用简单的比喻就是,计算机内部通常扁平的硅片正在变成多层,用于内存、电源管理和图形等功能的电路将堆叠在一起,作为提升性能和节约成本的一种方式。

推动堆叠芯片设计这一趋势的原因很简单且现实:现在的设计能力面临巨大的压力,芯片行业通过缩小晶体管以维持更高性能来跟上步伐的能力遇到了技术障碍,要继续让芯片更快、更小,付出的努力可不像前20年这么简单。

芯片的发展长期以来只是延续摩尔定律的趋势——英特尔创始人戈登·摩尔观察到,集成电路上可以容纳的晶体管数目在大约每经过18个月便会增加一倍。摩尔定律只是是内行人摩尔的经验之谈,汉译名为“定律”,但并非自然科学定律,它一定程度揭示了信息技术进步的速度,这条经验法之前已经宣布结束,因为芯片确实越来越先进,但开发周期却越来越长。

荷兰公司ASML就认为,即使要保持摩尔定律的发展,仅仅使芯片上的功能更小是不够的。 作为ASML来说,基本上垄断了世界上最先进的芯片和最小晶体管至关重要的光刻机,它的发言具有一定的前瞻性。在2021年9月向投资者的介绍中,ASML就谈到了“芯片堆叠系统扩展”的想法,该公司认为“系统扩展”是对ASML 为缩小微芯片特性所做工作的补充。

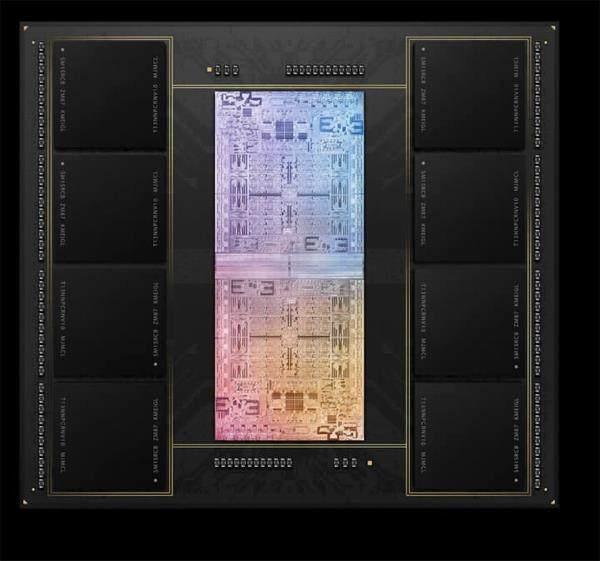

率先“吃螃蟹”的当数苹果公司2022苹果春季新品发布会上发布的M1 Ultra处理器,这款处理器采用了苹果UltraFusion封装架构,通过两颗M1 Max晶粒的内部互连,性能与实力都达到空前水平。这种SoC芯片结构的出现,让超级计算机的算力提升,并且普及到了家用电脑中。

不过“堆叠芯片”也并非没有技术难度,当涉及管理在密集电路中执行的计算时,热量散发会给工程师带来挑战。尽管它们可以更节能,但它们的庞大尺寸意味着也会消耗大量电力。例如英特尔的Ponte Vecchio芯片采用了OAM模块,这是一种开放式硬件计算加速器形态和互连结构,共有五层,从下到上分别是底板、PCB 电路板、顶板、水冷装置和固定盖板。而新的 OAM 计算模块则需要 600W 的供电,几乎相当于一个吹风机的功耗,英特尔选择为这种架构液冷散热,但是与传统的大型散热系统相比,新开发的系统占地面积很小。

制造堆叠芯片并非易事,部分原因是这样做意味着以纳米级精度将每个芯片组件焊接到位,并且在没有微型焊枪的情况下将它们连接起来困难重重。

Apple 的 M1 Ultra 芯片在其 Mac Studio 计算机中使用,由 1140 亿个晶体管组成

在传统设备中,接收和传输无线电波(例如,通过 Wi-Fi 进行通信)的芯片可能会连接到另一个进行通用计算的芯片,它们之间的连接实际上就是所谓的“总线”。新的堆叠芯片封装反而将这两个芯片,可能还有更多直接连接起来,实现创新。

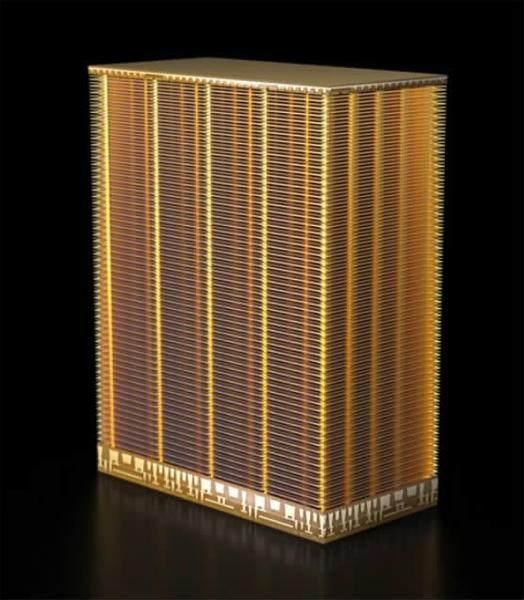

存储芯片大厂美光(Micron)7月底就宣布,其232层NAND闪存芯片已实现量产,这是全球首款突破200层大关的固态存储芯片,抛开工程样品不计,它的竞争对手目前只能提供176层的技术。

与竞争对手的芯片相比,美光技术将每单位面积存储的比特密度增加了一倍,每平方毫米封装14.6 Gbit。这一密度相比自家的176L NAND提升了约43%,比竞争对手的TLC产品高35%到100%。可以说,NAND Flash层数竞争愈演愈烈,继176层NAND之后,各大厂都瞄准200层以上NAND技术,美光之后,三星、铠侠等也在蓄势待发。

International Business前封装开发总监Subramanian Iyer表示,传统的微芯片必须将其近三分之一的面积(以及同样多的功耗)用于将芯片计算结果传达给设备其余部分的电路。而堆叠芯片使它们之间的通信更快,因为它允许它们之间的更多连接,就像在摩天大楼的楼层之间乘电梯旅行比一直穿过建筑物到达最近的一栋建筑更快一样。

美光的232 层闪存芯片是微芯片扩展的典型案例

虽然目前堆叠式芯片的数量可能很少,而且大多出现在标杆或者强大的主机中,但制造它们的趋势正在加速。

今年3月名为 Universal Chiplet Interconnect Express (UCIe) 的行业联盟宣布,英特尔与AMD已经加入其组织,一同与ARM、台积电、三星等推动标准与技术。越来越多科技大厂对芯片堆叠技术有浓厚兴趣,陆续加入自研芯片以发展业务,有谷歌、亚马逊、微软、特斯拉等,未来可期待从云端服务器到智能手机、游戏主机与智能汽车等都能看到这类堆栈架构为主的处理器。Ansys Samsung产品营销总监Marc Swinnen表示,近年来Ansys 客户涉及堆叠芯片的项目数量增加了20倍。

英特尔高级研究员Das Sharma 认为,堆叠型的芯片让英特尔可以提高其下一代台式机和服务器芯片的性能,并且不会增加现有芯片架构的占用空间或总功耗。这可能看起来有悖常理,但从芯片使用的功率来讲,这确是设计时需要考虑的,为芯片节省功率是行业的最高优先事项之一,否则一切创新都是空谈。

当然,芯片堆叠也不是没有弱点,实际上这是一种体积换性能的做法,想要通过14nm实现5nm的性能可能需要6块14nm芯片进行堆叠才能实现,从成本上来说这种做法同样有些得不偿失。同时芯片堆叠还会造成功耗以及散热等方面的问题,因为芯片堆叠不仅仅是简单地将两块芯片堆叠在一起,而是需要更多的技术和工序的支持。

并且芯片堆叠技术对于我国企業而言,是一道突破芯片封锁的曙光。从当下华为公布的堆叠芯片新专利上看,主芯片堆叠单元具有位于第一表面上的绝缘且间隔设置的多个主管脚,多个副芯片堆叠单元具有绝缘且间隔设置的多个微凸点,和苹果推出的M1 Ultra芯片将两颗M1 Max拼接起来不同,华为可将两个以上的芯片堆叠起来。在国内已经能够量产14nm、N+1等制程芯片的情况下,通过自主研发的专利降低功耗以及成本,不失为一种“曲线救国”的好方案。未来华为可能会采用多核架构的芯片,用堆叠、面积换性能,用不着先进工艺就能让产品具有市场竞争力,务实的心声还是值得支持的。

加州大学洛杉矶分校的伊耶博士说,推动人们对堆叠芯片产生兴趣的是人工智能和机器学习系统对现有硬件的贪婪需求。尽管面临挑战,但将当今的微芯片分解,重新组装成更大、更强的计算机,在动荡的半导体发展中或许代表芯片发展的另一种趋势。

华为芯片堆叠封装专利