异质衬底外延碲镉汞薄膜位错抑制技术进展

2022-08-23李艳辉杨春章李俊斌孔金丞姬荣斌

杨 晋,李艳辉,杨春章,覃 钢,李俊斌,雷 文,孔金丞,赵 俊,姬荣斌

〈材料与器件〉

异质衬底外延碲镉汞薄膜位错抑制技术进展

杨 晋,李艳辉,杨春章,覃 钢,李俊斌,雷 文,孔金丞,赵 俊,姬荣斌

(昆明物理研究所,云南 昆明 650223)

分子束外延碲镉汞技术是制备第三代红外焦平面探测器的重要手段,基于异质衬底的碲镉汞材料具有尺寸大、成本低、与常规半导体设备兼容等优点,是目前低成本高性能红外探测器发展中的研究重点。对异质衬底上碲镉汞薄膜位错密度随厚度的变化规律进行了建模计算,结果显示~1/模型与实验结果吻合度好,异质衬底上原生碲镉汞薄膜受位错反应半径制约,其位错密度无法降低至5×106cm-2以下,难以满足长波、甚长波器件的应用需求。为了有效降低异质外延的碲镉汞材料位错密度,近年来出现了循环退火、位错阻挡和台面位错吸除等位错抑制技术,本文介绍了各技术的原理及进展,分析了后续发展趋势及重点。循环退火和位错阻挡技术突破难度大,发展潜力小,难以将碲镉汞位错密度控制在5×105cm-2以内。台面位错吸除技术目前已经显示出了巨大的发展潜力和价值,后续与芯片工艺融合后,有望大幅促进低成本长波、中长波、甚长波器件的发展。

碲镉汞;异质衬底;位错抑制;循环退火;位错阻挡;台面位错吸除

0 引言

碲镉汞(HgCdTe,MCT)在整个红外谱段带隙可调,具有高量子效率以及低暗电流等优点,是目前军事领域应用最广泛的红外探测材料[1-3]。相较于其他薄膜外延技术,分子束外延技术(molecular beam epitaxy,MBE)具备能带调控、原位监控、异质外延等诸多优点,可实现复杂结构材料的制备。通过Zn组分的调整,碲锌镉(CZT)衬底可做到与碲镉汞材料完全晶格匹配,在碲锌镉衬底上获得的碲镉汞材料晶体质量较高,其位错腐蚀坑密度(etch pit density,EPD)一般在1×104~1×105cm-2范围内。分子束外延碲镉汞通常选用(211)面碲锌镉,由于碲锌镉晶锭中孪晶主要分布在(111)面上,与(211)面存在19.3°偏角,因此制备(211)碲锌镉衬底对碲锌镉晶粒尺寸的要求要高于液相外延使用的(111)碲锌镉衬底。上述因素导致了(211)碲锌镉衬底成品率更低、衬底尺寸更小、价格更加昂贵,高温器件、中长双色器件等高端探测器中仅(211)碲锌镉衬底价格就能占到组件价格的20%到40%。相较于碲锌镉衬底,异质衬底(如Si、GaAs、Ge、GaSb等)具有尺寸大、成本低、与常规半导体设备兼容性好等优点,在异质衬底上外延碲镉汞材料是国内外主流红外机构在低成本高性能红外探测器方向发展的研究重点。但该技术的主要问题在于异质衬底与碲镉汞之间较大的晶格失配(Si:19.3%、GaAs:14.4%、Ge:14.3%、GaSb:6.1%)将在碲镉汞薄膜中引入高密度的贯穿位错(threading dislocation,TD)。贯穿位错作为材料中SRH复合中心和漏电通道,将降低材料少子寿命,增加器件的产生复合电流密度,降低器件量子效率及零偏电阻,最终导致器件性能的衰减[4]。这种衰减效应对于短波和中波碲镉汞器件来说影响并不明显[5],但会严重制约长波、中长波以及甚长波器件性能。目前异质衬底上原生碲镉汞薄膜位错密度一般在8×106~3×107cm-2范围内,为了满足长波及甚长波器件的应用需求,碲镉汞位错密度需要控制到5×105cm-2以下[6]。

本文对碲镉汞薄膜位错密度随薄膜厚度的变化规律进行了计算,分析了决定原生碲镉汞薄膜位错密度的主要因素,明确了引入位错抑制技术的必要性。基于此,总结了循环退火、位错阻挡和台面位错吸除3种位错抑制技术的原理及研究进展,讨论了3种技术后续的发展趋势及研究重点。

1 异质衬底外延碲镉汞位错密度随膜厚的演化规律

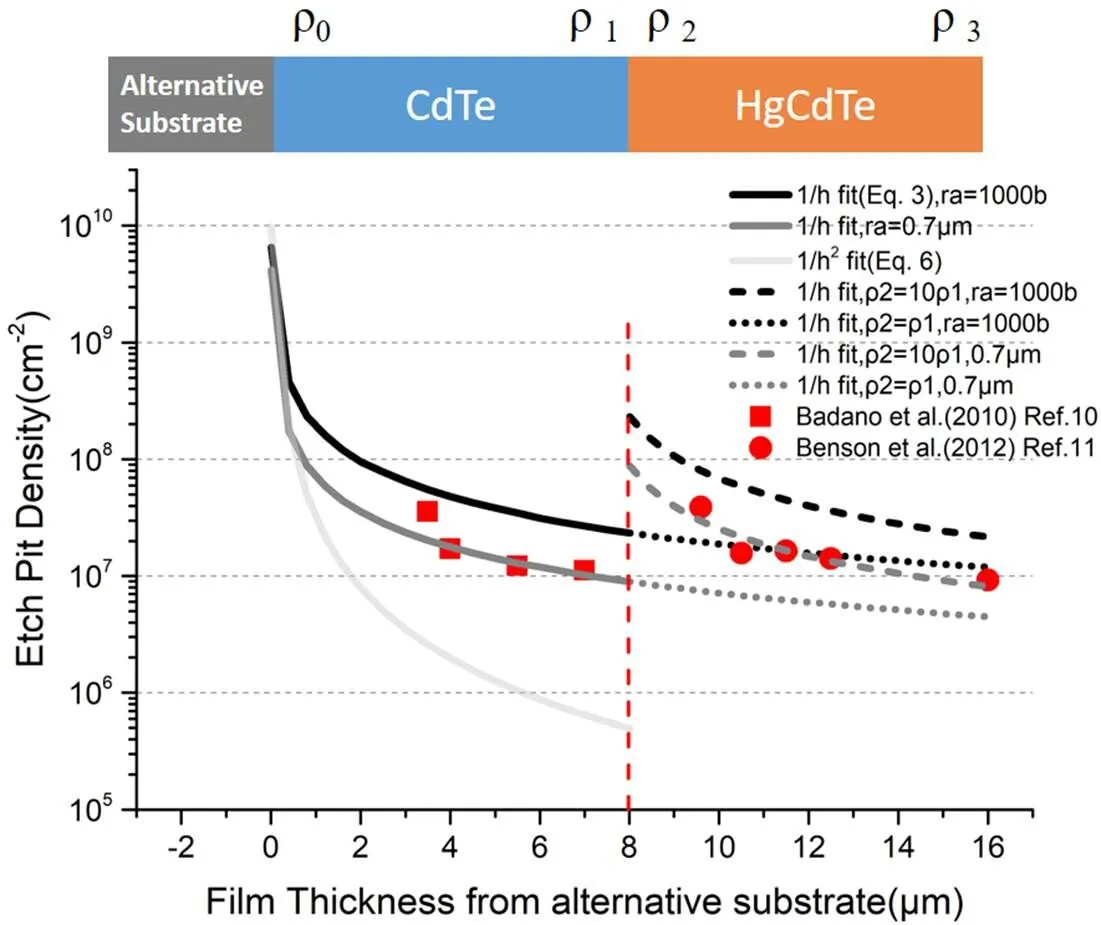

在异质外延体系中,~1/[7]和~1/2[8]是两种经典的位错密度随厚度演化模型。~1/模型认为位错随薄膜厚度增加而延伸,与延伸过程中相遇的位错发生湮灭反应(反应后两条位错均消失)。两条位错能够发生反应的最大距离称为位错反应半径a。在~1/模型中,当外延层厚度变化D时某一位错可与其他位错发生反应的区域如式(1)所示,任一位错将和数量为=的位错相遇并湮灭,为贯穿位错密度。因此位错密度随厚度的变化值Δ如式(2)所示,当D无限小后,将(2)式作积分处理后,得到位错密度与薄膜厚度的关系,如式(3)。

=2aD(1)

Δ=-=-2a2D(2)

式中:0为初始位错密度。

~1/2模型假设位错反应半径a¢随薄膜厚度增加而线性增加,与相遇的位错发生湮灭反应,位错反应半径a¢~,将其关系简化为a¢=,模型计算结果可给出位错密度数量级的估计。当外延层厚度增加时,任意位错反应的区域¢如式(4),其位错密度的变化D如式(5)所示,处理后得到式(6)。

¢=2pD(4)

D=-=-2p2D(5)

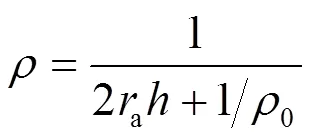

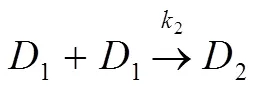

异质衬底与碲镉汞间通常需要制备一个碲化镉缓冲层,常规外延膜层结构如图1上部所示,0、1、2以及3分别表示衬底与碲化镉界面、碲化镉表面、碲化镉与碲镉汞界面以及碲镉汞表面4个位置处的贯穿位错密度。对于异质衬底上的碲化镉薄膜,采用上述两种模型进行了计算。其中衬底与碲化镉界面贯穿位错密度0取1×1010cm-2[7],a取1000[7]和0.7mm[9],为材料伯氏矢量,碲化镉厚度取8mm。计算结果如图1中0~8mm厚度范围内3条曲线所示,~1/模型计算结果(不同a取值)均与G. Badano等人[10]实验结果接近,a=0.7mm计算结果与实验结果吻合度更好。~1/2模型与实验值存在一个半数量级的偏离,这可能是模型假设中a¢=导致位错反应半径与实际值偏差较大造成的。验证了位错反应半径与材料剪切模量以及Peierls应力相关[7],主要由材料种类和生长温度所决定,而与厚度的关系不大。

对碲化镉缓冲层上的碲镉汞薄膜,采用~1/模型进行了计算。目前普遍认为碲化镉与碲镉汞间约0.2%的晶格失配将增殖出107~108cm-2量级[11-12]位错,计算中取2=1和2=101两个值,a取1000和0.7mm,碲镉汞层厚度取8mm。计算结果如图1中8~16mm厚度范围内4条曲线所示。初始条件为2=1、a=1000的计算结果与Ge基碲镉汞实验结果相近,说明Ge基碲镉汞EPD演化实验结果与界面无位错增殖、位错反应半径小的计算结果吻合度好,而初始条件为2=101、a=0.7mm的计算结果与J. D. Benson等人[11]的Si基碲镉汞实验结果相近,说明Si基碲镉汞EPD演化实验结果与界面位错增殖高、位错反应半径大的计算结果吻合度好。但值得注意的是,Ge、Si两种衬底上的碲镉汞EPD值较为接近。

从上述分析可以得出,位错反应半径和薄膜厚度是决定原生碲镉汞材料贯穿位错密度的主要参数。由于位错反应半径的限制,原生碲镉汞材料(8mm膜厚)贯穿位错密度无法降低至8×106cm-2以下,与长波器件对于碲镉汞位错密度的要求存在较大差距。为了进一步降低材料贯穿位错密度,位错抑制技术的引入是必须的。

2 异质衬底外延碲镉汞薄膜位错抑制技术进展

2.1 循环退火技术

循环退火(thermal cycle annealing,TCA)技术是出现最早、研究最为广泛的位错抑制技术。它不同于传统单周期长时间退火,而是通过短时间多周期循环对原生碲镉汞材料进行原位或离位热处理,利用高温在外延层与衬底之间引入的热失配应变,多次驱动位错进行运动,使位错相遇并发生反应,达到降低位错密度目的。循环退火技术典型退火温度曲线如图2所示[13],热循环中低温一般为250℃(位错运动激活温度),高温从300℃~600℃不等,样品每次在高温停留时间为单周期退火时间。

图1 异质衬底上碲化镉、碲镉汞材料贯穿位错密度随厚度的变化规律

注:图内示意图为膜层结构及各特征位置位错密度标记,方形及圆形数据点来自文献[10]和文献[11],分别为Ge基碲化镉和Si基碲镉汞EPD数据,菱形点为昆明物理研究所(KIP)Ge基碲镉汞EPD数据

Note: The schematic of HgCdTe layer structure and dislocations density symbols at each typical position were showed at top of the figure

循环退火技术最早由J. M. Arias等人[14]从GaAs/Si材料[15]借鉴到HgCdTe/GaAs材料中。其循环退火实验中,高温为490℃、低温为300℃、循环次数为4次,单周期退火时间为10min。经过循环退火处理,碲镉汞表面EPD值从初始的5×106cm-2降至2.3×105cm-2。此后,多家机构跟进开展了相关研究,但均无法重复J. M. Arials等人的结果[16-18]。以J. D. Benson组[16]的系统研究最具代表性,其针对HgCdTe/Si材料,选用400℃~600℃内多个高温温度进行了4~16次循环退火,材料中位错密度从1×107cm-2初值开始下降,并在1×106cm-2附近趋于饱和,与J. M. Arias等人得到的结果相差近一个数量级。

图2 循环退火典型温度控制曲线[13]

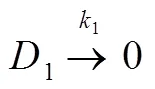

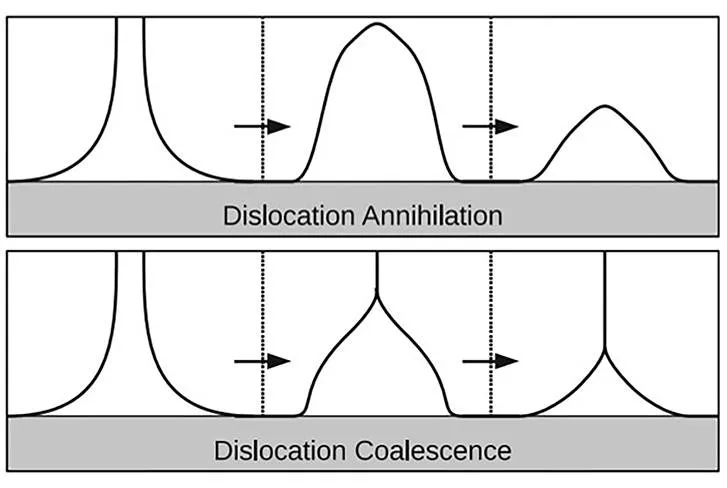

为了解释位错密度在循环退火后出现饱和的现象,J. D. Benson等人[15-16]进行了建模仿真,模型中不考虑位错间具体反应时需要满足的矢量条件和能量条件,直接将其简化为基元反应,分为湮灭反应(dislocation annihilation,位错消失于自由边界或界面,位错数量1®0)和合并反应(dislocation coalescence,两条位错相遇后合并为一条位错,位错数量2®1),如图3及式(7)、式(8)所示。

式中:1为滑动位错密度(位错在滑移面内,可自由运动);1为湮灭反应速率;2为钉扎位错密度(位错脱离了滑移面,无法继续运动);2为合并反应速率。1、2是位错运动速率的一次函数,退火温度越高,位错运动速率越大,1、2也越大,1、2可从实验数据中拟合得出,对于碲镉汞薄膜来说,2比1小6个数量级左右。

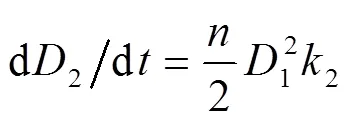

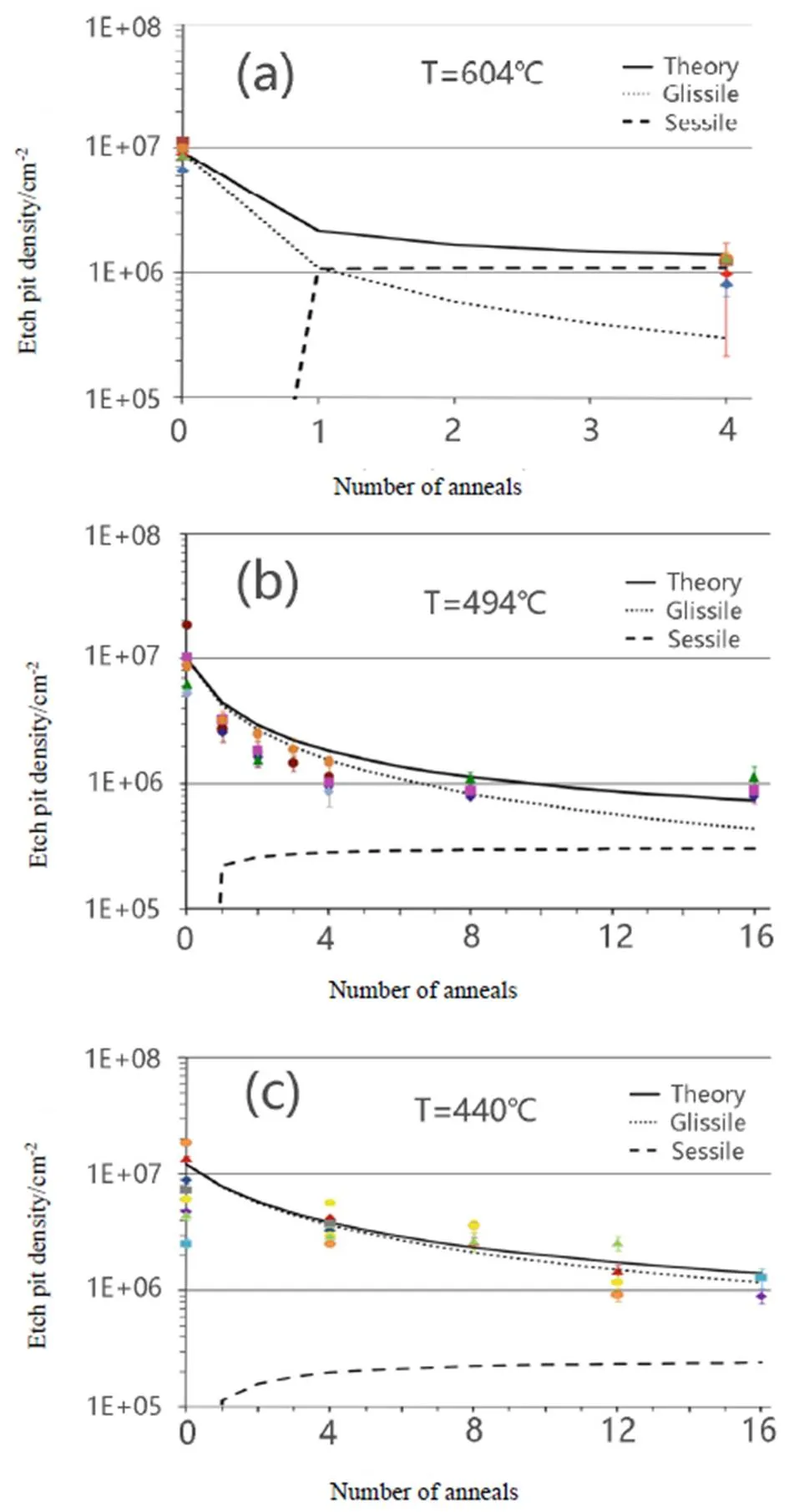

根据反应式(7)和式(8),可得到1和2的变化速率,如式(9)和式(10),其中为参与合并反应的滑动位错比例。对式(9)、(10)进行积分后,可以得到第一次循环后滑动和钉扎的位错密度值1(cycle1)和2(cycle1)值,相加后得到第一次循环反应后总位错密度值total(cycle1),如式(11)、(12)及(13)。

图3 两种位错反应类型示意[17]

d1/d=-11-212(9)

式中:0为原生材料位错密度;为退火时间。将前一循环total值作为下一次循环的0值,进行迭代计算,可得到次循环后滑动、钉扎、总位错密度值1(cycle)、2(cycle)及total(cycle)。

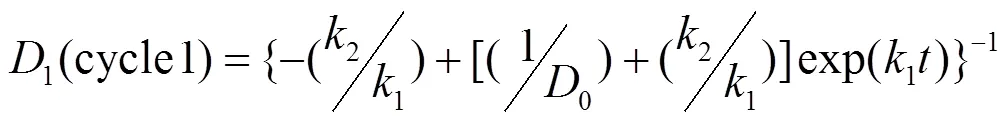

不同退火温度下仿真和实验结果如图4所示[16],可以看出在较高温度(604℃)退火,由于较大的2值,式(8)反应加快,钉扎位错密度上升较快,4次循环后即达到1×106cm-2,此时总位错密度无法得到进一步降低。而当降低退火温度,减小2值,增加循环次数时,钉扎位错密度可相应的降低,在440℃和494℃进行16次循环后达到3×105cm-2附近,但总位错密度仍处于1×106cm-2附近。

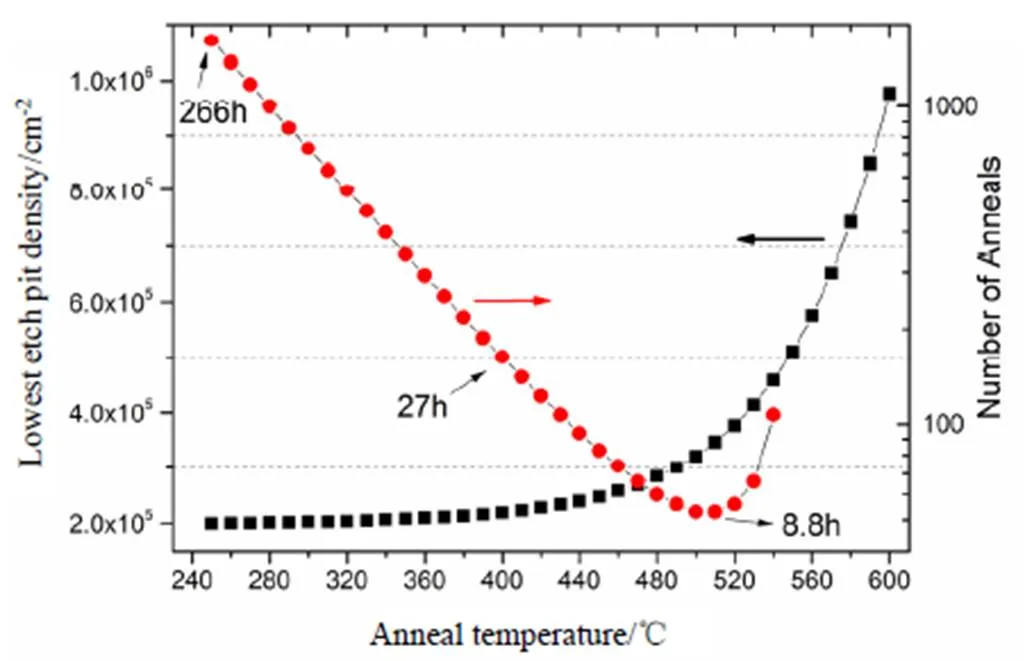

J. D. Benson模型中以上一循环total值作为下一循环的0值,但实际上每次循环仅有滑动位错1可参与到下一循环的反应中。因此本文使用上一循环1值作为下一循环的0值,在250℃~600℃范围,计算了材料中理论最小位错密度值(1<1×104cm-2时的钉扎位错密度2值),同时计算了材料位错密度从1×107cm-2降低到5×105cm-2时所需的循环次数及热处理时间,结果如图5所示。可以看出,退火温度不超过550℃时,材料总位错密度可控制在5×105cm-2以内,但温度越低,所需循环次数越高,250℃时需要超过100000周期,热处理时间为266h(每周期10min),而500℃所需周期数最低(53次),时间为8.8h。

图4 退火温度与位错抑制效果关系,点为实验结果,线为理论计算结果(每周期5min):(a) 高温温度为604℃;(b) 高温温度为494℃;(c) 高温温度为440℃[16]

多周期循环有望将异质衬底上碲镉汞材料位错密度降低到5×105cm-2,但由于所需循环数非常大,从可工程化的角度看,位错密度为5×105cm-2已经是循环退火技术可以达到的最低值。为了获得更加有效的位错抑制效果,出现了台面阵列退火技术和位错阻挡技术。

图5 循环退火处理后碲镉汞薄膜理论最低位错密度与退火温度的关系,材料位错密度降低至5×105cm-2时所需的循环次数及时间与退火温度的关系

2.2 位错阻挡技术

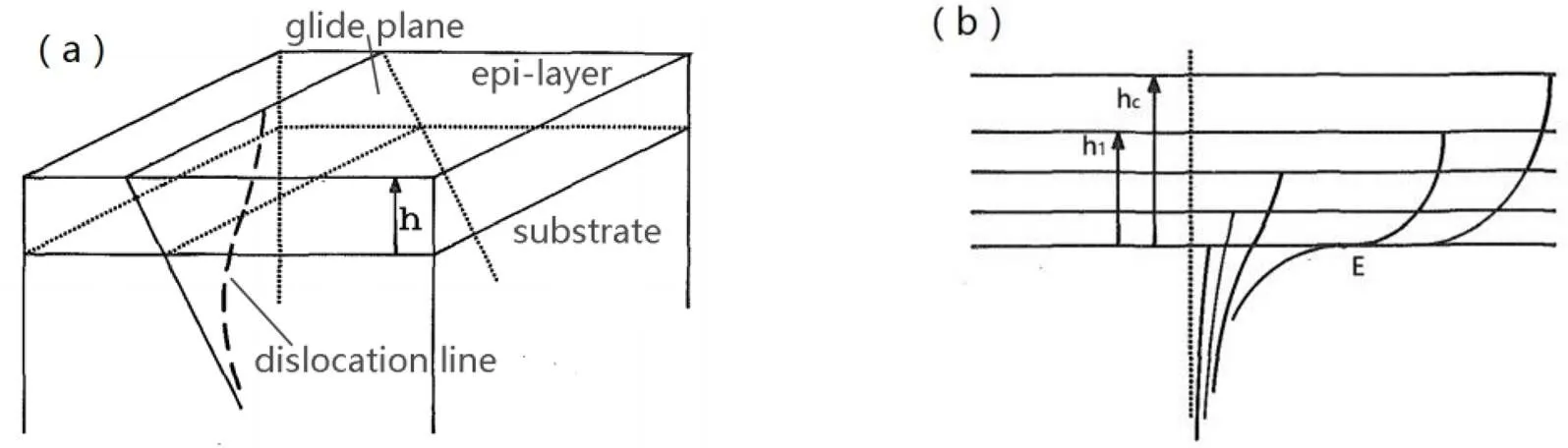

外延过程中,贯穿位错在界面处将发生偏转(图6(a)),偏转程度与失配度及外延层厚度有关(如图6(b))。当外延层厚度超过一定厚度1时(1<临界厚度c),位错达到最大偏转程度,此时位错将沿界面进行延伸,延伸长度可达厘米量级[20]。当薄膜厚度进一步增加超过临界厚度c后,位错又将转向并穿入到外延层中[21]。位错阻挡技术[8,22]利用了上述位错在界面处偏转并延伸的特性,人为制造具有一定失配度、厚度及层数的交替阻挡层,使位错被阻挡且沿阻挡层界面延伸,延伸过程中增加了位错间发生反应的概率,最终达到降低位错密度的效果。

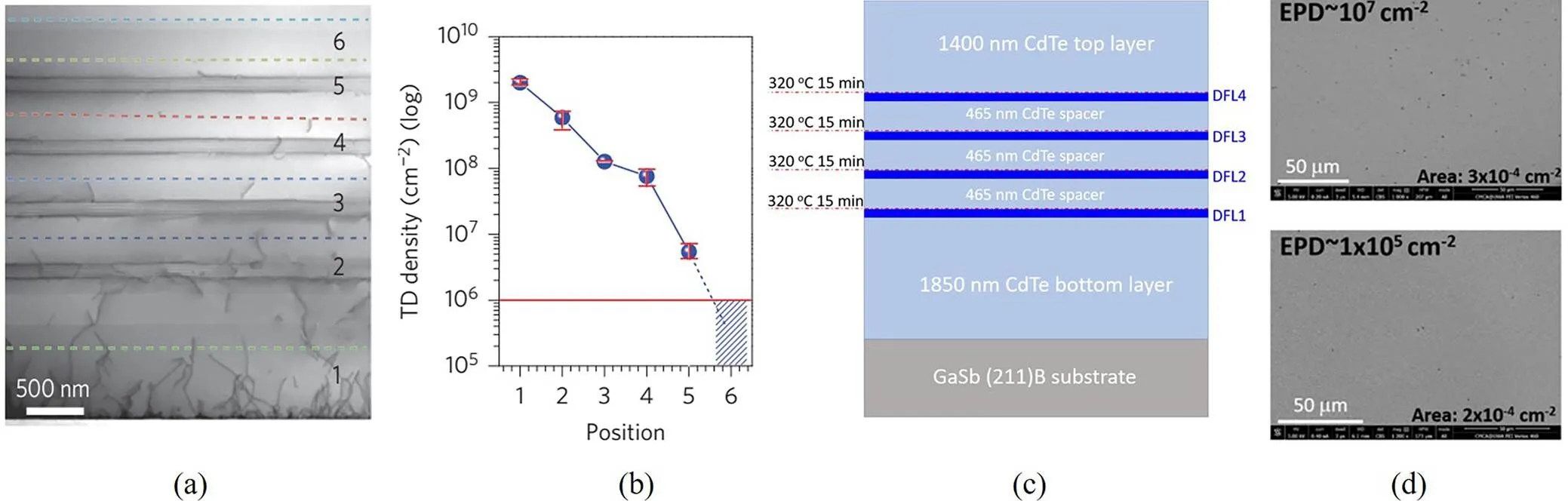

J. Wu等人[23-25]在Si衬底上制备InAs/GaAs量子点材料,使用位错阻挡层对GaAs缓冲层的位错密度进行控制,以降低贯穿位错对量子点红外器件性能的影响。位错阻挡层位于Si与GaAs界面处,包含4组重复结构,每组由5周期(10nm In0.18Ga0.82As/10nm GaAs)交替结构及300nm GaAs间隔层组成。经过位错阻挡,后续GaAs层中的位错密度降到了105cm-2量级,阻挡层结构及位错密度测试(TEM)如图7(a)、(b)所示。

W. Lei等人[26-27]在CdTe与GaSb界面处制备了两种位错阻挡结构,一种是30~50周期(4~5nm ZnTe/4~5nm CdTe)交替结构位错阻挡层,另一种由4组位错阻挡层组成,如图7(c)所示。每个位错阻挡层由5周期(12nm Cd0.85Zn0.15Te/13nm CdTe)交替结构和465nm CdTe间隔层组成。经过位错阻挡,异质衬底上碲化镉薄膜位错密度从1×107cm-2降至1×105cm-2附近,如图7(d)所示,这是异质衬底上制备的碲化镉材料目前达到的最低位错密度。

位错阻挡技术在Ⅲ-Ⅴ族和Ⅱ-Ⅵ族材料异质外延中均展现出了较好的位错抑制效果,但对于制备低位错密度碲镉汞材料来说,低位错密度碲化镉缓冲层只是一个必要前提。根据图1中的位错变化规律,碲镉汞与碲化镉间~0.2%的晶格失配仍将在碲镉汞中引入高系数107cm-2量级的位错,因此如何在高质量的碲化镉缓冲层上外延得到位错密度相当或更低的碲镉汞薄膜仍极具挑战。从位错抑制的角度分析,碲化镉与碲镉汞间的位错阻挡层或组分渐变过渡层是两种可能的途径。位错阻挡层方面,以HgCdTe/CdTe交替结构为例,由于交替结构间失配度小,为使位错在界面处偏转,阻挡层中交替结构的单层厚度需要超过数十纳米,加上间隔层后阻挡层总厚度将超过数微米。这需要在器件工艺中将位错阻挡层去除,降低其对辐射信号吸收产生的影响。组分渐变过渡层方面,需要通过控制Hg束流的方式从碲化镉渐变到碲镉汞,Hg束流的控制以及由于Hg/Te持续变化所需的生长温度调控难度均不小。总体来看,位错阻挡技术后续获得突破的技术难度较大。

2.3 台面位错吸除技术

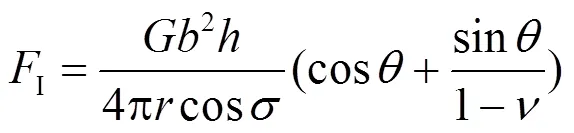

台面位错吸除的思想来源于选区外延,由P. Müller等人[28]最先提出,它是将外延材料进行台面成型,再进行退火处理,使台面上的贯穿位错移动并消失于台面侧壁的技术。由于碲镉汞与异质衬底间存在膨胀系数差D,提升材料温度将在碲镉汞与异质衬底界面处引入热失配(式(14)),失配应力将驱使位错发生运动。位错包含失配部分和贯穿部分,位错运动时,失配部分沿界面进行延伸,贯穿部分在滑移面内移动。X. G. Zhang对台面上位错的运动进行了静力学分析[29-30],由于台面侧壁自由边界的存在,台面内位错的贯穿部分将受到镜像力I作用(式(15)),牵引位错向台面侧壁运动,同时位错的失配部分将受到线张力L的阻碍(式(16))。当镜像力大于线张力时,贯穿位错可移出台面,平衡I与L,可得到镜像力作用最大有效距离max以及位错可完全移出的台面最大尺寸max(式(17))。

图6 异质外延中贯穿位错进入外延层时发生偏转及沿界面延伸示意[22]:(a) 位错在界面处的偏转发生在滑移面内;(b) 位错在界面处发生偏转的截面示意

图7 位错阻挡层结构及位错阻挡效果:(a) GaAs/Si界面附近In0.18Ga0.82As/GaAs阻挡层TEM照片;(b) GaAs/Si界面附近经多次位错过滤后位错密度的变化,位错阻挡层将位错密度降至1×106cm-2以下[25];(c) CdTe/GaSb界面处的Cd0.85Zn0.15Te/CdTe位错阻挡层结构示意图;(d) CdTe/GaSb材料阻挡层位错抑制效果,原生碲化镉EPD(上)及位错抑制后碲化镉EPD(下)[27]

=D×D(14)

(16)

式中:为剪切模量;为泊松比;为位错伯氏矢量;为薄膜厚度;为镜像力作用有效范围;为位错线与材料表面夹角,一般为60°(全位错);为位错线与其伯氏矢量间夹角。

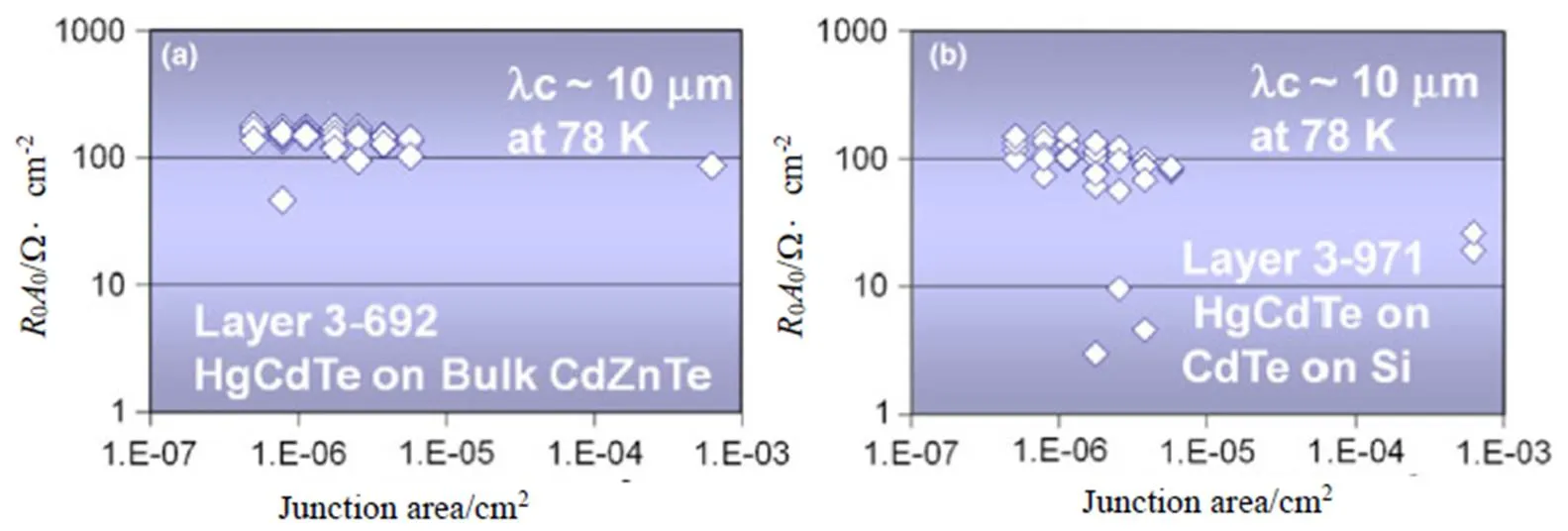

实验方面,A. J. Stoltz等人[31]在HgCdTe/Si薄膜上用等离子刻蚀制备了直径30mm,高8mm的台面,经过低温250℃、高温494℃四次循环退火,将碲镉汞位错密度从1×107cm-2附近降低到3×106cm-2,并且其位错腐蚀坑大多分布在台面边缘,台面中心位错密度接近0 cm-2。进一步器件结果显示,台面位错吸除处理的Si基碲镉汞制备的长波器件0值与碲锌镉基碲镉汞制备的长波器件0值相当,如图8所示。

使用式(17)对HgCdTe/Si材料位错可滑出台面最大尺寸进行计算,假设贯穿位错仅在碲镉汞单膜层中运动,即热应力驱动碲镉汞与碲化镉界面上的失配位错进行延伸,取CdTe/Si热膨胀系数为7.4×10-6K-1[32],HgCdTe(=0.2)热膨胀系数为5×10-6K-1[33],D=469K,=10mm(MCT)得到=34mm。假设贯穿位错在HgCdTe/CdTe双膜层中运动,热应力驱动碲化镉与Si界面处的失配位错进行延伸,取Si热膨胀系数为2.5×10-6K-1,=16mm(CT+MCT)得到=55mm。Stoltz的实验结果中位错并未完全消失于台面(台面尺寸为30mm),因此可认为单层膜假设中计算结果与实验更为接近。

台面隔离沟槽深度、沟槽侧壁角度等将影响位错去除效率及后续芯片工艺难度,需要对台面位错吸除与芯片加工进行工艺融合。由于镜像力可看作真空对位错的吸引力,隔离台面的沟槽越深,碲镉汞薄膜中贯穿位错受到镜像力作用的部分越多,因此通常需要刻蚀开槽到碲化镉与碲镉汞界面附近,即沟槽深度与碲镉汞薄膜厚度相当。另外,沟槽侧壁角度虽然与位错去除效率关系不大,但与器件占空比、侧壁钝化难度等直接相关。

图8 台面位错吸除处理的Si基碲镉汞制备的长波器件R0A值与碲锌镉基碲镉汞制备的长波器件R0A值比较[31]:(a) CZT衬底上生长的碲镉汞;(b) Si基碲镉汞

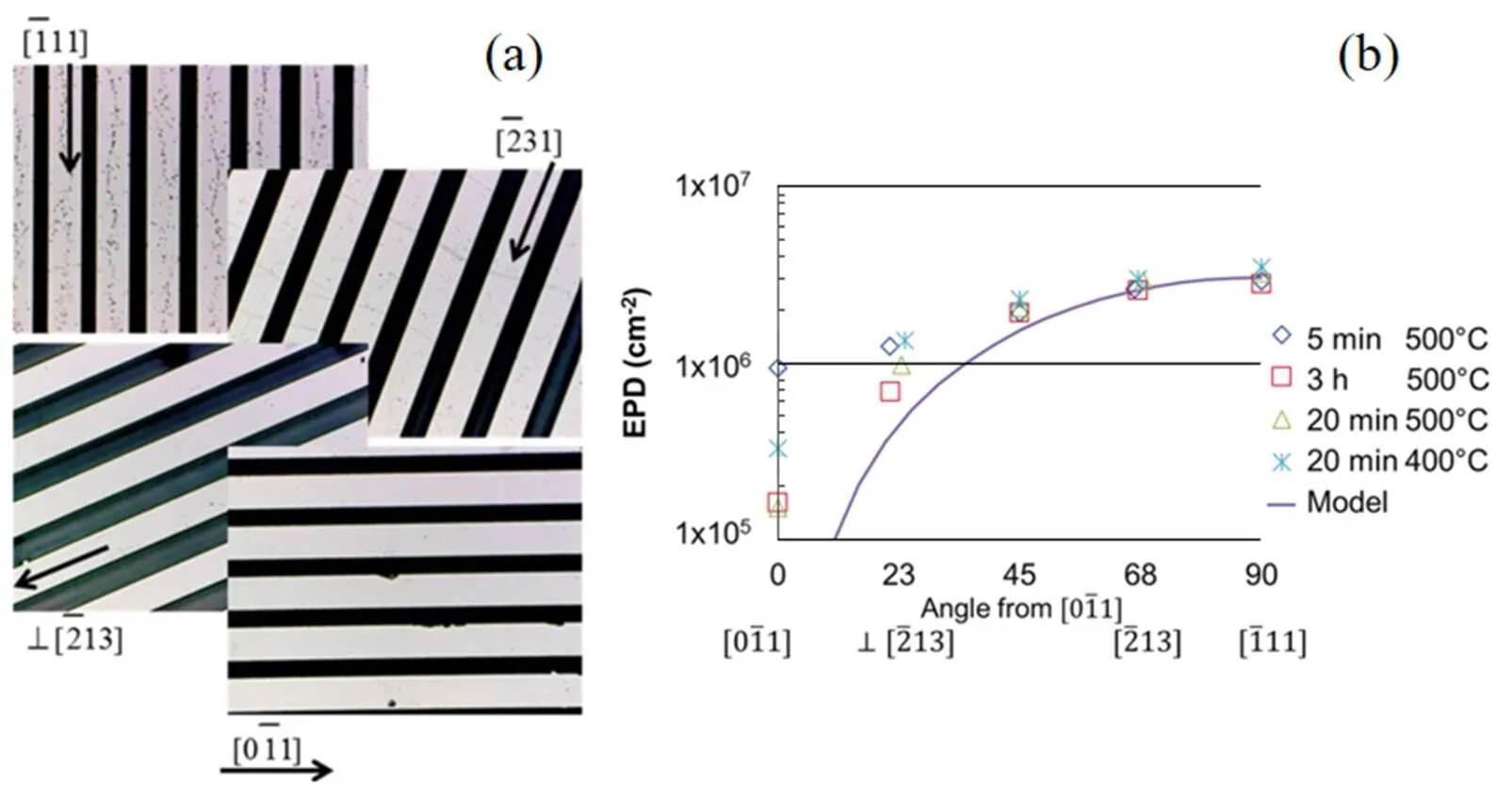

图9 不同方向长条台面位错抑制效果对比[34,36]:(a) 沿不同晶向台面退火处理后EPD情况;(b) 不同晶向台面在不同退火条件处理后EPD情况

3 结语

~1/模型可以准确地描述异质衬底上原生碲化镉、碲镉汞薄膜位错密度随厚度的变化规律,由于位错反应半径的限制,原生碲镉汞材料贯穿位错密度难以降低至5×106cm-2以下,与长波、甚长波器件对材料位错密度的要求存在较大差距,因此有必要引入位错抑制技术。

循环退火技术近年来得到了广泛研究,由于位错反应过程中钉扎位错的产生,碲镉汞薄膜位错密度容易在1×106cm-2附近将出现饱和。模型计算结果显示碲镉汞位错密度的进一步降低需要合适的退火温度和更多的循环次数,但多次循环退火工艺将引入表面劣化、材料中原子互扩散等问题。因此循环退火技术更适用于短波、中波器件探测性能提升,但对于长波及甚长波器件,其后续发展潜力不大。位错阻挡技术方面,目前异质衬底上碲化镉位错密度已降至1×105cm-2附近,后续的难点是在高质量碲化镉上制备出位错密度相当甚至更低的碲镉汞薄膜。在碲化镉和碲镉汞间的HgCdTe/CdTe位错阻挡层或组分渐变过渡层是可能的解决途径,但总体来看获得技术突破的难度较大。台面位错吸除技术目前针对HgCdTe/Si薄膜获得了较好的位错抑制效果,可以将材料位错密度控制在5×105cm-2以内,显示出了巨大的发展潜力和价值,后续将台面退火工艺与芯片工艺融合后,有望大幅促进低成本长波、中长波、甚长波器件的发展。

[1] LEI W, Antoszewski J, Faraone L. Progress, challenges, and opportunities for HgCdTe infrared materials and detectors[J]., 2015, 2(4): 041303.

[2] Kinch M A. The future of infrared; III–Vs or HgCdTe?[J]., 2015, 44(9): 2969-2976.

[3] Rogalski A. History of infrared detectors[J]., 2012, 20(3): 279-308.

[4] Jóźwikowski K, Jóźwikowska A, Martyniuk A. Dislocations as a noise source in LWIR HgCdTe photodiodes[J]., 2016, 45(10): 4769-4781.

[5] Johnson S M, Buell A A, Vilela M F, et al. HgCdTe/Si materials for long wavelength infrared detectors[J]., 2004, 33(6): 526-530.

[6] Gopal V, Gupta S. Effect of dislocations on the zero-bias resistance-area product, quantum efficiency, and spectral response of LWIR HgCdTe photovoltaic detectors[J]., 2003, 50(5): 1220-1226.

[7] Speck J S, Brewer M A, Beltz G, et al. Scaling laws for the reduction of threading dislocation densities in homogeneous buffer layers[J]., 1996, 80(7): 3808-3816.

[8] Ward T, Sánchez A M, Tang M, et al. Design rules for dislocation filters[J]., 2014, 116(6): 063508.

[9] Carmody M, Lee D, Zandian M, et al. Threading and misfit-dislocation motion in molecular-beam epitaxy-grown HgCdTe epilayers[J]., 2003, 32(7): 710-716.

[10] Badano G, Robin I C, Amstatt B, et al. Reduction of the dislocation density in molecular beam epitaxial CdTe (211) B on Ge (211)[J]., 2010, 312(10): 1721-1725.

[11] Benson J D, Bubulac L O, Smith P J, et al. Growth and analysis of HgCdTe on alternate substrates[J]., 2012, 41(10): 2971-2974.

[12] Jacobs R N, Benson J D, Stoltz A J, et al. Analysis of thermal cycle-induced dislocation reduction in HgCdTe/CdTe/Si(211) by scanning transmission electron microscopy[J]., 2013, 366(MAR.1): 88-94.

[13] Brill G, Farrell S, Chen Y P, et al. Dislocation reduction of HgCdTe/Si through ex situ annealing[J]., 2010, 39(7): 967-973.

[14] Arias J M, Zandian M, Shin S H, et al. Dislocation density reduction by thermal annealing of HgCdTe epilayers grown by molecular beam epitaxy on GaAs substrates[C]//, 1991, 235(1): 1646-1650.

[15] Yamaguchi M, Tachikawa M, Itoh Y, et al. Thermal annealing effects of defect reduction in GaAs on Si substrates[J]., 1990, 68(9): 4518-4522.

[16] Benson J D, Farrell S, Brill G, et al. Dislocation analysis in (112) B HgCdTe/CdTe/Si[J]., 2011, 40(8): 1847-1853.

[17] Farrell S, Rao M V, Brill G, et al. Effect of cycle annealing parameters on dislocation density reduction for HgCdTe on Si[J]. J, 2011, 40(8): 1727-1732.

[18] SHEN C, GU R J, FU X L, et al. Dislocation reduction in CdTe/HgCdTe film prepared by MBE on Si substrate[J]., 2011, 30(6): 490-494.

[19] Vaghayenegar M, Jacobs R N, Benson J D, et al. Correlation of etch pits and dislocations in As-grown and thermal-cycle-annealed HgCdTe(211) films[J]., 2017, 23(S1): 1526-1527.

[20] Szilagyi A, Grimbergen M N. Misfit and threading dislocations in HgCdTe epitaxy[J].:,,, 1986, 4(4): 2200-2204.

[21] Ciani A J, Chung P W. Simulations of dislocations in CdZnTe/SL/Si substrates[J]., 2010, 39(7): 1063-1069.

[22] Freund L B. A criterion for arrest of a threading dislocation in a strained epitaxial layer due to an interface misfit dislocation in its path[J]., 1990, 68(5): 2073-2080.

[23] George I, Becagli F, LIU H Y, et al. Dislocation filters in GaAs on Si[J]., 2015, 30(11): 114004.

[24] WU J, JIANG Q, CHEN S, et al. Monolithically integrated InAs/GaAs quantum dot mid-infrared photodetectors on silicon substrates[J]., 2016, 3(5): 749-753.

[25] CHEN S, LI W, WU J, et al. Electrically pumped continuous-wave III-V quantum dot lasers on silicon[J]., 2016, 10(5): 307-311.

[26] LEI W, REN Y L, Madni I, et al. Low dislocation density MBE process for CdTe-on-GaSb as an alternative substrate for HgCdTe growth[J]., 2018, 92: 96-102.

[27] PAN W W, GU R J, ZHANG Z K, et al. Strained CdZnTe/CdTe Superlattices As threading dislocation filters in lattice mismatched MBE growth of CdTe on GaSb[J]., 2020, 49: 6983-6989.

[28] Müller P, Zogg H, Fach A, et al. Reduction of threading dislocation densities in heavily lattice mismatched PbSe on Si(111) by glide[J]., 1997, 78(15): 3007-3010.

[29] ZHANG X G, LI P, ZHAO G, et al. Removal of threading dislocations from patterned heteroepitaxial semiconductors by glide to sidewalls[J]., 1998, 27(11): 1248-1253.

[30] ZHANG X G, Rodriguez A, WANG X, et al. Complete removal of threading dislocations from mismatched layers by patterned heteroepitaxial processing[J]., 2000, 77(16): 2524-2526.

[31] Stoltz A J, Benson J D, Carmody M, et al. Reduction of dislocation density in HgCdTe on Si by producing highly reticulated structures[J]., 2011, 40(8): 1785-1789.

[32] Jacobs R N, Markunas J, Pellegrino J, et al. Role of thermal expansion matching in CdTe heteroepitaxy on highly lattice-mismatched substrates[J]., 2008, 310(12): 2960-2965.

[33] Kasap S, Willoughby A. Mercury Cadmium Telluride: Growth, Properties and Applications[M]. John Wiley & Sons, 2011.

[34] Stoltz A J, Benson J D, Jacobs R, et al. Reduction of dislocation density by producing novel structures[J]., 2012, 41(10): 2949-2956.

[35] Jacobs R N, Stoltz A J, Benson J D, et al. Analysis of mesa dislocation gettering in HgCdTe/CdTe/Si (211) by scanning transmission electron microscopy[J]., 2013, 42(11): 3148-3155.

[36] Simingalam S, Pattison J, Chen Y, et al. Dislocation Reduction in HgCdTe Mesa Structures Formed on CdTe/Si[J]., 2016, 45(9): 1-6.

Research Progress of Dislocation Density Reduction in MBE HgCdTe on Alternative Substrates

YANG Jin,LI Yanhui,YANG Chunzhang,QIN Gang,LI Junbin,LEI Wen,KONG Jincheng,ZHAO Jun,JI Rongbin

(,650223,)

HgCdTe has dominated the high-performance IR detector market for decades. Owing to its numerous merits, including precise energy band structure control and device structure growth, theMBE(molecular beam epitaxy) growth of HgCdTe has become the main tool for fabricating third-generation IR focal plane arrays. CdZnTe is widely considered to be an ideal substrate for HgCdTe epitaxy because of the matched lattice through Zn fraction adjustment. Therefore, HgCdTe/CdZnTe has a high crystal quality with a typical etch pit density in the range of 1´104–1´105cm-2. However, several limitations, such as high cost, small wafer size, and low yield, still exist in the (211) CdZnTe substrate, which results in high cost and limits the array format size in infrared detectors based on HgCdTe/CdZnTe. Compared with CdZnTe substrates, alternative substrates (e.g., Si, Ge, GaAs, and GaSb) have large wafer size, low cost, and convenience in standard semiconductor equipment, which have the potential to fabricate low-cost high-performance focal plane arrays. The main issue in HgCdTe on alternative substrates is the large lattice mismatch between the substrate and epi-layer (19.3%, 14.3%, 14.4%, and 6.1% for Si, Ge, GaAs, and GaSb, respectively), which is responsible for the high dislocation density of 106–107cm-2in HgCdTe films. The high dislocation density hampers the application of this material to long-wavelength and very long-wavelength infrared detectors.The variation in dislocation density with film thickness in the as-grown HgCdTe film grown on an alternative substrate was modeled, and the results from the ρ~1/h law agreed well with the experimental data. This indicates that the dislocation annihilation radius is the leading cause of impeding the dislocation density below 5´106cm-2in HgCdTe; thus, dislocation reduction is urgently needed. Moreover, the theory and research progress on three dislocation reduction methods, namely thermal cycle annealing (TCA), dislocation blocking, and mesa dislocation gettering (MDG), are summarized in this paper. Prospects and priorities for future development are also discussed. Overall, TCA and dislocation blocking techniques are likely to be harder in technical breakthroughs andhave less development potential in dislocation reduction tobelow 5´105cm-2. By contrast, the MDG technique has shown tremendous development potential and high value in low-cost long-wavelength infrared detectors; however, process integration between the MDG technique and standard focal plane array fabrication is needed.

HgCdTe, alternative substrates, dislocation reduction, thermal cycle annealing, dislocation blocking, mesa dislocation gettering

TN304

A

1001-8891(2022)08-0828-09

2021-03-10;

2021-04-16.

杨晋(1990-),男,博士研究生,主要从事红外光电材料的研究工作。E-mail:buaamseyj@163.com。

核高基重大专项项目。