基于FPGA和ADS8568的多路水声信号采集系统

2022-08-12付传宝

黄 敏,付传宝

(1.中国电子科技集团公司第三十四研究所,广西 桂林 541004;2.中国船舶重工集团750试验场,云南 昆明 650051)

0 引言

近十年来,为了了获取连续、系统、高分辨率水声信号,一般采用多个(少的几十个,多的上百个)低成本、低功耗、多功能的传感器布置在特定区域构成一个大范围多节点的水声信号采集网络[1],在水下对微弱信号进行采集后利用光纤传输容量大、质量轻、保密性好等特点实现采集信号的上传。各个节点协同完成信号采集、传输,实时获取区域全方位、立体、长时间的信号信息,为相关水下实验或环境监测提供数据支撑。本文针对该应用环境,采用多通道ADS8568采样、FPGA信号处理搭建一个水下信号采集传输系统,实现了区域内水声信号的高可靠性、低功耗的实时采集、传输。

1 采集传输系统设计

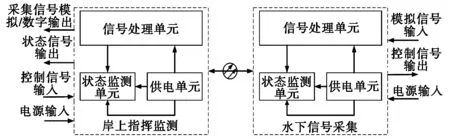

系统组成方式如图1所示。

图1 系统组成方式

在水下信号采集部分,多路水下信号输入到信号处理单元,实现水声信号的AD采集、采集后AD信号的预处理、多路并行数字信号数据复用、编码、电/光转换,将模拟信号、状态监控信号转换成高速串行光信号,采用一芯光纤传输到岸上指挥监控室;水下信号处理单元同时通过光/电转换、CDR(时钟恢复)、解码、数据解复用从光信号中解析出控制信号等输出给末端设备。

在岸上指挥监测部分,信号处理单元通过光/电转换、CDR(时钟恢复)、解码、数据解复用实现高速光信号到电信号的转换,从高速串行光信号中解析出并行数字信号、水下信号采集部分的状态监测信号,解析出来的并行数字信号按照系统约定的格式以并行数字接口、网络数据包或者经DA还原成模拟信号输出;状态监测信号与岸上部分的状态监测信号一起打包成以太网/异步数据(RS232/RS422)格式,通过以太网/异步数据接口输出;岸上指挥监测同时将用户控制室输入的控制信号经数据复用、编码、电/光转换将电信号转换成光信号通过一芯光纤传输到水下信号采集部分。

状态监测单元完成两部分的工作状态的实时监测(光状态、电源状态、链路连接状态等),并将所有监测数据打包上传给岸上、输出给用户。供电单元为系统两部分电路提供稳定、低噪声的工作电源。

2 各功能单元设计

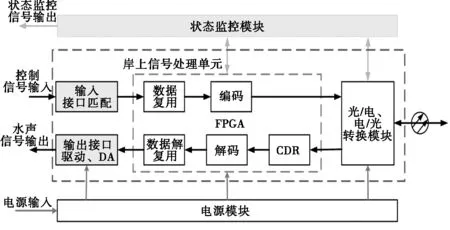

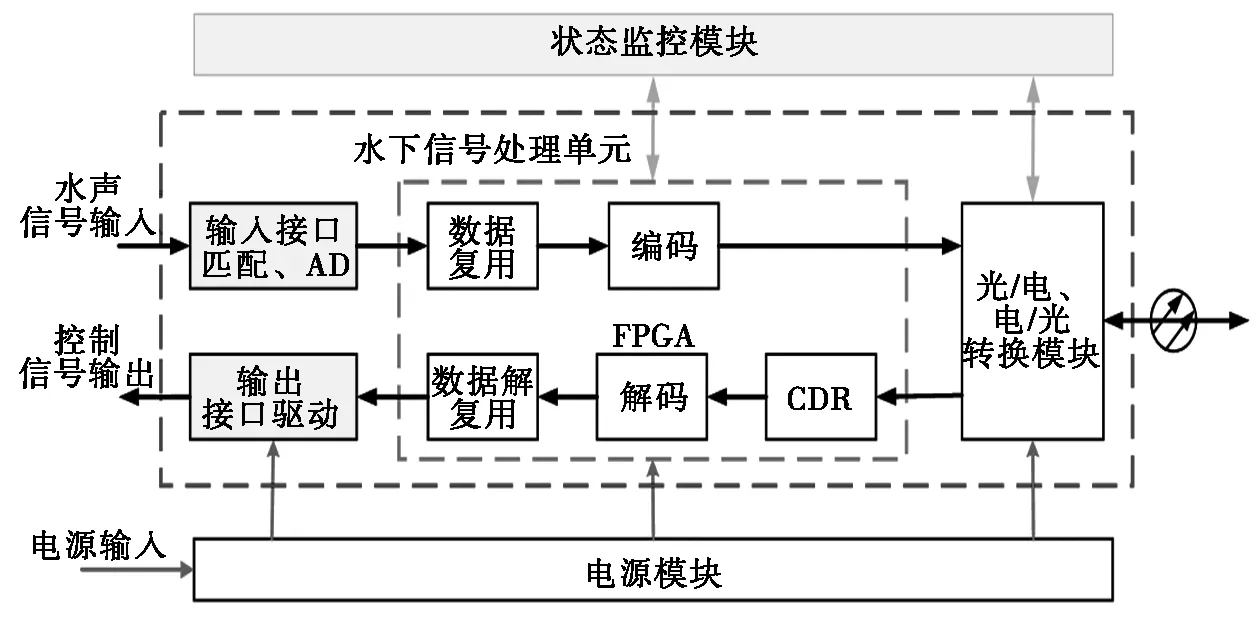

2.1 信号处理单元设计

岸上指挥监控部分和水下信号采集部分均包含有信号处理单元,各自功能框图如图2,图3所示,两部分信号处理单元都包含有数据复用、数据解复用、编码、解码、CDR、光电/电光转换模块,不同之处主要有:1) 水下信号处理单元增加了一个实现信号采集的AD模块;2) 岸上指挥监控部分包含一个将数字信号还原成模拟信号的DA模块;3) 状态监控信号输出方式不同,水下部分状态监控信号通过复用上传到岸上部分,与岸上的状态监控信息一起打包输出给用户。

图2 岸上信号处理单元

图3 水下信号处理单元

各部分主要实现的功能如下:

输入接口匹配/输出接口驱动:将用户输入RS232/422电平转换成LVTTL接口、将LVTTL电平转换成后端用户所需的RS232/422,实现用户接口电平与设备内部FPGA的IO引脚之间的匹配、驱动。

数据复用/数据解复用:实现信号的复接与还原,数据复用将多通道AD采样的低速并行信号、用户输入的控制信号按时分复用的方式转换成一路高速串行信号,然后送到数字发射光模块,变成光信号通过光纤传输。数据解复用采用CDR还原出来的时钟作为工作时钟,从光纤传送过来的高速串行信号中解析出并行信号,实现信号的还原。

编码/解码:为了提升系统的可靠性,保证传输的数据在接收端能正确复原,需要将转换后的高速串行信号采用8B/10B方式进行编码,使得发送的“0”、“1”数量保持基本一致,连续的“1”或“0”不超过5位,即每5个连续的“1”或“0”后必须插入一位“0”或“1”,从而保证信号DC平衡,也就是说,在链路超时的情况下不致发生DC失调。同时利用一些特殊的代码(如K码),可以帮助接收端进行还原的工作,并且可以在早期发现数据位的传输错误,抑制错误继续发生;在接收端则需要对信号解码,按照编码规则从扰码数据中还原出原始的高速串行信号,进入下一步的解复用环节。

CDR:即时钟恢复,从接收到的数据信号中恢复出时钟信号,以及使用恢复出来的时钟对数据进行重定时[2],为后续数据处理提供与数据同步的时钟信号。

光/电、电/光转换模块:主要完成光信号-电信号之间的转换,使信号通过光纤进行传输。

2.2 电源模块设计

系统采集的水声信号频率范围为20 Hz~80 kHz,幅度一般很小,经前级放大后输入到水下采集板的幅度一般为mV级,因此在系统设计时需要将系统本身引入的干扰尽量降低。系统本身引入的干扰主要为电源干扰,水下系统供电电源一般为24 V或者更高的直流电源,为了得到内部所需要的各种供电电源需要进行二级转换,直流电源转换成系统内部所需的各种电源的方式有两种:一是采用LDO;二是采用DC/DC。

LDO(线性稳压器)的成本低,噪音低,静态电流小,需要的外接元件也很少,一般只需要一两个旁路电容,目前LDO线性稳压器基本都可以做到输出噪声30 μV,PSRR为60 dB,静态电流6 μA;但LDO最大的劣势在于其输入电流等于输出电流,当输入与输出压差过大时会大大增加系统的功耗,另外由于增加的功耗都体现为LDO器件的热耗,造成该器件局部过热降低系统可靠性。DC/DC为采用开关方式实现直流到直流电源转换方式,优点是效率高、输出电流大、静态电流小;缺点是采用脉冲开关方式开关频率对信号有干扰以及噪音较大。考虑到水下信号采集系统要求设备功耗尽量小,但设备信号频率在80 kHz以内,使用DC/DC时可以将其开关频率设计为大于300 kHz,避开信号频段,后端使用滤波器可以将开关频率对信号带来的干扰去除,因此在设计中选用DC/DC模块实现电源转换。

2.3 监控模块设计

监控模块主要为提升系统可靠性及实用性而设计,采用FPGA/ARM在设备内部对设备核心单元(光链路状态、信号状态、电源状态)的工作状态进行实时采集,水下端采集的状态与数据一起通过光纤传输到岸上端,在岸上端与岸上的状态信息一起打包成以太网/串口数据,后端用户通过该接口及协议,可以直接获取设备的工作状态信息,实时了解设备各个核心部件工作状态,为相关决策提供数据支撑。

3 系统核心功能部分分析

由于设备水下信号采集部分放置于水下,基于设备远距离供电及维修难度方面考虑,在设计中设备功耗、体积要求尽量小、可靠性越高越好。系统核心部分为信号处理部分和水下AD部分,这两部分的选择设计决定了系统的功耗、体积及可靠性指标。

信号处理单元功能主要是数据复用/解复用、编码/解码、CDR。设计时可以选用如下两种方式实现:一是各个功能单元均采用独立硬件方式实现,该方式设备硬件设计复杂度增加、功耗较大;二是采用现场可编程门阵列(FPGA)实现,FPGA内部逻辑资源丰富,集成时钟管理模块、存储管理模块及高速串行收发器,通过软件设计可以简洁方便的实现信号复用/解复用、编解码、CDR等所需信号处理功能,同时由于其核心电压1.2 V,与硬件方式的3.3 V相比功耗较低。从硬件设计复杂度、功耗方面考虑选用FPGA软件方式实现信号处理单元功能。在FPGA选型时基于满足软件设计要求的情况下选用XILINX的中端低功耗器件SPARTAN-6系列的XC6LX45T。该款FPGA内部有43 k逻辑单元,最大296用户IO端口,4个GTP通道通过内部IP核实现4通道最大3.2 Gbps的高速串行收发器,内部资源满足系统软件设计资源需求,同时在采用双向单通道GTP情况下,器件功耗约1 W[3]。

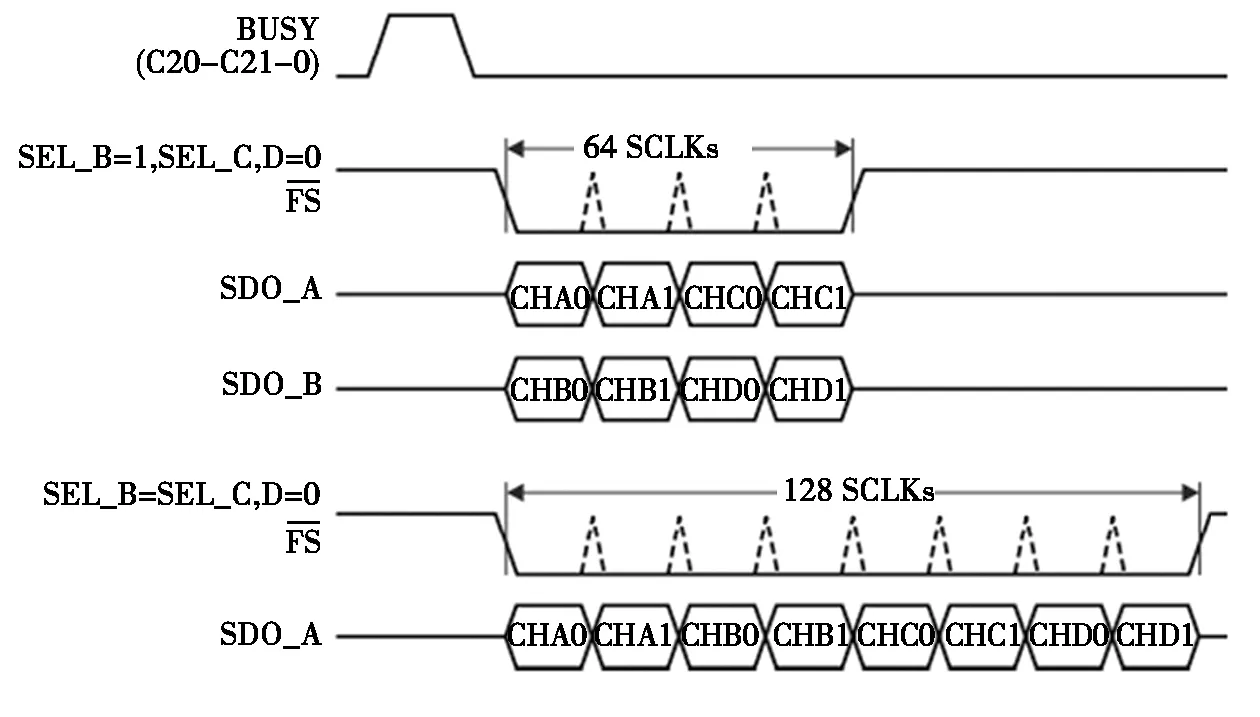

模拟信号模数转换一般采用单/双通道A/D实现。系统需要采集/监测目标区域全方位的水声信号信息,外部自带的模拟水声信号探测/采集器较多,一般为少则几十,多则上百;使用该方式需要用到几十片甚至上百片AD,系统硬件设计复杂,同时容易引起的各个采样电路之间的相互干扰。综合考虑系统中水声信号的频率特性及系统要求,为了降低系统复杂度,选用多通道串行A/D转换器ADS8568进行数采集,该A/D内部包含8个同步16位ADC,在外部基准电压3V时通过软件设计支持最大±12 V的模拟输入,最大采用速率为400 kSPS,信噪比91.5 dB,谐波失真-94 dB,器件最大功耗389 mW,待机功耗32 mW。器件在串行工作模式下时序逻辑如图4所示。

图4 4ADS8568串行工作模式时序逻辑图[4]

4 实际应用及结论

实际应用中在水下信号采集端使用8片ADS8568完成64路模拟水声信号的采集及传输,在接收端还原的信号精度最小为1 mV,信噪比≥82 dB,失真度≤-80 dB,水下信号采集部分功耗小于8 W。通过采用多通道ADS8568完成监测地点/试验场所全方位模拟水声信号的AD采样,利用FPGA内部资源实现数据复用/解复用、编解码、CDR等信号处理过程,将采样的信号通过光纤上传,为后端用户的信号处理分析提供了高精度、实时、可靠的数据支撑;同时由于采用了多通道AD及FPGA,简化了系统硬件复杂度、降低了设备功耗、提升了设备工作稳定性与可靠性。