基于FPGA的改进型电子安全与解除保险系统

2022-08-12孙国先

张 旭 孙国先

(西安机电信息技术研究所,陕西 西安 710065)

1 引言

与传统机械式、机电式引信安全解除保险系统相比,全电子安全解除保险系统(Electronic Safety and Arming System,ESA)具有更大的优势,系统全部由电子元件组成,具有较高的安全性、可靠性以及良好的抗干扰性能。全电子安全与解除保险系统能够使用多种环境信息作为解除保险的激励信号,极大地拓展了全电子安全与解除保险系统的应用领域[1,2]。

一般来说,电子安全与解除保险装置的逻辑控制器包括ASIC、ARM、单片机等。早期FPGA产品的功能和性能有很多局限性,如功耗高、成本高、密度低、加工速度慢等,实现电子安全与解除保险装置功能的控制器通常采用ASIC 技术。ASIC 技术的应用大大降低了产品的成本和规模,同时提高了产品的可靠性,推动了全电子安全与解除保险装置小型化、集成化的发展[3]。然而,随着近几十年来FPGA技术的快速突破,FPGA产品的性能不断得到显著提高,其大量应用在工业控制领域。与传统ASIC相比,FPGA产品具有可编程性强、易于修改等特点,具有极大的灵活性。此外,应用FPGA技术开发电子安全与解除保险装置能大大缩短研发周期,同时能很好地控制成本[4]。在系统设计的正常水平上,FPGA产品正在迅速占据原来由ASIC产品占据的市场份额。

虽然ARM 和单片机价格低廉,在工业上得到了广泛的应用,但在高温、强磁场、强冲击和振动等恶劣环境中应用时可靠性较差。为了解决现有单片机ESA 系统的不易修改性及变成性差的问题,同时为了极大地适应ESA系统在强电磁干扰等恶劣环境条件下使用的安全性及可靠性,提出了采用双FPGA 芯片作为ESA 系统解除保险的逻辑控制单元。两个FPGA控制器主要负责识别弹上环境激励信号,同时也控制解除相应的保险开关。本文最后对整个工作过程进行了仿真和相应的分析,验证了该系统的正确性和有效性。

2 电子安全与解除保险系统

导弹发射后将经历不同的物理场,包括力场、声场、电场、热场和磁场[5]。选择不同的环境信息作为解除保险的激励信号需要考虑两个因素,一方面,它必须有一个独有的特征,能够区别于其他环境信息。另一方面,这种环境信息必须能够利用技术手段方便地被检测和识别[6]。

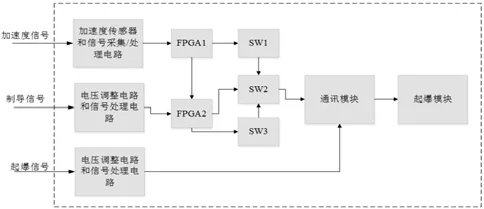

经过试验表明,火箭发动机产生的加速度是稳定的,并且持续很长时间。弹上控制系统给出的制导信息是在导弹飞行的某个时刻,具有唯一性。这两种解除保险的环境激励信号都具有唯一的特点,同时易于检测和识别。因此,选择发动机加速度和制导信息作为解除保险的环境激励。本系统框架如图1所示。

图1 电子安全和接触保险系统组件

为了识别导弹发动机在点火以后产生的加速度,采用AD22035 加速度传感器来识别加速度信号。加速度传感器由信号滤波电路、放大电路和AD0805 组成的信号处理电路对加速度模拟信号进行处理。然后将经过AD转换后的数字信号输入到FPGA1 器件中进行进一步的可靠识别,当可靠识别到加速度信号时打开电子开关SW1。

当制导信息到达时,相应的开关闭合,接通15V 电源。该信号经滤波后调整到标准电压3.3V,最后输入到FPGA 2器件中进一步可靠识别。

ESA 系统中的三个电子开关起着保持系统安全的作用。当各级解保环境信号均被正确识别时,电子开关将打开,相应的保险解除。当所有三个开关都打开时,ESA 系统处于解除保险状态。简而言之,两个微控制器FPGA1和FPGA2负责环境激励信号的识别,同时两个控制器协同工作生成驱动信号以打开所有开关,解除所有保险使ESA系统处于保险解除状态。

3 系统工作原理

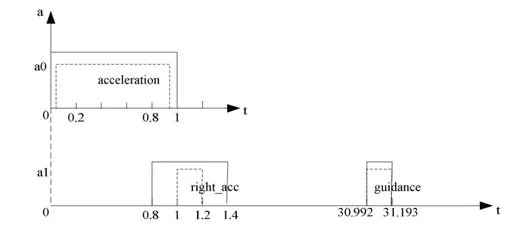

整个ESA系统处于安全状态时,三个负责保险的电子开关均与解保电源断开。由于没有向通信模块提供电源,因此在安全状态下,起爆控制器FPGA3不工作。当导弹发射后,两个FPGA控制器协同工作将按顺序打开三个电子开关,当所有开关均被打开后,引信由安全状态转入解除保险状态。图2为两个环境激励信号识别原理和相应时序。

图2 环境激励识别的原理

在图2中,“a0”和“a1”的代表环境激励信号的阈值。“t”表示导弹工作时间,其单位为秒。虚线代表有效信号,而实线代表时间窗口。从图中可以看出,所有的三个信号是由阈值和三个时间窗分别判断[7]。

控制器FPGA1 用于识别导弹发动机加速度信号,其工作频率为1MHz。导弹发动机产生的加速度信号将持续很长时间。因此,信号识别策略采取了两个原则,就是信号幅度和时间窗口。对于此特定应用场景,将选择20g加速度作为阈值,当其幅度大于20g的信号被认为是预定的信号。同时如果这一预定信号持续时间超过0.8s,以及小于1s,则此信号识别为正确有效信号。加速度信号进行有效识别后,控制器FPGA1 将输出两个信号,right_acc 和sw1。其中right_acc作为反馈信号保存在FPGA2中,而sw1信号用作打开电子开关SW1的驱动信号。

控制器FPGA2的工作频率为1kHz。当right_acc保持高电平为0.2s,则该时间窗口方法用于进一步识别信号的有效性。如图2 所示,right_acc 的时间窗口为0.8s~1.4s。只有当right_acc持续在这个时间窗口内时,系统才认为它是有效的信号。然后,识别right_acc作为正确有效信号所需时间保存在FPGA2中的CNT3计数器。

控制器需要识别的另一个解保环境信号是制导信息。利用控制器FPGA2 识别制导信号,同样,也采用阈值+时间窗的方法来识别该信号。当其电压上升为逻辑高电平时,FPGA2 相应计数器开始计算其持续时间。如果高电平持续时间超过0.2s,则该信号被认为是正确有效的。此时,FPGA2输出sw2信号以驱动SW2开关打开。同时FPGA2计数器也保存有效的制导信息到达的时刻。然后FPGA2 比较right_acc 的到达时间和制导信息到达时间。如果right_acc信号先出现并且制导信息后到达,则FPGA2将输出sw3以打开开关SW3。如果没有,则没有信号输出,并且开关保持与电源不连接,则整个系统处于安全状态。

4 实验验证

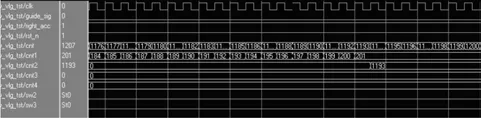

本系统采用Altera 公司生产的Cyclone II FPGA 进行设计实现。在QuartusII 软件中编写和编译Verilog HDL 程序,借助Modelsim仿真软件进行时序仿真,仿真结果如图3至图7所示。

图3 FPGA1从AD读取数据

图3表示出控制器FPGA1从AD设备中读取加速度信号的过程。图3中显示的所有信号解释如下:

Clk是FPGA1的基本工作频率大小为1MHz。rst_n表示复位信号,当rst_n为逻辑低时,内部信号的值被重置。Wr_n用作来控制AD设备,当wr_n为逻辑低电平时,AD设备将复位,同时d0~d7 的值变为零;当它变为高电平,开始数据传输,在进行数据传输期间,intr信号保持逻辑高。在64个时钟周期之后,8位二进制代码被传送到输出锁存器同时将intr变为逻辑低电平。Intr信号的逻辑低表示整个AD数据完成传输。当数据传输完成,rd_n 信号变为低电平,FPGA1 可以读取d0~d7 的值,将读取到的数据临时存储到一个8 位寄存器中,该寄存器的名称为read_data。然后在下一个时钟周期内,FPGA1通过相关指令将该值与设置的阈值进行比较。如果它超过阈值,则cnt2的值将加1。如果不是,则cnt2的值保持不变。此时,wr_n变为逻辑低电平,将进行下一次的信号识别和传输过程。

图4 表示加速度信号的识别结果。如图4 所示,在1s 的时间窗内当read_data里面保存的值超过阈值时,计数器cnt2的值就会增加。在1s的时间窗之后,将cnt2和11765的值之间进行比较。根据图4,若cnt2 累计值超过11765,这表明加速度信号的持续时间超过0.8s(计算公式如下:11765×0.068=800.2ms),当幅值和持续时间都满足要求时则认为该信号为有效信号。同时在下一个时钟周期到来时,将right_acc 和sw1 都置为高。sw1 信号驱动打开开关SW1,并且将right_acc作为反馈信号传输给控制器FPGA2。

图4 识别加速度信号的结果

图5 FPGA2信号的仿真结果

FPGA2 的工作频率为1 kHz。仿真时间设置为35s。根据图4,该系统在31194ms完成解保。

FPGA2 中为了识别right_acc 信号,使用阈值+时间窗的方法。当right_acc 变高时,cnt1 开始记录其持续时间,如果持续时间为200ms,则在时间窗内进一步识别它。从图4 可知,right_acc 将在1s 内传输给FPGA2。在识别其预设阈值200ms 后,FPGA2 中的时间窗在1s~1.4s 的范围内。根据图6,right_acc在1193ms到达,在预设的1s~1.4s的范围内,将其视为有效的信号,同时将该值记录到cnt3中以进一步识别。

图6 识别right_acc信号的结果

图7 识别制导信号和输出

图7所示是识别制导信号的过程。为了识别制导信号,使用时间窗口的方法。如果此信号变高并持续200ms,则视为正确信号。当可靠识别到制导信号后,sw2变量置高,驱动打开电子开关SW2。同时,cnt4 记录识别制导信号的时间。在下一个时钟周期中,比较cnt2 的值和cnt4 的值,可以明确两个环境激励信号到来的先后顺序。如果cnt3 的值小于cnt4 的值,则sw3 将变高,然后打开电子开关SW3。如果不是,则sw3保持低电平,开关SW3不会打开。

5 结语

本文提出了基于FPGA 的电子安全与解除保险系统。通过改进现有基于ARM 和单片机作为逻辑控制单元的体系,通过使用两个FPGA 芯片进行保险解除的逻辑控制单元,使得设计过程变得更容易,开发周期短,产品易于修改。通过实验模拟和仿真分析了基于FPGA 的电子安全和解除保险系统的整个工作过程,模拟和仿真时序表明本系统能够基于“阈值+时间窗”两个信号识别原则正确区分不同的环境激励信号。结果表明该系统能替代现有的基于ARM 和单片机的ESA 系统,方法可行、有效,符合相应国军标的要求。此外,在设计过程中,严格遵循了几个重要的设计标准。依据这些标准[8,9],两个FPGA 芯片应该在不同的时钟频率下工作,以防时钟问题可能导致两个FPGA 器件都出现故障。本系统中,两个FPGA 工作在不同的时钟频率,这不仅符合设计标准,而且使系统更可靠。