应用QFN封装的CMOS运算放大器芯片设计

2022-08-06陈宏,杨树,郭清,刘立

陈 宏, 杨 树, 郭 清, 刘 立

(浙江大学电气工程学院,杭州 310027)

0 引 言

作为信息产业重要基础的集成电路产业已成为现代制造业的重要组成部分,推动着国民经济的发展[1]。每个新一代集成电路的出现,总是以光刻所获得的线宽为主要技术标志,因而其关键部件、光刻胶、工艺参数等都成为近年来的研究热点[2]。随着科技水平的提高,市场需求的芯片集成化程度越来越高、体积越来越小、质量越来越轻。增加电路的密度,使得一片芯片上集成了越来越多的电子元器件,赋予了芯片更高的性能和价值[3]。芯片制造过程主要包括电路设计、晶圆制造和芯片封装测试,芯片在制造过程中离不开晶圆。在芯片的电路设计时需要考虑晶圆制造和芯片封装的工艺要求,晶圆制造的过程和设备有关,封装的功能主要是为芯片提供输入输出的电路通道,使芯片在印刷版电路中能够通过管脚和电路中的其他元器件连接起来,实现印刷版电路的调试和测量。为了降低成本,须扩大晶圆的利用率,势必要求生产线追求最大的利用率和产出[4]。减小芯片的尺寸,使晶圆上容纳更多的芯片版图是提高晶圆利用率的最直接的途径,功率器件、运算放大器芯片在保证最佳工作性能的同时体积小的贴片封装越来越受到市场欢迎。

芯片的封装不同,对芯片电路设计的要求也不同。芯片封装按照逐步复杂和高级的封装形式分类,目前封装外形可以分为SOT、SOP、QFN、QFP、BGA、FCQFN、FCBGA、WLCSP 等[5]。随着单板上元器件的布局密度不断地提高,芯片与芯片的间距以及芯片本身的引脚中心距也在进一步精细化,最具代表性的封装就是QFN封装[6]。在贴片式封装中的方形扁平无引脚封装(Quad Flat No-lead Package,QFN)因为管脚在底部完全没有任何外延引脚,芯片体积小,能够提高晶圆的利用率,降低芯片的制造成本,而且QFN 封装的底部可以设置散热焊盘,散热好,提供的散热性能恰好能够满足容易发热的运算放大器需求。

本文设计运算放大器7 层折叠型QFN 封装的16 μm×16 μm CMOS芯片版图,集成度高,提高晶圆的利用率和产出。

1 QFN封装

QFN封装需要经过磨片、划片、装片、焊线、包封、电镀、打印、切割的流程:①磨片是对晶圆片进行减薄,方便封装;②划片是对晶圆上独立功能的芯片切割分离;③装片是把分离的芯片从晶圆上取出来,放到金属框架载体上,通过银浆进行连接;④焊线是使用自动焊接设备把芯片上的引脚连线端与框架上的管脚连接在一起;⑤包封是用自动注塑设备,通过高压注塑的方式,把焊线好的芯片和金属载体用环氧树脂包裹并且固化,形成物理保护层;⑥电镀是在金属框架材质上镀锡,形成保护层,防止裸铜氧化;⑦打印是在环氧树脂表面打印产品型号、批次和标识;⑧切割是把芯片从条状金属框架载体上分割开,采用机械切割的方式,尽量减少切割的毛刺。完成以上步骤后的QFN封装芯片底部如图1 所示[7]。芯片周边导电引脚电极均位于器件封装底部,且封装底部中央位置有一个大面积裸露焊盘用来散热,围绕大焊盘的封装外围两边有实现电气连接的导电焊盘[8-9]。由于没有引脚,这种方形扁平封装的芯片占用的面积小,芯片的高度比较低,体积小,质量轻。

图1 QFN封装的芯片底部

QFN封装的芯片内部引脚连线端和外部引线框架焊盘之间的路径可以设计得足够短,电路分布电阻很低,可以降低引脚间的自感应系数[10],具备非常卓越的电性能。在高密度电路板中广泛使用,深受欢迎。由于其非常低的阻抗和自感,可满足高速或微波电路的使用[11]。在运算放大器芯片工作时,常常因为发热影响芯片的功能,但是QFN封装的芯片底部一般都有一大块焊盘作为散热块,底部焊盘直接释放热量,具有优质的散热能力,因此QFN封装特别适合大功率或电源类的控制芯片,随着行业对其可靠性机理的认知不断深入,现在已经逐渐地被应用到工业类和医疗类电子产品中[12]。特别适合在对质量、尺寸和性能都有苛刻要求的应用环境中使用QFN 封装的芯片[13]。QFN

封装的芯片在电路板上的装配可以通过电路板焊盘上涂刷焊锡膏,通过回流焊形成焊点和QFN封装芯片的焊盘连接起来。

2 电路设计

2.1 设计原理

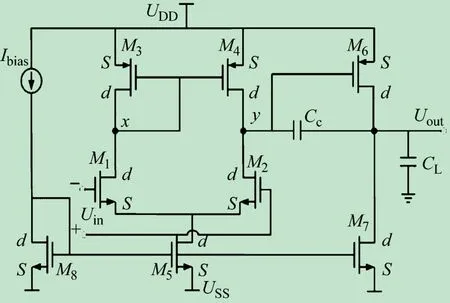

图2 CMOS运算放大器的电路图

由于CMOS场效应管的低输出功率和低栅氧击穿电压[14],难以实现大功率输出,为解决这个问题,在QFN封装运算放大器的电路设计中,采用2 级放大的电路实现运算放大器的功能,设计QFN封装运算放大器的原理图如图2 所示。图2 中CMOS 运算放大器主要由3 部分组成:Ibias电流源与M8组成直流偏置级,为后面两级放大电路提供直流偏置点;M1~M4与M5组成输入级差分放大电路,M5在直流偏置级的作用下工作在饱和区,相当于恒流源,M3与M4工作在饱和区,等同于偏置电流源,当M2的栅源极电压更大时,一开始M2的UDS与M1的UDS相等,随M2的UGS增大,流过M2的IDS随之增大,由于M4与M2处于串连关系,使得M4的UDS变大,M2的UDS变小,从而实现差分输出,即M1与M2将差分电压转化为差分电流,M3与M4将差分电流转换为差分电压;M6、M7与Ce、CL组成输出级放大电路,M7受直流偏置级的影响相当于恒流源,当输入级差分输出为高电平时,M6截止,输出电压为USS,当输入级差分输出为低电平时,M6导通,差分输出为UDD,从而实现运放的功能,Ce为M6的启动提供偏置电压,CL进行密勒补偿。

2.2 版图设计

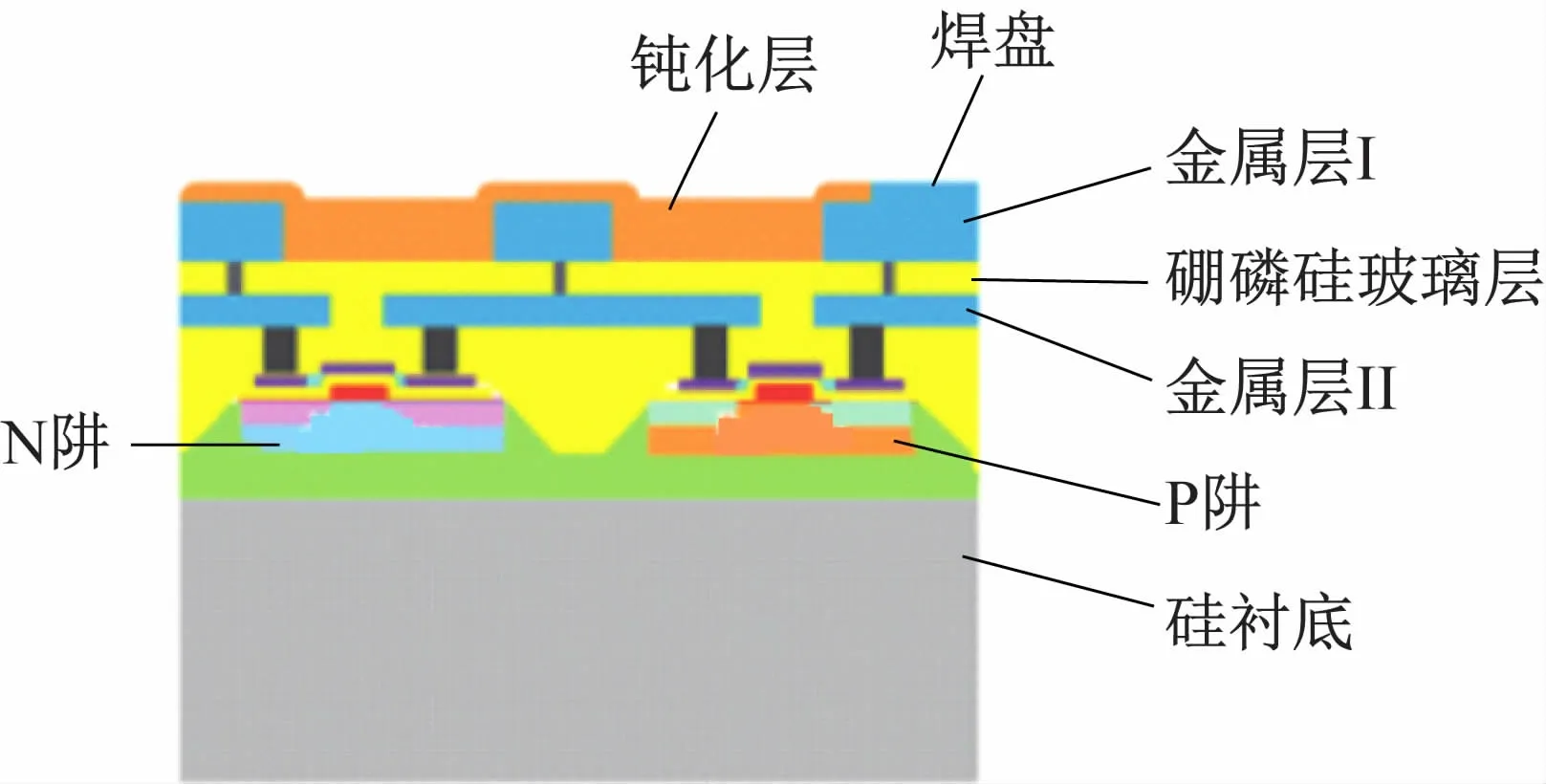

CMOS工艺具有集成度高、成本低、工艺成熟、可靠性高、功耗低等优点,并且易于与数字电路集成[15],CMOS工艺的芯片结构如图3 所示[16]。

图3 CMOS工艺芯片结构

图3中显示了CMOS 工艺的芯片结构,芯片结构的制作过程有12 个步骤:①准备衬底,采用热氧化法进行初始氧化,可将衬底和高纯度氧气、氢气暴露在高温的氧化炉中,形成初始氧化层;②光刻和刻蚀,用酸溶液去除所有的光刻胶,使用离子注入的方式形成N阱或者P阱;③依次生长SiO2、沉积Si3N4、涂敷光刻胶,露出场区形成鸟嘴,除去Si3N4和SiO2、露出有源区;④用化学气相淀积氮化硅,使用氢氟酸去除所有的氧化层并使用化学气相沉积将氧化层和多晶硅沉积通过光刻形成栅极,除去NMOS 和PMOS 栅极区域的氧化层和多晶硅外的其余部分,形成多晶硅栅;⑤运用化学气相淀积工艺生长介质膜SiO2;⑥进行涂胶、刻蚀,水平表面的Si3N4 薄层被刻蚀,留下隔离墙,精确的保证源区和漏区的离子注入;⑦接触孔形成工艺,目的是在所有硅的有源区形成金属接触;⑧形成可以提供互连的金属端子,在电解质上做1 层屏障,除去SiO2,重新沉淀金属层;⑨进行涂胶、刻蚀,形成金属互联,需要时还进行沉积钝化层;⑩进行涂胶、刻蚀,形成金属过孔;○1 完成抛光;○12 蒸发厚金属、涂胶光刻,做金属掩膜。在图3 中CMOS 芯片是将NMOS器件和PMOS 器件同时制作在1 个硅衬底上,CMOS芯片是多层布线,层间采用金属通孔互连[16]。

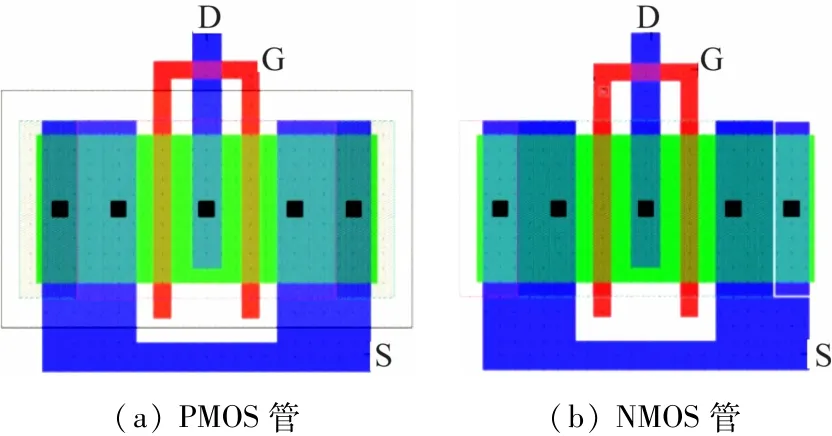

设计时需要考虑版图布局和MOS管的端口连接,达到体积小、集成度高、电路分布符合QFN 封装的要求,分成2 个步骤设计。第一是设计PMOS 管和NMOS管。为了得到更小的CBD、更小的芯片面积、更好的集成度和更好的导通区分布均匀度,设计了如图4所示折叠型MOS 管的版图。在图4 中的版图层包括左边PMOS管和右边NMOS管的折叠式版图。第二是设计运算放大器的版图。由于M3、M4、M6的源极均连接在UDD,所以将3 个PMOS 并排连接在一起,对于M1与M2,M5、M7与M8同理。由于未经过精确计算,无法得出密勒补偿电容的具体大小,所以将其置于外边沿,若确定其具体大小,可根据具体情况进行调整。为了对直流工作点进行调整,Ibias采用外部接入的方式,如图5 所示。

图4 折叠形MOS管版图

图5 运算放大器的版图

在图5 中,运算放大器的电路第1 级运放实现高增益,第2 级运放增加输出幅度,在第1 级和第2 级之间加入密勒电容补偿相位裕度。其中电容的设计可以是2 个金属层、2 个多晶硅层,或者1 个多晶硅和1 个金属层的版图设计。构成电流镜的M5、M7、M8也应在版图设计时尽可能靠近,避免由于工艺原因带来的性质差异,保证两级放大电路有相同的增益,绘制的版层包括N阱、有源层、N 植入层、P 植入层、多晶硅层、接触层和金属层I,共7 层。按照QFN 封装的设计把引脚安排在4 周,缩短引线的长度,减小版图的尺寸,实现16 μm×16 μm的版图设计,体积小,集成度高,节省制造成本。

3 测试结果

集成电路需要经过长达2 ~3 个月CMOS 工艺流程时间才能制成成品,如果因为设计不合理造成成品不能正常工作,在时间和原材料上都是极大的浪费。所以设计好的版图进行CMOS 工艺的设计规则测试,可以避免由于短路、断路造成的电路失效和容差等问题造成功率器件集成电路成品的质量缺陷。

设计规则检查(Design Rule Check,DRC)的内容由版图涉及到的版图层决定,设计规则包括走线最小宽度、同一版层的最小间距、不同版层的最小距离、版层的最小面积、版图分布的最小密度等等,没有用到的版层可以不在DRC 检查的项目中。CMOS 运算放大器的DRC项目如图6 所示。

图6 设计规则检查的内容

在图6 中的设计规则是设计人员与工艺人员之间的协议,版图设计必须无条件服从的准则,图中的WIDTH是工艺极限的最小宽度,Spacing 是多边形的最小间距,Overlap 是多边形相互重叠的最小尺寸,density是最小密度,要求每层版的密度均衡,防止过重的版层塌陷、短路。按照CMOS 工艺制造的设计规则要求测试了图5 的运算放大器电路版图,检查结果如图7 所示。设计规则检查的结果是0 错误,设计的版图没有出现违反DRC的错误项。

图7 DRC结果

根据测试结果可以看出,这个运算放大器的电路和版图设计通过了DRC 检查,说明这个基于QFN 封装的7 层折叠型CMOS运算放大器符合芯片制造的工艺要求,电性能好,能够在芯片制造工艺过程和芯片实际工作中确保电路和版图的质量,可以在电子设备中实现QFN封装CMOS运算放大器的电气性能。

4 结 语

芯片制造过程从芯片的电路设计开始,到晶圆制造、封装测试,完成成品检查后才能出货、销售,芯片电路设计需要考虑晶圆制造和芯片封装的工艺要求,晶圆制造的过程和设备有关,封装主要是为芯片提供输入输出的电路通道,使芯片在印刷版电路中能够通过管脚和电路中的其他元器件连接起来,实现印刷版电路上的调试和测量。基于QFN 封装的CMOS 运算放大器的电路和版图设计为了提高晶圆的利用率和产出,利用QFN封装芯片体积小、质量轻的特点,设计两级放大的MOS 管电路实现大功率输出,设计折叠式MOS管的7 层版图在16 μm×16 μm的面积中实现运算放大器的功能,采用QFN封装增大散热面积保证运算放大器正常工作时能够及时散热,不仅有效提高晶圆利用率、提高芯片的产出,而且降低芯片生产成本,具有重要的工程实践意义。这种利用贴片封装设计芯片的技术解决芯片制造的实际工程问题、提高生产力的科学方法,对于我国现阶段和未来在芯片制造产业和供应链中的各个环节中实现逐步创新、提高自主生产能力、提高产品质量,具有重要的创新价值和示范意义。