一种基于DSP和FPGA的高速光纤总线通信控制技术

2022-07-29孙宇伟苗世亮徐巧童黄凯

孙宇伟 苗世亮 王 琰 徐巧童 黄凯

(北京精密机电控制设备研究所航天伺服驱动与传动技术实验室,北京 100076)

20世纪美国的电气协会制定了MIL-STD-1553B数字总线标准,该总线具有双向传输、高可靠性及实时传输的特点,广泛应用于航海、航空以及车载领域。但随着科技不断进步,目前的伺服控制驱动单元采用MIL-STD-1553B通信协议,在与上位机或者控制单元的交互过程中只能传输有限的信息量,而且进行更高数据量交互时总线的负载率提高,导致通信可靠性下降,同时伺服响应实时性变差。随着超大功率机电伺服技术的发展,机电伺服单元的通道数、复杂性越来越高,产生对数据量越来越大;大功率机电伺服情况下对伺服系统的重量、通信可靠性也提出了更严格的要求。本文设计了一种基于DSP和FPGA的高速光纤总线通信伺服控制技术,可有效实现伺服驱动单元与控制单元两者在信息交互时传输速率快、可靠性高的设想。

1 电路方案设计

基于DSP和FPGA的高速光纤总线通信伺服控制技术,其中整个电路设计中包括以下几个部分:基于内部总线的收发单元、内部信号调理电路、二次电源变换电路、位移信号的采集电路和高速光纤总线模块电路。总线收发单元前端接DSP的EPWM模块,将EPWM模块所需的电平为3.3 V,带死区互补对称PWM控制率转换为电平为5 V的PWM信号,输出端连接伺服驱动器的IGBT/MOS管驱动芯片,实现功率模块的驱动。

本文是选用TI公司的现场可编程逻辑门阵列SMQ7K325芯片,研发了一种基于中央处理器(DSP)与现场可编程逻辑门阵列(FPGA)的Glink高速光纤总线伺服控制驱动单元,总线通信速率由1 Mbps提高至2.65 Gbps,可满足伺服单元与控制单元更大数据量交互与实时性的要求。同时高速光纤总线与传统的MIL-STD-1553B方式相比,通信介质由电缆变为光纤,减轻了电缆重量;传输信号由电信号变为光信号,在大功率机电伺服系统中避免了电磁干扰的影响,提高了通信可靠性。

1.1 DSP及外围电路

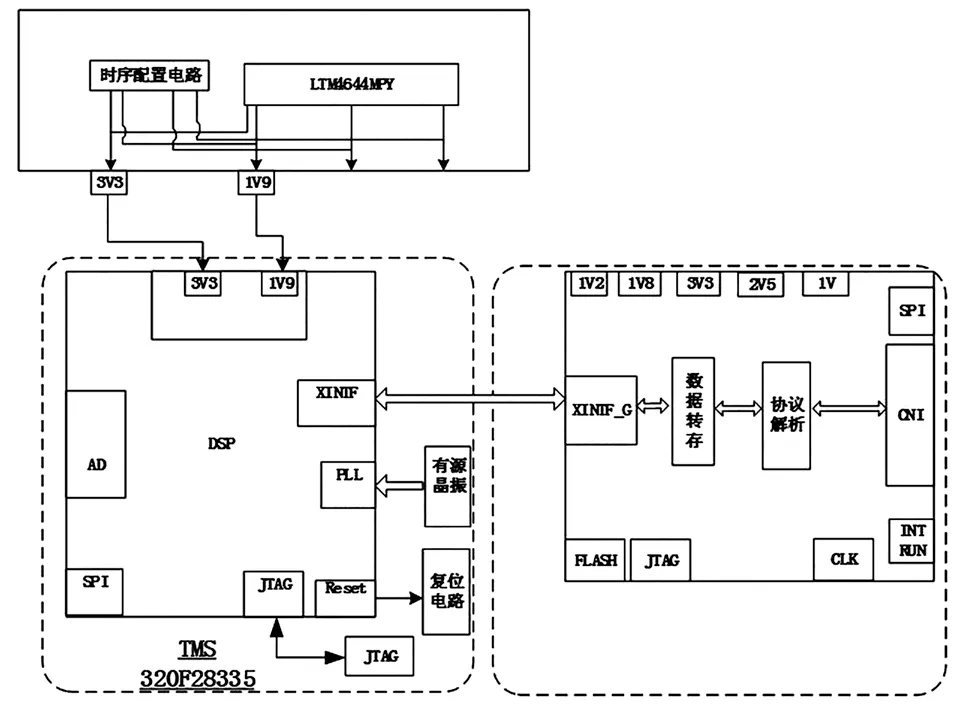

本文设计的高速伺服控制驱动单元由DSP单元、FPGA单元、高速光纤协议处理单元、二次电源变换单元、信号处理单元等组成。如图1所示,中央处理器(CPU)DSP为TI公司的新一代28335芯片,DSP芯片作为信号处理单元,包括了与FPGA芯片之间的通信,用来换算其采集特性;在中央处理器DSP 28335芯片的上方为二次电源变换电路,由2块电源模块4644芯片组成,为整个系统电路供电;在CPU的右边为FPGA芯片,用于高速信号的传输与处理,构成了中央处理器的桥梁;在FPGA的右边为光电转换连接器,用于与外界系统进行通信。

图1 DSP芯片通信结构图

整个控制器芯片DSP内部由主芯片TMS320F28335及其外部单元组成。其中,TMS320F28335内部由信号处理单元、EPWM模块、采集模块、SPI模块、JTAG模块、Reset模块、PLL模块、I/O模块、3V3/1V9模块子单元组成。其中,EPWM子单元模块作用于芯片根据内部设计的控制算法的PWM信号,该产生PWM信号输出端可以由接总线收发器的芯片进行传输。AD子单元模块输入端可以接收模拟量信号,将模拟量转化为数字量,用于计算整个系统内产生的实时模拟量信号。SPI子单元模块用于外部高速串口信号处理电路实现通信。JTAG模块外接JTAG电路,实现程序下载与在线调试。Reset子单元模块外接复位电路芯片,实现DSP内部的程序复位。DSP芯片上的PLL子单元模块外接有源晶振,用来实现DSP芯片的时钟输入信号。DSP芯片上的3V3/1V9子单元输入端接二次开关电源单元3V3、1V9的输入,实现为DSP芯片的内部供电。DSP芯片内部的信号处理单元包括高速总线收发单元、信号调理电路、位移信号调理电路,总线收发单元前端接DSP的EPWM模块。二次供电电源输入如图2所示,二次电源供电芯片为LTM4644,芯片为四路电压输出芯片,经过外围电路设计后,输出3.3V、1.9V、1.2V、1.8V电压,为DSP和其他外围电路供电。

图2 供电芯片示意图

1.2 FPGA及外围电路

FPGA单元由TI公司的FPGA芯片SMQ7K325及其外围电路组成。其中SMQ7K325也是由I/O模块、闪存(FLASH)模块、下载口(JTAG)模块、时钟(CLK)模块、接口(INT/RUN)模块、容器网络接口(CNI)模块、高速串行接口(SPI)模块、高速光纤总线单元以及供电电源等子单元组成。其中XINTF_G模块用于实现与DSP 28335单元的I/O模块进行接口通信,以实现伺服数据以及伺服状态信息在DSP芯片与FPGA芯片之间的数据高速交互。FPGA芯片单元上的FLASH模块子单元外接FLASH配置芯片的电路,用于实现FPGA芯片SMQ7K325的程序、数据掉电存储与上电加载。内部的JTAG子单元外接JTAG下载仿真器,用于实现FPGA芯片内程序的下载与调试。FPGA芯片的CLK子单元外接有源晶振芯片输入,作为FPGA芯片的时钟输入。CNI模块外接FPGA芯片的高速光纤总线单元的CNI接口,实现两者的数据通信,完成伺服数据与伺服状态信息在FPGA单元与高速光纤总线单元的数据交互。高速SPI子单元模块外接高速光纤总线单元的高速SPI接口,用于完成FPGA对光纤总线接口的配置。INT/RUN模块外接光纤总线接口的INT/RUN接口,分别用于接收光纤总线单元的正常工作、中断信号。

1.3 高速光纤总线实现

高速光纤总线协议处理单元由FPGA SMQ7K325芯片内部的总线模块区域所组成。FPGA芯片内部的高速光纤总线单元由高速SPI子单元模块、CNI子单模块、INT/RUN子单元模块、CHA高速串行信号模块、CHB高速串行信号模块以及供电的电源子单元模块组成。FPGA SMQ7K325芯片内的高速光纤总线单元用于实现收发CHA高速串行信号、CHB高速串行信号与DSP芯片内CNI协议信号的相互之间转换,完成伺服单元与伺服状态信息在高速光纤与内部ONU模块之间的信息传输。CNI子单元模块用于提供外部接口,外接FPGA芯片单元CNI子模块,完成伺服单元与伺服状态信息在FPGA芯片内的闪存信息模块、I/O模块传来的信息与FPGA芯片自身内部的高速光纤总线单元之间的信息传输。高速SPI子单元模块用于接收FPGA单元SPI模块发出的芯片配置信息。FPGA芯片的INT/RUN子单元模块将上行的DSP发出的TFC1553的运行状态信息、中断信息输出至FPGA的INT/RUN接口模块,实现与外部产品的高速通信。FPGA芯片内的电源单元用于接收二次变换电源单元提供的1V、1V35、2V5、3V3F输入,实现芯片的供电。如图3所示。

图3 信息交互流程图

要实现与外部的高速连接,则需要将内部芯片产生的电信号转化为光信号进行外部通信。因此,外部连接器内集成了光电转换电路,该电路由FPGA芯片上的电源进行供电,这样可以使整个系统实现高速差分电信号与光信号之间的互相转换。如图4所示。

图4 FPGA芯片通信结构图

2 软件实施设计

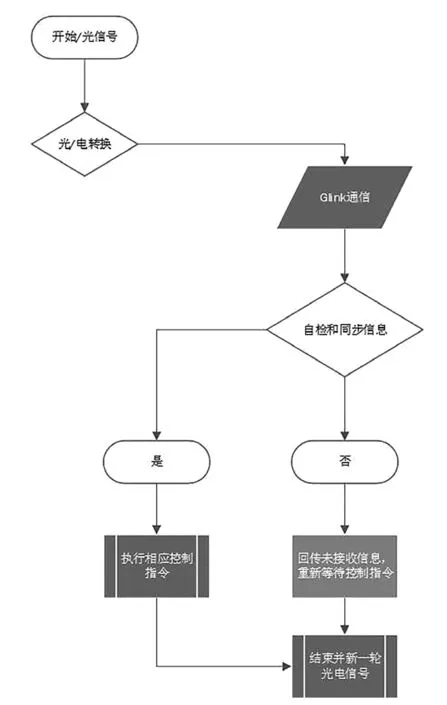

整个高速光纤通信流程如图5所示,控制指令由光信号通过高速光电转换插头转变为电信号,然后通过内部的FPGA芯片上的高速通信引脚进行信息交互,当控制器内部成功接收到信息并进行解析后,会通过高速光纤插头给控制系统发送接收成功信息,并通过解析控制指令进行相应的执行动作;DSP芯片的内部程序自检完成后,FPGA SMQ7K325芯片内的高速光纤总线单元用于与DSP芯片内的CNI协议信号的相互之间转换,完成伺服单元与伺服状态信息在光纤单元与内部ONU模块之间的信息传输;FPGA芯片内的INT/RUN子单元模块将上行的DSP发出的TFC1553的运行状态信息、中断信息输出至FPGA的INT/RUN接口模块,实现与外部产品的高速通信。如果控制信息未接收成功,回传给控制系统接收失败信息,并等待下一条消息。

图5 通信流程图

3 结论

本文设计给出的基于DSP和FPGA芯片的高速光纤总线通信控制技术,选用TI公司的SMQ7K325,研发了一种基于中央处理器(DSP)与现场可编程逻辑门阵列(FPGA)的高速光纤总线伺服控制驱动单元。其逻辑实现简单,传输速率快并且可扩展性强;相比于传统的1553B通信,总线通信速率由1 Mbps提高至2.65 Gbps,不仅满足了伺服单元与控制单元更大数据量交互与实时性的要求,同时新型高速光纤总线与传统的1553B方式相比,通信介质由电缆变为光纤,减轻了电缆重量;传输信号由电信号变为光信号,避免了电磁干扰的影响,提高了通信可靠性。