基于时间交替采样技术的1 GS/s、16 bit 数据采集系统研究

2022-07-21李海李斌康

李海 涛 ,李斌康 ,2,孙 彬 ,张 美 ,2,田 耕 ,2

(1.西北核技术研究所,陕西 西安 710024;2.强脉冲辐射环境模拟与效应国家重点实验室,陕西 西安 710024)

0 引言

随着半导体技术的快速进步,基于模数转换器(Analog to Digital Converter,ADC)的实时数据采样技术发展迅速。为了高精度地获取待采样信号波形,需要选择合适参数的数据采集系统。待采样信号带宽越高,需要的数据采集系统实时采样率就越高;待采样信号的幅值动态范围越大,需要的数据采集系统分辨率越高。

对数据采集系统的研究正在持续地蓬勃开展,2012年,中国科学技术大学的唐绍春,基于时间交替采样技术,研制10 GS/s、8 bit 数据采集系统[1];2013 年,中国科学院高能物理研究所的邹剑雄,研制4 GS/s、12 bit 数据采集系统[2];2019 年,中国科学技术大学的梁昊,研制双通道5 GS/s、10 bit 数据采集系统[3];2019 年,电子科技大学的周楠,研制5 GS/s、12 bit 数据采集系统[4];2019年,电子科技大学蒋俊、杨扩军等人,基于时间交替采样技术,研制20 GS/s、8 bit 数据采集系统[5-6];2019 年,中国工程物理研究院的吴军,研制6.4 GS/s、12 bit 数据采集系统,应用于脉冲辐射场诊断。

国内外也有很多数据采集产品,如普源精电科技公司(RIGOL)基于自研的凤凰座(Phoenix)示波器ASIC 芯片组研制的DS8000 示波器,性能达到10 GS/s、8 bit。美国Tektronix 公司研制的高分辨率示波器如MSO58LP,性能达到3.125 GS/s、12 bit;美国Teledyne 公司推出的高分辨率示波器如HDO8108A,性能达到2.5 GS/s、12 bit,还有数据采集卡产品如ADQ7,性能达到10 GS/s、14 bit;美国Gage 公司研制的数据采集卡如Razormax,指标为1 GS/s、16 bit,TB3-EON 的指标为6 GS/s、12 bit;美国Spectrum公司的数据采集卡如M4x.2234-x4,指标为5 GS/s、8 bit;美国Pico technology 公司的数据采集卡如PicoScope6407,指标为5 GS/s、8 bit;瑞士PSI 研发的数据采集卡如SIS3305,指标为5 GS/s、10 bit 等[7]。

前述的研究成果、产品,关注的重点大多在实时采样率上,以提高数据采集系统的时间测量精度为目的,对超快前沿(高带宽)的信号波形,用高采样率获得足够的精细时间信息。前述示波器/数据采集卡的垂直分辨率为8 bit、12 bit,对应动态范围有限,约100 倍、700 倍。在幅度归一化时,可分辨1/700 满量程电压幅值。一些应用场景中,待采样信号的动态范围高于1 000 倍,为了既获取信号整体波形,又获取信号波形细节,一般通过信道量程搭接等操作,实现对待采样信号的高精度测量。为提高信号测量精度,相邻信道量程必须有较大的重叠部分,这会降低信道的有效动态范围;此外,各信道的时间误差不同、幅值误差不同,同样会降低测量精度。

本文主要研究高分辨率的数据采集系统,针对大动态范围的待采样信号,用高分辨率数据采集系统获取高精度的信号幅度信息。研制采样率为1 GS/s、分辨率为16 bit 的数据采集系统,采用一个信道测量一个待采样信号,即消除了量程搭接引入的误差影响,又节约了信道,实现对大动态范围待采样信号的高精度幅度信息获取。在功能测试过程中,发现采样数据的振荡问题,基于时间交替采样技术,提出在线校准加离线校准的方案,解决采样数据的振荡问题,有效扩展系统的有效动态范围。

1 时间交替采样技术

时间交替采样技术也称为并行时间交替采样技术,基本原理是待采样信号传输到M 个ADC 通道,各ADC通道的采样时钟(频率相同)保持固定的相位差进行采样,最后把M 个ADC 通道的采样数据组合起来,等效构成一个ADC 的采样数据。时间交替采样技术使等效实时采样率提高到单个ADC 通道采样率的M 倍,且分辨率保持不变,是实现高速高分辨率ADC 的有效技术路线之一[1]。

时间交替采样技术可以在PCB 上实现,也可以在芯片内部实现,目前很多的高采样率、高分辨率ADC 芯片采用片上时间交替采样技术实现,例如ADS54J60 芯片,采用4 个250 MS/s、16 bit 的pipeline ADC 通道,达到1 GS/s、16 bit 的性能[8]。如图1 所示,对比分析两种典型ADC 的基线噪声频谱,一款为TI 公司的ADS5400 芯片,指标为1 GS/s、12 bit;另一款为TI 公司的ADS54J60,指标1 GS/s、16 bit。ADS5400 的平均噪底(高基线)约为-109.5 dB,ADS-54J60 的平均噪底(低基线)约为-121.7 dB,平均频谱噪底的大小和ADC 的分辨率正相关。ADS54J60 的频谱在250 MHz 频率点有一个凸起,对应其内部ADC 通道的实时采样频率。ADS5400 的频谱在200 MHz、400 MHz频率点有凸起,可以推断,其内部集成了5 片200 MS/s、12 bit 的ADC 通道,使用时间交替采样技术达到1 GS/s、12 bit 的性能。

图1 典型的基线噪声频率谱密度分布

理论上,如果各ADC 通道参数都一致,那么利用时间交替采样技术,可以完美地实现高采样率、高分辨率ADC[9]。在实际电路中,各ADC 通道的偏置、增益以及采样时钟相位都不一致,把偏置和增益的不一致引入的误差分别称为偏置误差(Offset error)和增益误差(Gain error);把采样时钟相位不一致导致的误差称为时间相位误差(Time-skew error);三种误差统称通道失配误差,严重影响时间交替采样ADC 的性能。

利用MATLAB 仿真工具,建立包含4 个ADC 通道时间交替采样ADC 的失配误差仿真模型(指标为1 GS/s、16 bit),输入模拟信号为标准正弦波,频率为30 MHz,ADC 相干采样,采样数据的频率谱密度如图2 所示,偏置误差 (三角形标识成份) 与输入信号无关,仅与ADC 通道实时采样率有关;增益误差和时间相位误差 (圆形标识成份) 与输入信号、ADC 通道采样率有关,且两种误差无法有效区分。

图2 1 GS/s、16 bit ADC 四通道时间交替采样系统失配误差的仿真模型

2 数据采集系统研制

采用“ADC+FPGA”的架构,研制定制化性能参数的高分辨率数据采集系统,硬件原理如图3 所示。待采样信号输入ADC 进行模拟数字转换,ADC 输出采样数据至FPGA;FPGA 对输入的采样数据进行接收、降速处理和缓存等操作;通过外部总线协议,读取FPGA 缓存的采样数据,做在线或离线的数据分析处理。

模拟信号调理链路的核心部分采用Ti 公司的电流型差分运算放大器——LMH6552,LMH6552 将待采样单端信号转换为待采样差分信号,带宽从直流到500 MHz,输入到ADC 中进行模拟数字转换。

ADC 芯片选择Ti 公司的ADS54J60,其内部包含4 个250 MS/s、16 bit 的pipeline架构的ADC通道,采用片上时间交替采样技术实现1 GS/s、16 bit 的性能参数,ADS54J60 的有效位约为11.5 bit(fin=10 MHz),理论上可以实现2 800 倍的动态范围[10];ADS54J60 输出数据率为5 Gbps/lane×8-lane,输出采样数据采用了JESD204B协议,JESD204B 协议采用CML 驱动器,具有数据传输率高、使用引脚少等优点。

FPGA 芯片选择Xilinx 公司Kintex-7 系列,芯片内部具有集成16 通道GTX 收发专用硬核[11],单通道GTX 可实现12.5 Gb/s 的高速串行数据双向收发功能,通过配置JESD204B 协议链路上的Tx、Rx 和时钟等链路连接参数[12],建立具有确定性延迟的JESD204B 协议链路连接,采用8 个GTX 通道接收ADC 输出的40 Gb/s 的JESD204B协议采样数据。

JESD204B 协议的时钟数据同步方式为自同步(Self-Synchronous)[13-15],自同步方式将时钟在数据流中进行编码传输,这种方式使得时钟和数据的延时路径相同,能保证最优的时序收敛。选择Ti 公司的LMK04828B芯片为ADS54J60 提供器件时钟(频率为1 GHz)、系统参考时钟(频率为3.960 25 MHz),为FPGA 提供全局时钟(频率为125 MHz)、参考时钟(频率为125 MHz)、系统参考时钟(频率为3.960 25 MHz)等[16-19],如图3 所示,整个系统的时钟同源,所有时钟的相位差保持稳定,有利于建立JESD204B 协议链路和实现确定性延迟。

图3 高分辨率数据采集系统硬件原理

3 信号源测试

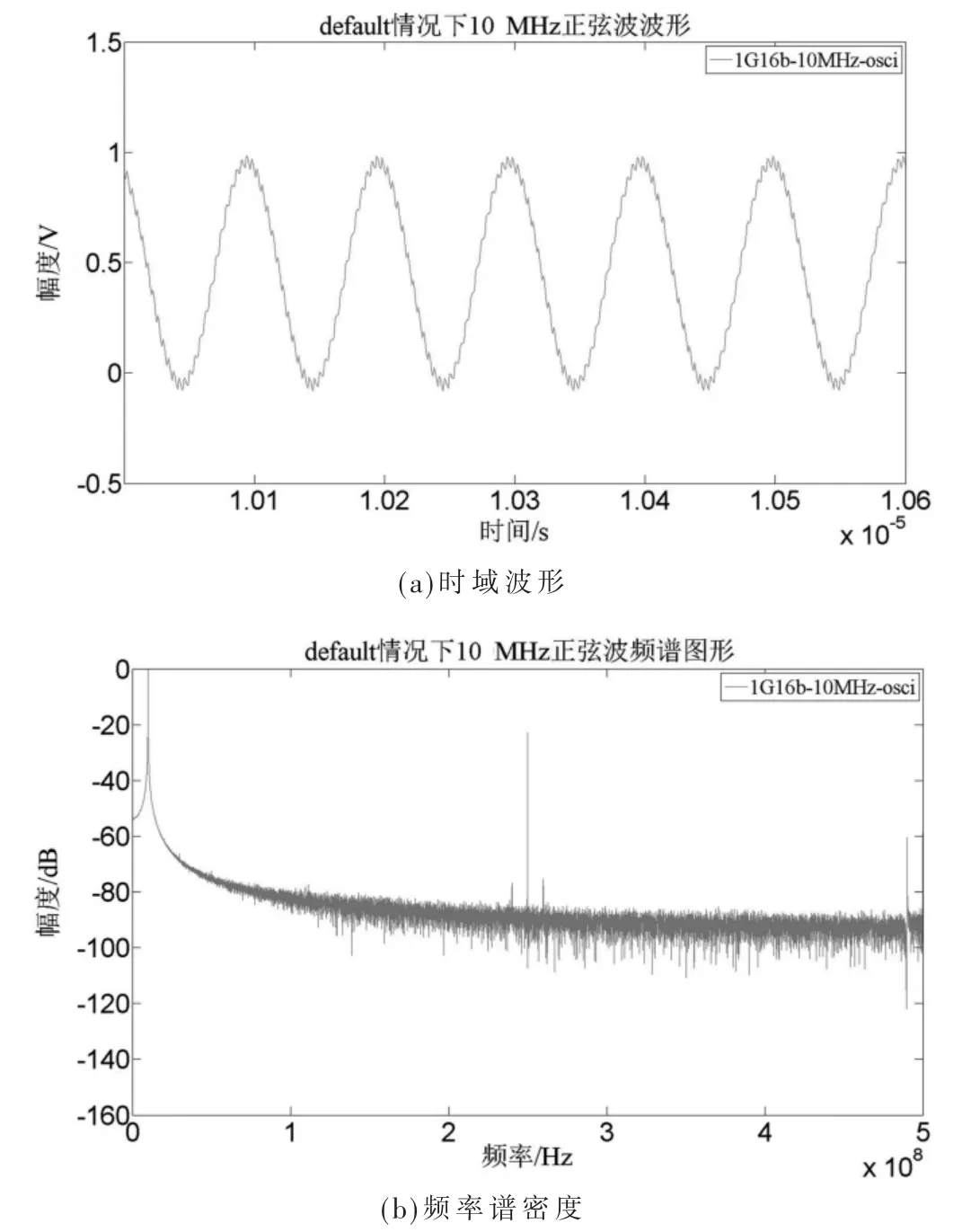

对研制的1 GS/s、16 bit 的高分辨率数据采集系统开展功能测试,使用DG5251 作为标准信号源,输出10 MHz正弦波进入ADC 模拟输入端,测量得到采样数据时域波形和频谱如图4(a)、图4(b)所示,250 MHz 频率点对应的毛刺为ADC 通道实时采样频率,230 MHz、240 MHz 对应的是二阶互调失真(IMD2),对比图1 的基线频谱,图4中二阶互调失真比较明显;与图2 相比,由于各种原因(主要是输入正弦波频率和ADC 采样频率的选择)没有满足相干采样的要求,在数据分析时也没有加窗函数处理[10,20],因此频谱泄露比较大,形成比较大的喇叭口。

图4 采集的正常10 MHz 正弦波波形

测试中发现:设置ADC 工作在实时校正误差模式(默认工作模式),当输入模拟信号中含有较大低频能量(尤其是直流分量)时,输出的采样数据发生振荡问题。调整信号源输出带有直流偏置(+500 mV) 的10 MHz 标准正弦波,输入研制的数据采集系统,分析输出采样数据的频谱如图5 所示,输出采样数据处于稳定振荡过程,振荡周期为4 ns,对应4 个ADC 通道采样时钟周期。对比图4 正常的正弦波频谱图,结合图2 的仿真结果,可以看到,误差主要集中在偏置误差频率点上(250 MHz),ADC 无法实时校正偏置误差,导致了采样数据的振荡问题。

图5 采集的10 MHz 振荡的正弦波波形

为解决ADC 芯片无法实时校正偏置误差而导致的采样数据振荡问题,手册给出了一种frozen 校正方法的解决方案[8,21]。该方案要求在ADC 芯片上电正常工作后,首先保证ADC 的输入端50 Ω 接地,进行实时校正,获得的实时校正值存储到ADC 的片上寄存器;之后关闭实时校正,采用存储值进行frozen 校正。使用frozen 校正偏置误差后,获取采样数据的时域波形和频谱如图6所示,frozen 校正的正弦波(上方波形)在时域上和正常波形(下方波形)并无明显区别,在频谱上区别明显,图6(b)中,正常波形频谱基线(最下方基线)比frozen 校正波形的频谱基线(最上方基线)平均值低约15 dB。对比图4、图5,采用frozen 校正方法,虽然部分消除偏置误差,却额外引入了增益误差和时间相位误差,并且整体抬高了采样数据频谱的平均噪声基底约15 dB,极大降低了数据采集系统的有效动态范围。这是因为frozen 校正采用固定值校正偏置误差,而偏置误差是动态变化的,并不是实时动态校正偏置误差,这样就无法有效校正偏置误差。

图6 采用frozen 方法校正误差后得到的典型结果

4 失配误差校正

测试发现,frozen 校正无法实时校正ADC 采样数据中的偏置误差,导致其出现了振荡问题,并且降低了系统的有效动态范围。为解决ADC 输出采样数据的振荡问题,确保数据采集系统的动态范围,需要研究新的偏置误差校正算法。研究振荡过程、振荡幅值、恢复过程等和输入模拟信号的关系,确定校正方法,给出对比测试结果。

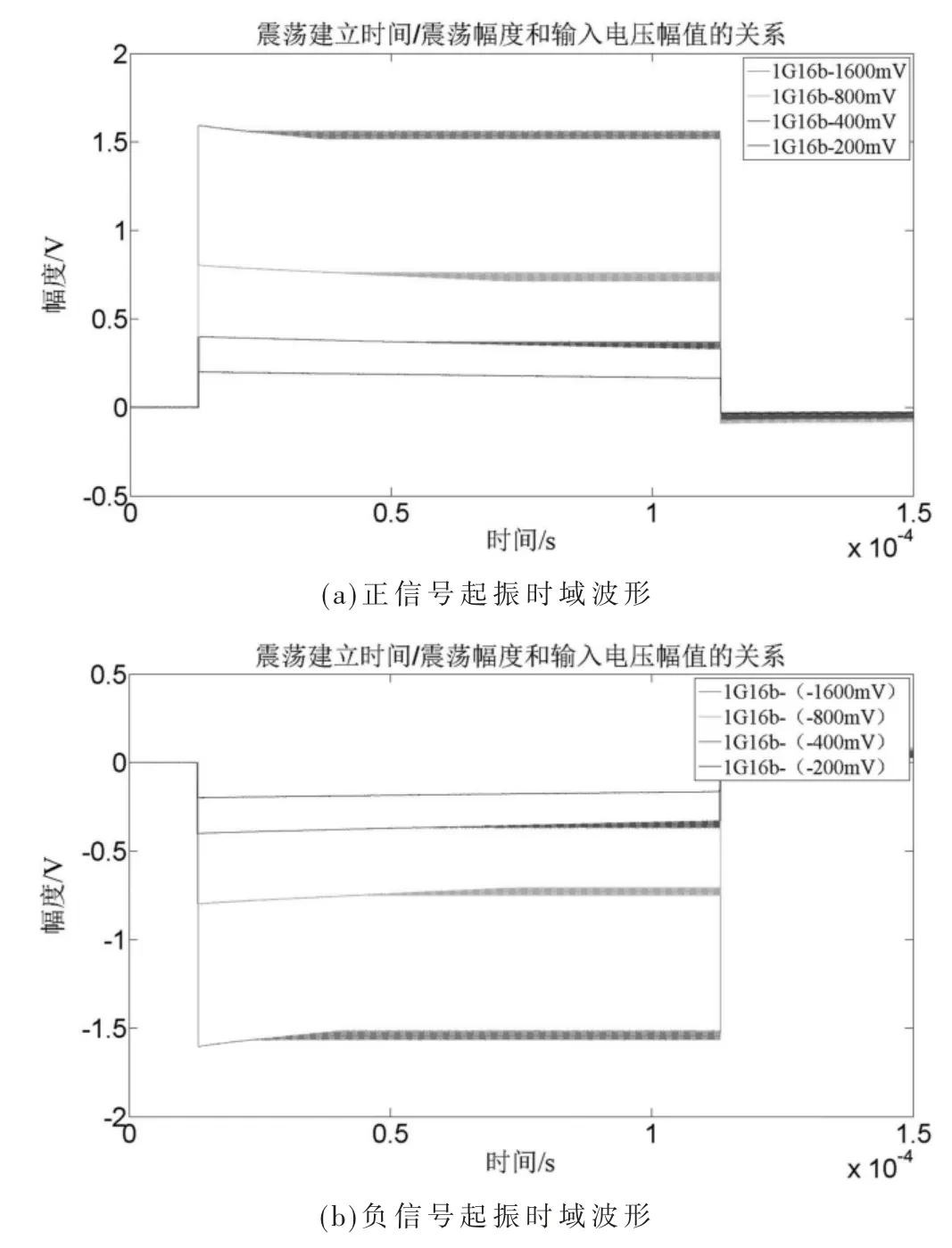

ADC 工作在实时校正误差模式,分析采样数据振荡过程和输入模拟信号电压幅值的关系。采用100 μs 长脉冲信号测试,脉冲从0 电平跳变至正负高电平,如图7所示,振荡经历了起振、建立、稳定、恢复等过程。分析得到:(1)起振时间、振荡稳定时间和输入电压幅值相关,近似成平方关系;(2)振荡稳定后的振荡幅度范围和输入电压幅值无关。根据公式E=U2×t/R,R 为50 Ω;定义Eosci为起振能量阈值,tosci为起振时间,是波形从输入电压幅值跳变时刻到振荡开始时刻的时间;定义Estable为振荡稳定能量阈值,tstable为振荡稳定时间,是波形起振时刻到振荡稳定时刻的时间,(tosci+tstable)为波形从输入电压幅值跳变到稳定振荡的时间。当输入偏置电压超过一定幅值后,ADC 无法实时有效校正偏置误差,会在芯片内部积累能量,当积累的能量低于Eosci时,输出的采样数据对应幅值会缓慢下降,但不振荡;当积累的能量超过Eosci后,输出的采样数据就会逐步起振,且振荡的电压幅值逐渐增大;如果能量继续积累到Estable后,振荡过程就会保持稳定,稳定振荡的电压幅值和输入电压幅值无关,稳定振荡电压幅值范围对应的ADC 编码范围约为±1 024,和手册中给出的值符合[21]。

图7 振荡过程和输入电压幅值的关系

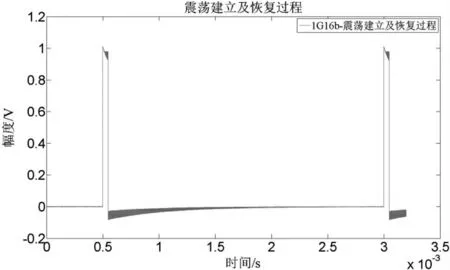

振荡过程中,如果外部的能量来源中断,即偏置误差归零,那么ADC 会从振荡过程进入到恢复正常过程,这种情况如图8 所示。振荡建立的过程是一个快过程,时间较短;与之相对,恢复正常过程是一个长过程,恢复时间约2 ms。

图8 振荡时间、恢复时间和输入电压幅值的关系

综上,采样数据振荡建立的过程是一个能量积累的过程,针对DC 耦合输入情况,只要ADC 的输入模拟信号中含有的直流或者低频分量的幅值,超过了ADC 可以实时校正的电压范围,就会在ADC 的模拟输入端积累能量,一旦超过能量阈值,输出的采样数据波形就会振荡,稳定振荡的电压范围和输入模拟信号幅值无关。ADC 无论是处于起振过程、振荡稳定过程,还是恢复正常过程,振荡周期均为4 ns,对应4 个ADC 通道的实时采样周期。

基于以上结论,设置ADC 为实时校正偏置误差工作模式,使其工作在稳定振荡过程,确保振荡幅值稳定。对于ADC 无法实时校正的偏置误差部分,采用求平均做减法的方法,偏置误差校正前后的典型时域波形和频谱如图9 所示,对比正常采样数据的时域波形和频谱,偏置误差被基本消除,偏置误差校正后的噪声基底水平和正常波形的噪声基底水平类似。

图9 离线校正偏置误差后的典型结果

结合使用ADC 芯片实时在线校正加离线校正的方法,有效解决了偏置误差导致的采样数据振荡问题。图10(a)给出了研制的1 GS/s、16 bit 数据采集系统单信道多次测量采集到的脉冲信号时域波形,上升时间约为3 ns,脉宽为20 ns,16 bit 原型系统的测量结果离散较小,基线噪声峰峰值约为2.3 mV。图10(b)给出1 GS/s、8 bit 示波器信道多次测量采集到的脉冲信号时域波形,基线噪声峰峰值约为55 mV。在相同输入电压幅值情况下,1 GS/s 16 bit 原型系统的动态范围约是8 bit 示波器的24 倍。如前述,一般8 bit 示波器的动态范围约100 倍,因此16 bit 系统的动态范围超过2 000 倍,可以实现对大动态范围脉冲信号的实时采集功能。在采样数据波形的离散型方面,不论在基线处,还是波形幅值快速跳变处,16 bit 测量的采样数据波形的离散较小。

图10 16 bit 系统和8 bit 示波器多次测量脉冲信号典型结果

5 结论

基于时间交替采样技术,研制1 GS/s、16 bit 高速高分辨率数据采集系统。测试中发现ADC 输出采样数据的振荡问题,采用推荐的frozen 校正方法解决振荡问题,效果不理想。通过对采样数据的频谱分析,确认偏置误差无法实时校正是采样数据振荡问题产生的原因。研究时间交替采样技术,确定ADC 输出采样数据振荡和输入待采样信号电压幅值的关系,认为振荡过程是一个能量积累过程,稳定振荡波形幅值和输入信号幅值无关。设置ADC 工作在实时校正误差模式,使其工作在稳定振荡过程,结合采用离线算法校正偏置误差。对比误差校正前后采样数据的典型时域波形及其对应的频谱分布,可以发现经过误差校正消除了偏置误差,有效解决了采样数据的振荡问题。使用研制的大动态范围数据采集系统采集单信道采集脉冲信号波形,并与8 bit 示波器信道量程搭接采集到的待采样信号波形进行对比,研制的系统可以实现对大动态范围脉冲信号的高精度实时采集功能。