C-R 型多通道10 bit SAR-ADC 设计

2022-07-21邓玉清牛洪军

邓玉清 ,牛洪军

(1.中科芯集成电路有限公司,江苏 无锡 214035;2.无锡翼盟电子科技有限公司,江苏 无锡 214035)

0 引言

Flash A/D 转换器满足高速高精度,可以实现GS/s的水平,主要用于军工设计,例如雷达、卫星通信等[1]。ΣΔA/D 转换器满足低速高精度,主要用于音频领域。流水线A/D 转换器满足高速高精度,可以实现500 MS/s 水平,主要应用于高速仪表、视频领域、网络系统。积分型A/D 转换器满足中等速度中等精度,主要用于低速仪表。逐次逼近ADC(SAR ADC)满足中等速度中等精度,并且具有功耗低、面积小、复杂度低、易于集成SoC 等优势,被广泛应用在数据采集、工业控制[1-2]。

提高转换速率可以通过增加比较器个数、采用异步控制等,但往往伴随功耗和面积的更多开销。随着位数增加,传统结构的DAC 面积呈指数增加,可以改变分段结构来降低面积。为了降低失调,许多文章提到采用全差分结构配合混合切换[3],然而相比单端结构会消耗更大的面积和功耗。在降低功耗上,有人通过采用动态比较器,但动态比较器带来更大的失调,需要更为复杂的修调算法补偿[4]。

综上,本文采用CR 分级、温度计码、自举开关、前置放大技术克服如上提到的缺点。

1 系统设计

1.1 SAR 系统结构

本设计的结构如图1 所示,包括通道选择、采样、CR-DAC、静态比较器、SAR 控制逻辑。在传统结构基础上加入通道选择控制,实现对任一通道输入的A/D 转换。针对传统结构中面积大问题,采用CR 分级合理选型,达到面积与性能的最优化[5-6]。

图1 SAR-ADC 功能框图

1.2 SAR 系统结构

当软硬件配置好后,ADC 按图2 时序工作。

图2 ADC 的工作时序图

复位信号Rst 释放后,当数字逻辑接收到Sos(Start of sample)的高脉冲后开始采样时序(>2T)。当数字逻辑接收到Sos 的下降沿则会触发SAR 逻辑,按照固定周期循环10T,每周期完成一次D/A 转换和比较工作。按照每次的比较值设置对应sar 的值。当完成最后一次比较之后Eoc(End of converse)变为高,与此同时,sar 的数值会读入reg,在数据口D<9:0>可获取。

在采样阶段,与Vin连接的开关全部闭合,输入对采样电容负极板充电,采样时正极板为共模电压Vcm,此时采样极板的电荷量为[7]:

在保持阶段,与Vin连接的开关全部断开并连接地,正极板与共模电压间的开关也断开,此时正极板的电荷量为:

在转换阶段,SAR 逻辑从MSB 开始逐位置位DAC的输入,使DAC 输出向共模点逼近。根据每次比较结果获得最终的ADC 输出,经过N 次比较后,最终的残余电荷为[8]:

2 电路级设计

2.1 DAC 设计

DAC 是SAR-ADC 中最重要的子模块,DAC 的线性会影响ADC 精度。DAC 主要有电压定标型、电荷定标型、混合型结构[6]。电阻分压型最大的优势是能保持良好的单调性,但随着位数增加芯片面积也大大增加。电荷定标型ADC 功耗一般比较小,并且不需要额外的采样保持电路,但是电容的精度和面积都是限制位数的因素[6]。电容-电阻(C-R)组合结构则可以兼具电压型与电阻型的优点,在降低芯片面积和功耗的同时可保证线性[7]。文献[5,7]针对“5+7”“6+6”以及“7+5”三种典型的C-R 组合结构进行了功耗仿真和比较,低5 位用电阻实现具有良好的单调性。

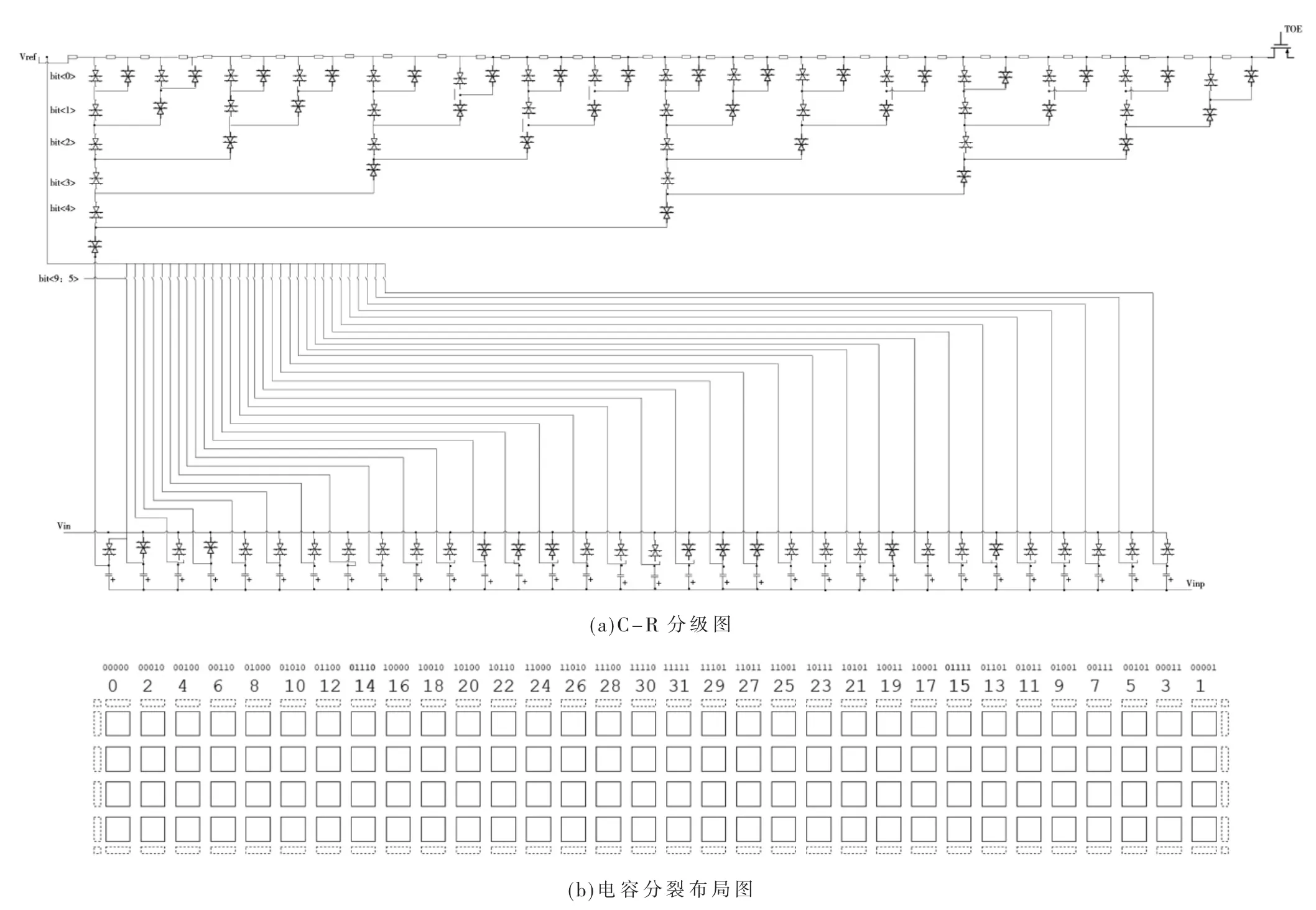

在以上研究背景下,本文采用“5+5”的分级结构实现DAC设计。图3(a)为CR 混合式结构DAC示意图。高5 位用电容满足高位的精度,低5位用电阻实现良好的单调性。高5 位只需要32Cu,而不分级的10 位ADC 则需要1 024Cu,可以大幅降低芯片面积。

二进制编码控制开关会存在开关大量切换的过程。而在开关切换过程中会引入时钟溃通和电荷注入效应。从文献[7]可获得DNL 贡献公式如下:

因此在高5 位的设计中,除了尽量采用大电容外,高5 位全部采用温度计码设计,从而进一步提升芯片的DNL。低5 位的电阻分压型采用二进制切换即可满足要求。图3(a)展示的是最终确定的DAC 结构,从上到下依次为电阻分压、温度计译码、电容阵列。

电容的匹配性布局设计如图3(b)所示。一个Cu在版图上分裂为4 个小电容。在温度计码递增/减时,电容数会按照图中标注次序以Y 轴对称交互选中/关断。

图3 DAC 结构

2.2 自举开关设计

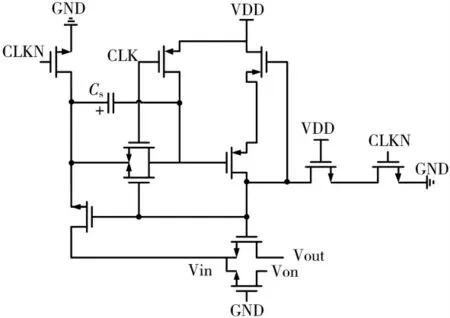

由于单管开关的输入信号摆幅会受到开关阈值的影响,大多都会采用CMOS 开关进行信号传输。但CMOS开关的导通电阻也很难保证恒定,会影响ADC 的非线性增益误差。因此在本设计中采样开关采用自举开关,电阻开关采用CMOS,置0/置1 开关采用NMOS/PMOS。

本设计中的自举开关如图4 所示。当CLKN 为高时,电源对采样电容Cs充电;当CLK 为高时,电路对输入电压采样,采样开关的栅源电压等于AVDD,与输入电压大小无关,如此则保证了很好的线性度。此外,在开关两端跨接了伪开关抵消部分电荷泄漏,采样开关的线性度更高[4]。

图4 自举采样开关

2.3 静态比较器的设计

动态比较器由时钟触发,速度快、静态功耗小,但具有失调电压大和回踢噪声大缺点[7],不经过修调算法的动态比较器只能达到6 位。因此本设计确立了静态比较器结构选型,结构如图5(a)所示。比较器由四级构成,前三级为前置放大,输出级为双转单输出。全差分的输入级天生具有消除共模误差的作用,大增益等效降低了输出级的失调误差影响。如图5(b)所示,静态比较器由两级构成,第一级为共源共栅,第二级为共源放大器。

图5 静态比较器

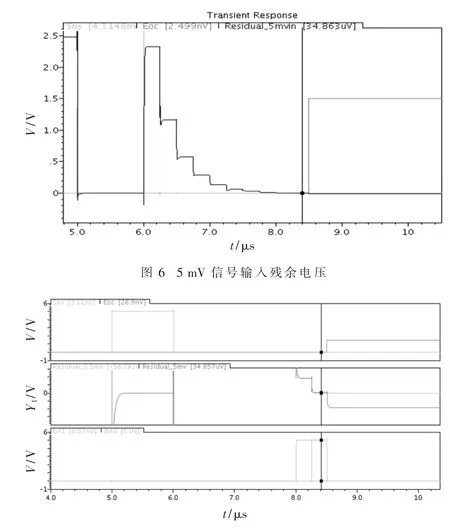

图6 和图7 为整体仿真中比较器输入端的残余电压。从图7 可知输入端0.1 mV 的差异就可造成比较器的翻转,完全满足系统的精度要求。

图7 对比5.1 mV 输入时的残余电压

3 仿真结果

整个ADC电路在0.13μm工艺上设计实现。用Spectre 进行了子模块仿真,并用hsim 完成ADC 的系统仿真。ADC 核心电路版图如图8 所示。版图的尺寸为580μm×290 μm。

图8 模数转换器的版图

ADC 的静态参数包括失调误差、增益误差、DNL、INL、综合误差。输入斜坡信号完成全量程仿真后,通过Analog expression 实现数字输出结果的模拟化,再与10 位ADC 的理想阶跃曲线取差即可获得ADC 的静态参数。仿真结果如图9 所示。可以看出DNL<+0.5/-0.5LSB,INL<+0.7/-0.7LSB。

图9 输入斜坡信号时的输出波形

ADC 的动态参数包括SNDR、ENOB 等。为获得动态参数,广泛的做法是输入正弦信号进行多周期仿真,然后对采样数值在MATLAB 中做FFT 分析。图10(a)为输入5 kHz 正弦信号,在采样率为200 kS/s 时的仿真图形。为简化ADC 的设计流程,本文采用hsim 仿真器做整体仿真,仿真结果可以直接用Verdi 来做FFT 分析。图10(b)为取样16 384 点,并且加Blackman 窗函数后的FFT 结果。从频谱可看出SNDR 达60 dB,ENOB 达到9.5。

图10 正弦波仿真

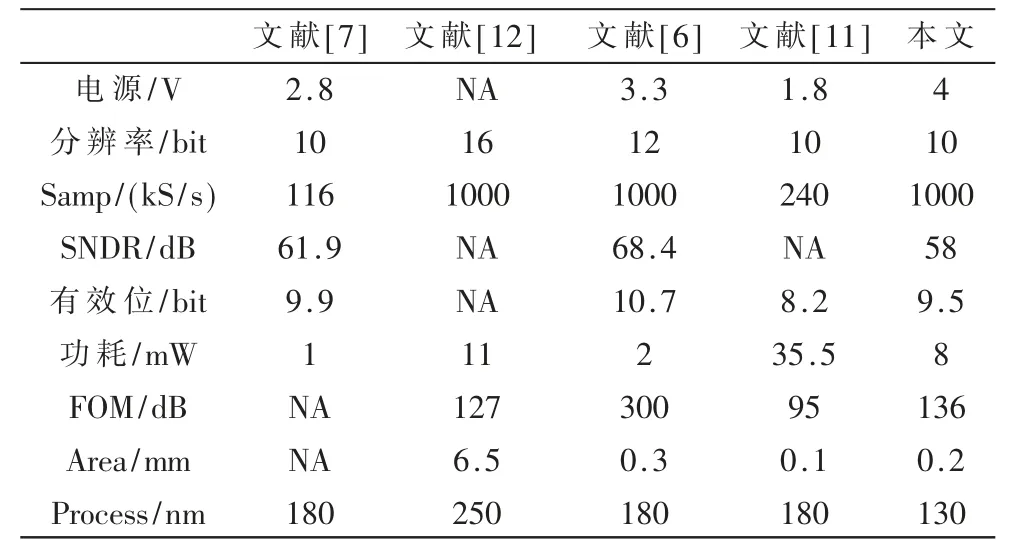

当输入50 kHz 正弦信号,在采样率为1 000 kS/s 时,SNDR=58 dB,详见表1。本文用品质因数FOM(Figure-Of-Merit)作为衡量ADC 综合性能的标准。

表1 是与近期相似领域论文的比较结果。从表中可见,本设计的综合指标较好,有较高的性价比。

表1 性能比较

4 结论

本文在0.13 μm 工艺中设计实现了一款10 位SARADC,通过C-R 结构、自举开关、温度计码控制、高精度比较器的设计有效减小芯片面积,提高了ADC 精度。在信号峰峰值4 V、信号频率为200 kHz、采样率为1 MS/s下后仿真得到SNDR 达58 dB,ENOB 达9.5 位。