Yolo 神经网络在集成电路焊盘布局规则检测上的应用研究*

2022-07-21林纯熙

林纯熙 ,粟 涛

(1.北京邮电大学 国际学院,北京 100001;2.中山大学 电子与信息工程学院,广东 广州 510006)

0 引言

从2015 年以来,产业界研发了多种神经网络处理器[1-2],并使用这些处理器制造了许多服务器,在多个城市大规模地部署了计算中心[3-5]。这些服务器具有强大的计算力。大量的个人携带的移动终端也嵌入了带神经网络处理器的芯片,形成一种随处可用的算力。如果这些算力也可以参与到集成电路的自动化设计中来,那会使设计工作变得更加方便。比如说,只需要下载相应的权值,就可以使用手机进行集成电路设计版图的检查,这对管理人员也是一种帮助。

神经网络在图像分析上获得了巨大的成功。这些成功的案例有:目标分类[6-8]、目标检测[9-12]、目标识别[13-14]。除了单目标分析,神经网络还可以进行多目标分析[15-16],比如在一张图中找到所有汽车[17]。然而当前成功的深度学习神经网络对于集成电路设计是否仍然有效,还有待研究。

集成电路设计分为前端和后端。后端的核心任务就是版图设计。版图设计分为绘制和检查两个环节。每次绘制完总要进行检查来判断绘制是否合规。芯片版图分为内核和IO 两部分。首先探索神经网络是否可以用于IO 焊盘摆放的合规性检查。

最近学术界在使用神经网络辅助集成电路设计上也开展了一些工作,主要有:采用ANN 技术辅助微波电路设计[18];利用人工神经网络设计、优化、模拟集成电路[19];利用神经网络进行数字电路的分层测试[20]等。

上述这些工作存在诸多问题,并且也没有针对IO布局进行的研究。检查IO 布局涉及目标的检测和识别,除了检测多个目标,还要分析目标之间关联,判断是否违规。此外还要对整个布局的态势做出分析。这种版图分析比人脸识别之类的分析要更加复杂,有可能带来一些对神经网络算法和应用的新认识。

综上所述,研究神经网络在IO 布局上的应用有实际用途,与已有的工作不重复,并且具有一定的学术价值。

1 焊盘布局

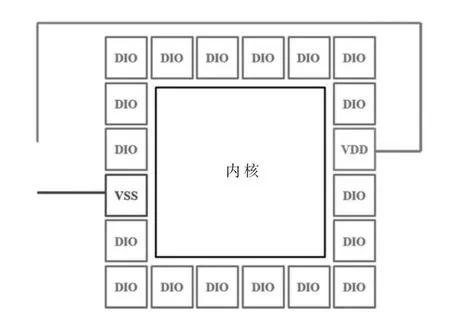

图1 给出了一种芯片版图,IO 焊盘围绕内核排布。在这个布局中,电源引脚VDD 和接地引脚VSS 的焊盘被放在相邻的位置。这种布局的好处是,在封装和电路板上VDD 和VSS 的互连线可以紧紧靠在一起,既减少了供电网络的寄生电感,又能降低电源互连线上的电磁辐射,因此是有利的。

图1 焊盘布局(有利)

图2 给出了一种不利的芯片版图。电源引脚VDD和接地引脚VSS 的焊盘分别被放在两边。这种布局的电源网络连线会出现一个较大的环路,降低电源网络的快速响应能力,并导致较大的电磁辐射。

图2 焊盘布局(不利)

如果芯片版图中缺少VDD 或VSS 引脚,那很可能是一种错误,也是不能通过检查的。根据以上分析,确定本文要实现的检查目标为:给定芯片版图,分析VDD 和VSS 的相对位置,(1)如果两者相邻,就报正确;(2)如果两者不相邻,就报错误;(3)如果缺少其中一种或全部,也报错误。下面将验证神经网络是否能够完成这样的检测。

2 检测算法

深度卷积神经网络的模型有很多,其中用于目标检测并进入实用的主要有Faster R-CNN、SSD 和Yolo[21]。本文采用Yolo 的v3 版本[22]进行版图检查。

Yolo v1 是Redmon 等人针对两阶段网络效率低、实时性差的问题提出的首个单阶段目标检测网络。即只需要对输入图像进行一次处理,即可同时得到目标位置和类别的优化网络,相比于其他几种目标检测算法,主要有目标检测速度快、背景错误少、泛化性能好等优点。

Yolo v3 在小目标的检测上表现出了比Yolo v1 更卓越的性能。同时,在目标框位置检测和物体定位方面也更精确、更稳定。在检测速度方面,Yolo v3 仅用1/3 的时间就可以达到与SSD 相当的精度。Yolo v3 在边界框大小的预测上采用与Yolo v2 相同的K 均值聚类算法,最终从预测出的三个初始尺寸不一的边界框中选出与真实值的IOU 最大的边界框来预测该目标。因此,在同尺寸的样本检测中,Yolo v3 生成的边界框大小几乎一致,并且更加接近于目标物的真实大小。Yolo v3 用bx、by、bw、bh 表示预测得到的边界框的中心坐标和尺寸。

综合考虑,选用Yolo v3 为本研究的目标检测算法。

3 实验部署

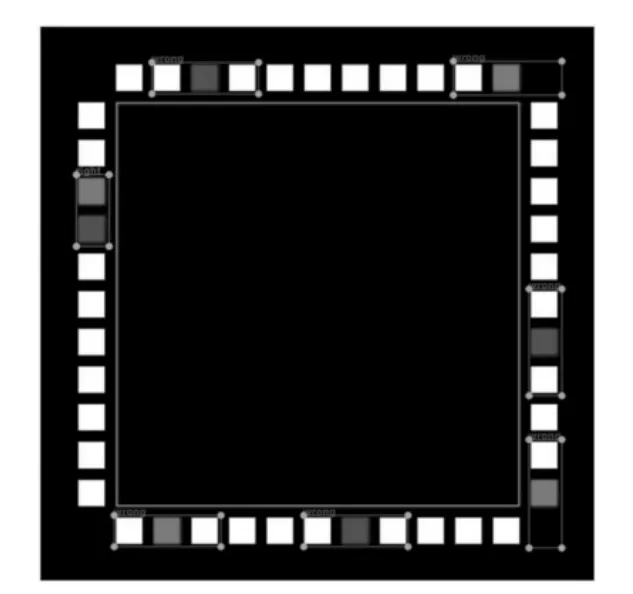

以44 个引脚的布局为实验用例,见图3。首先利用自编写的Python 脚本生成了100 张样本图片,随后运用LabelImg 对其进行了标签标记并生成数据集。用Python生成版图框架,而后生成四组数字0~10 的随机排布序列,并据数列确定VSS 和VDD 在每条边上的位置序号,随后生成样本图片。

图3 标记后的图形数据

将目标划分为两个大类:“right”和“wrong”。对于在同一条边上相邻的VDD 与VSS,将其框住并将标签命名为right;对于不符合排布规范的VDD 和VSS 焊盘,将其与左右相邻的普通焊盘或同极性焊盘一并框起并令标签名为“wrong”。

数据集制作完成后,利用Python 脚本将其按照90 :9 :1 的比例随机分成训练集、测试集和验证集三部分,同时利用脚本获取每个部分的文件名与地址。完成以上数据的收集后,将Yolo v3 文件中的默认类别数量与名称悉数改为本次实验中的相关参数。至此,第一次训练前的准备工作已全部完成。

调用训练器对训练集进行了训练。经过梯度下降算法的两百次迭代,生成最佳权重文件weight1.pt。然后调用版图检查器对权重进行测试。

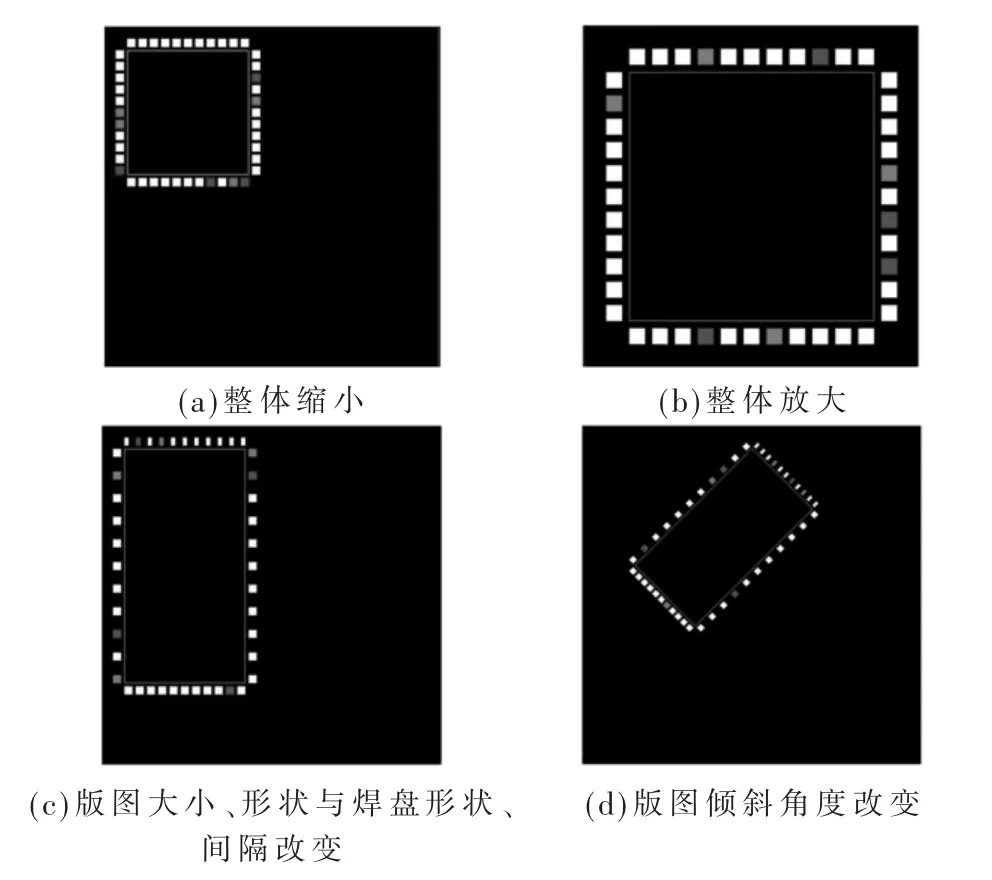

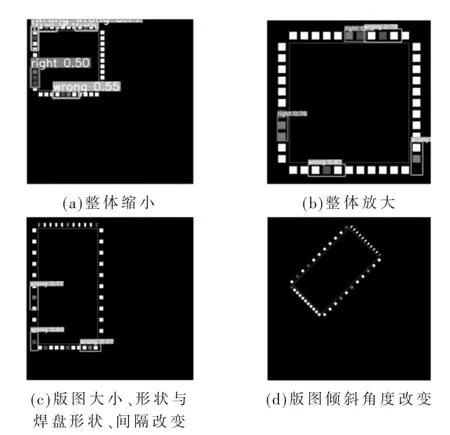

为了测试版图检查器的泛化能力,又制作了三组数据集。取消了每边一对极性焊盘的限制,并分别改变了版图的整体大小、版图大小、形状与焊盘形状、间隔以及版图的倾斜角度,随机生成了一批版图,见图4,称为异形样本。

图4 非标准图形数据示例

对异形样本的测试集进行了测试,然后针对测试中所暴露的弱点进行三次再训练。四次训练的特点和获得的权值如表1 所示。

表1 权值的标号

4 实验结果

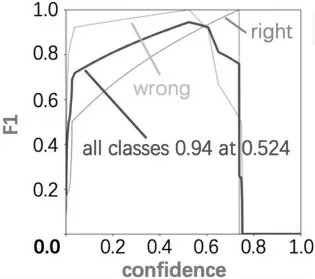

首先使用权值weight1.pt 针对100 张与训练集规格完全相同的测试图片进行了测试。实验结果如图5、图6所示。当置信度位于0.02(约)至0.75(约)区间内,召回率与准确率的平均效果值(以下简称为“F1 值”)从约0.70近线性上升至最大值0.94(置信度0.524),随后于最大置信度(约0.75)处达到下降至约0.75。

图5 第一次训练后的F1 曲线

图6 同类样本检测效果图

测试完成后在“detect”目录下生成了一个包含测试后图片的文件夹。结果显示,该轮检测精确率达到100%,召回率也在99%以上。由此可见,在同类样本的检测方面,该版图检查器展现出了卓越的性能。

第二轮实验考查检测器的原始泛化能力,仍然使用权值weight1.pt 对异形样本进行测试,结果如图7 和表2(第一次)所示。版图检查器对于等比缩小样本的检测精度低,对于间隙改变、角度改变的查全率较低。同时,由于生成异形样本时取消了一边一对极性焊盘的限制,对于同极性相邻的情况,检查器将其误识别为正确样本。版图检查器针对异形样本的精确率与召回率都不高。

图7 第一次训练后的异形样本检测结果

第三轮实验中,加入同比缩放的样本进行训练,得到weight2.pt 后,再对异形样本测试,结果如表2(第二次)所示。检查器对于小尺寸目标的检测性能得到大幅提升。在本轮检测中,小目标的边界框与实物更加贴合,检测精度上升。对于宽、窄间隙的识别也更加精准。同时由于新数据集中焊盘的排布取消了限制,该轮检测中同极性相邻判定错误的问题得到了解决。

第四轮实验中,加入版图大小、形状与焊盘形状、间隔改变的数据集进行训练,得到weight3.pt 后,再对异形样本测试,结果如表2(第三次)所示。检查器对于小目标边框的锚定得到了进一步优化。同时对于不规则矩形焊盘与宽度不规范的间隙有了更高的识别精度。对于倾斜摆放的版图样本,召回率已达到90%以上。但由于尚未针对这一样本进行训练,边界框的框定不规范,精确率不佳。

第五轮实验中,加入版图倾斜的数据集进行训练,得到weight4.pt 后,再对异形样本测试,结果如表2(第四次)所示。版图检查器的泛化性能得到进一步提升。针对异形测试集,版图检查器的精确度达到预期。同时,由于泛化能力的提升,在小目标的检测上边界框贴合度有所下降。至此,该版图检查器针对同、异形样本的检测精度已全部达标。

经过四轮针对异形样本的实验,可以看出一些规律。随着训练样本的逐渐丰富,该版图检查器对于任一类型样本的检测精度与边界框贴合程度逐步平均,提示该版图检查器的泛化能力能够随训练提升。同时,检查器对于最近结束训练的样本表现出更优越、更稳定的检测性能。

如表3 所示,版图检查器的最大F1 值在前三次训练中由0.94 单调升至1.00,在第四次训练后降至0.92。同时最大F1 值所对应的置信度在第二次训练时达到最大值0.641,而后于第四次训练后单调下降至0.363。

表3 各轮训练后版图检查器的综合性能总表

前三次训练方向基本一致,重点关注提升检查器对于小样本、不规则形状、不规则间隙的检测精度。而第四轮训练的样本则需要更普适、包容性更强的标记方式。因此,在第四次训练后检查器的对于各类样本的检测效果趋于平均,对于同类样本以及不倾斜异形样本的检测效果相较第二、三次训练后有所下降。同时,经过修正训练,版图检查器对于焊盘排布规则的改变表现出了较强的适应能力。

5 结论

目标检测算法Yolo v3 在芯片版图焊盘排列规则的检测上表现出了优异的性能。在规整的版图样本和不规整的版图样本上都得到很高的精确率与召回率。展示出很强的泛化能力和适用能力。

集成电路版图的布局须遵循一定的规则。本次研究表明,通过训练深度神经网络在集成电路版图检查方面有很大潜力,值得持续的探索与挖掘。