用于芯片电容精确测量的在片开路方法研究

2022-07-12乔玉娥丁立强刘霞美吴爱华

李 灏, 乔玉娥, 丁 晨, 丁立强, 刘霞美, 吴爱华

(中国电子科技集团公司 第十三研究所,河北 石家庄 050051)

1 引 言

电容是芯片工艺测试中的重要参数,在微电子领域有着广泛应用[1],测试量值的准确与否,直接影响到芯片产品及所列装整机系统的可靠性。与实物电容相比,在片电容准确测试的难度更大。常见的芯片电容测量系统,如PCM系统、MEMS测试系统等,通过矩阵开关、转接头、线缆、探针(探卡)等将测试仪器同被测芯片相连接,回路所包含的影响量复杂;且芯片与探针直接裸露在空气中,受到外界的干扰也更加明显。电容测试过程中,开路效果的好坏直接影响测试结果准确性[2]。标准电容器测试过程中,使用配套的开路器能够达到较为理想的开路效果;然而在片电容参数测试,由于缺少专用开路器,目前多采用探针悬空开路的方式,由于空气中开路无法对在片测试过程干扰量进行精确补偿,且开路状态难以固定,开路效果难以保证。

本文针对在片电容参数测试中开路难题,对标准电容器、开路器结构原理进行分析,研究了在片电容参数开路方法,设计并制作了在片形式的开路器,利用自行搭建的在片测量系统对开路效果进行了实验验证。结果显示,在片开路器能够达到较好的开路效果。

2 设计方案

2.1 标准电容开路器

作为复现电容单位量值的实物器具,标准电容器具有良好的稳定性[3],受外界环境影响小,能够最大程度上保证电容测试结果的准确性[4]。对于量值在100 pF范围内的小电容,多采用空气(或纯氮气、纯氩气)电容器形式进行制作[5,6]。

尽管标准电容器具备良好的指标特性,其仍然不可避免地存在着附加误差。在图1所示的四端对空气电容器等效电路模式中[7],CLH为该电容器目标被测量值;CHG为电容H端与外屏蔽层之间的分布电容;CLG为电容L端与外屏蔽层间的分布电容;LOLC、LOLP、LOHP、LOHC分别是各个端口到目标电容器的引线电感。上述引线电感及分布电容的存在,会对电容测量结果造成干扰。以Keysight公司16380A系列标准空气电容组为例[8,9],其分布电容的CHG典型值在17~33 pF范围内,CLG典型值在29~48 pF范围内,这些分布电容会给电容量值精确测试带来不可忽略的系统误差。

图1 四端对空气电容器等效电路模型Fig.1 Equivalentcircuit model of the four-terminal pair air capacitor

为了实现电容的精确测试,减小分布电容、引线电感等带来的误差,标准电容器需配备开路器进行使用。开路器内部结构同标准空气电容类似,在原电容位置使用开路进行替代,以模拟电容器结构引入的误差因素,并通过电容测量仪器的开路补偿功能进行消除[10,11]。开路器使用介质(如空气、纯氮气、纯氩气等)进行填充,有的在中间设计有隔离层,以进一步提升高端和低端间的屏蔽。图2所示为Agilent 42090型四端对开路器,其能够较好地搭配16380A电容组,实现标准电容的准确测试。

图2 Agilent 42090型四端对开路器Fig.2 Agilent 42090 four-terminal pair open termination

2.2 在片开路方案

2.2.1 在片电容开路器设计

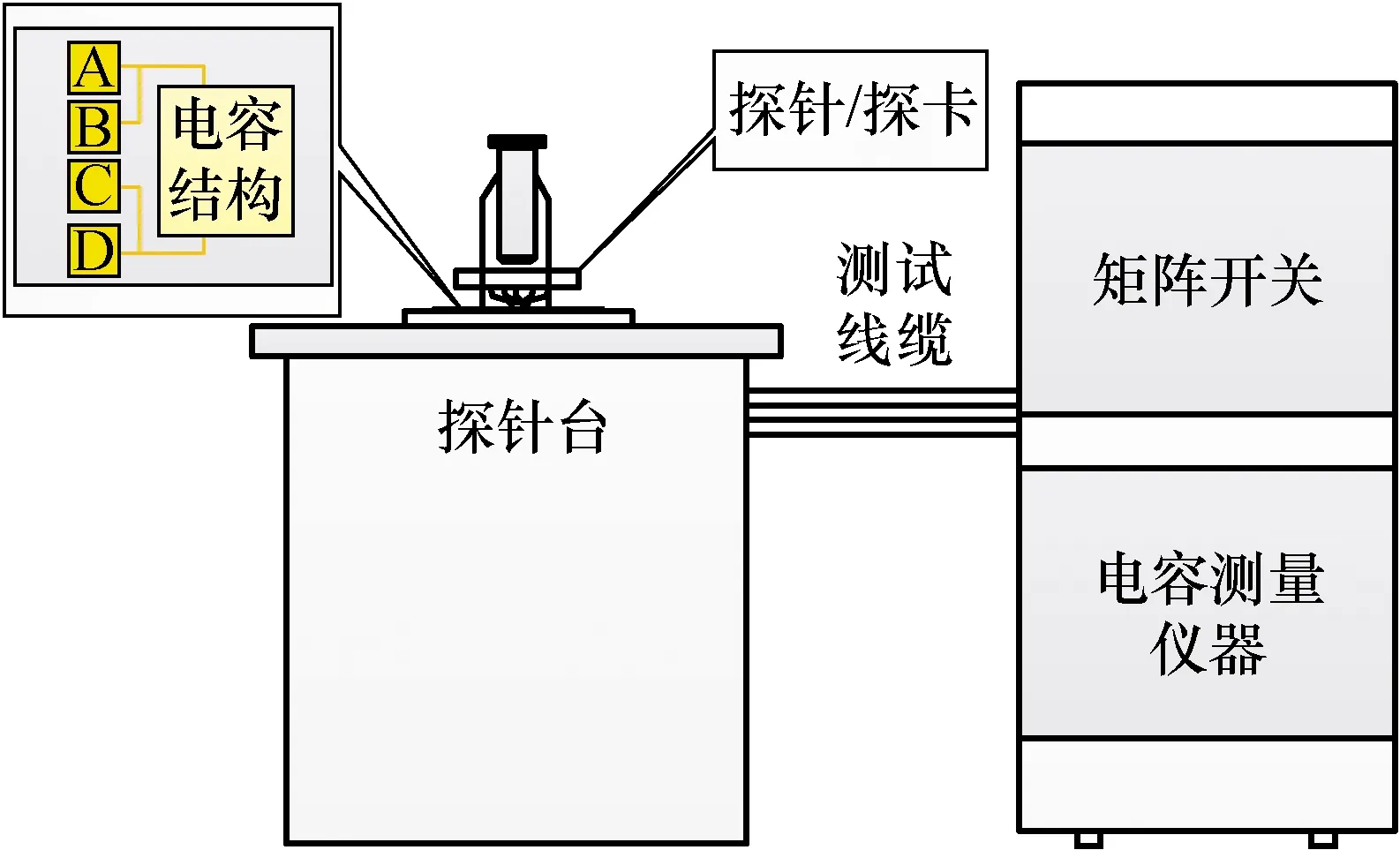

随着芯片技术的不断发展,在片电容参数测试成为半导体工艺生产中的重要环节。图3所示为典型在片电容测试系统结构示意图,电容测量仪器通过矩阵开关、测试线缆(转接头)、探针探卡等连接结构,同在片电容结构的4个PAD接触,完成在片电容的容值测量[12]。由于目前主流的电容参数测量仪器选用四端对形式,因而在片开路器也选用了四线结构[13]。

图3 在片电容测量系统结构示意图Fig.3 Structural diagrammatic drawing of the on-wafer capacitor measurement system

由于在片电容参数的特殊测量形式,其测量结果更易受到其它因素干扰:芯片表面PAD、金属导线等带来的引线电感及分布电容[14,15];芯片、探针为点接触,且暴露在空气中,难以实现良好屏蔽;探针与金属PAD间在近距离接触时也会存在微小的分布电容等[16]。这些干扰的存在,给在片电容参数精确测试带来了困难[17]。

为了尽可能消除上述干扰,测量前也必须进行开路操作。由于缺乏专用在片开路器,目前,在片电容测试系统的开路还只能通过探针悬空开路的方式进行。但该方法无法准确模拟芯片电容测试过程的附加误差,不能对干扰因素实现有效修正;同时,悬空开路方法的开路状态(开路高度、位置、空气环境等)难以固定,也会影响测量数据间的一致性。

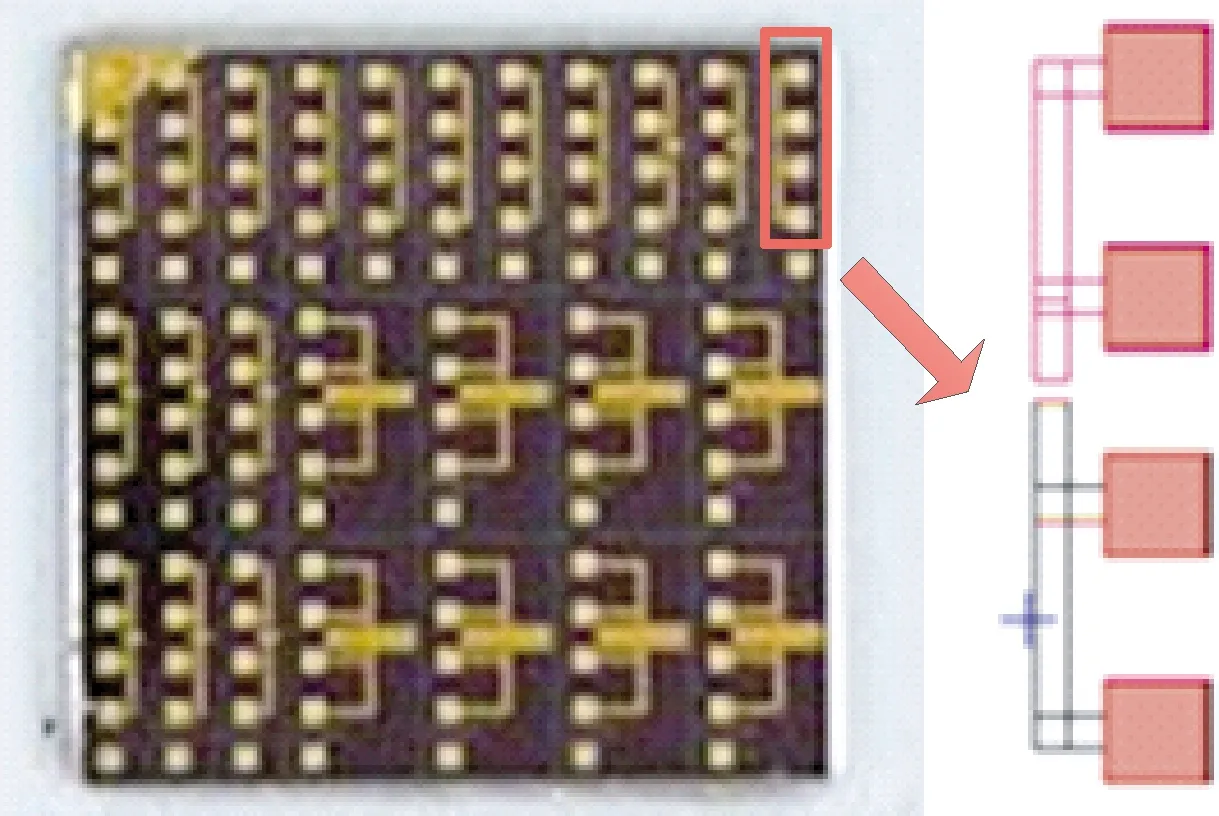

为此,参考标准电容开路器的结构原理,设计了专用于在片电容测试的开路器[18]。如图4所示,该结构在典型芯片电容结构基础上,将电容部分用芯片衬底材料代替,仅保留原结构的金属PAD及引线结构。为了实现开路器同被测电容间的良好匹配,其结构尺寸都应严格按照被测电容进行设计制作,才能保证附加误差修正的针对性与准确性。

2.2.2 在片电容开路器工艺制作

在上述在片开路器设计方案基础上,进行了半导体工艺制作,主要包括以下3个步骤:

(1)结构制作

在芯片衬底材料上制作出能够实现开路器功能的微小结构。为了保证开路器制作效果,使其更加贴近工艺线上实际测试需求,选择采用半导体领域主流的GaAs工艺进行制作。GaAs材料作为衬底材料能够实现引线间较好的隔离,避免引入新的干扰量。开路器结构尺寸同被测芯片保持一致,从而保证了开路补偿效果。所制作的在片开路器单元尺寸为10 mm×10 mm,包括4个面积为300 μm×300 μm的接触电极。

(2)钝化

在片开路器尺寸微小,直接暴露在空气中容易被氧化,影响其功能及量值的长期保持。为进一步提高其稳定性,在开路器结构制作完成后,在表面覆盖了一层SiN材料进行钝化。通过在芯片表面形成一层保护层,避免外界温度、湿度、尘埃、电磁干扰的影响。通过该处理,有效提高了在片开路器的稳定性。

(3)加固

GaAs晶圆片厚度很小(600 μm左右),且本身材料较脆,极易在外力作用下出现损坏。为提高其耐用性,对其进行了加固处理,主要包括减薄、划片及装架3个环节。在装架过程中,由于在片开路器采用的是正面工艺,芯片通过粘结剂粘附在载体上。装架载体的选择方面,为保证绝缘效果及支撑强度,采用了陶瓷片作为载体。

制作完成的在片开路器实物如图5所示。

图5 在片开路器实物图Fig.5 Real products of the on-wafer capacitor open instrument

3 实 验

为了对在片开路器的效果进行评估,自行搭建了在片电容测量实验系统。实验系统结构示意图如图6,主要由电容测试仪器(GenRad1693型LCR电桥)、线缆、探针台及探针(探卡)组成。图7是搭建完成的实验系统实物图。

图6 在片电容参数测试实验系统示意图Fig.6 Drawing of the on-wafercapacitance parameter measurement experimental system

图7 实验系统实物图Fig.7 Real products of the experimental system

实验系统搭建完成后,首先针对探针悬空开路的效果进行了实验验证。为了探究开路状态的改变对数据一致性的影响,实验选择探针高度作为变量,对开路时探针高度进行改变。在完成开路操作后,对标称值为1 pF的在片电容进行了测试,测试频率为1 MHz。表1所示为探针高度对开路效果的影响数据,其中开路高度指开路时探针间位置同待测芯片距离。

表1 开路高度对测试结果影响Tab.1 Influence on the measurement results by open height

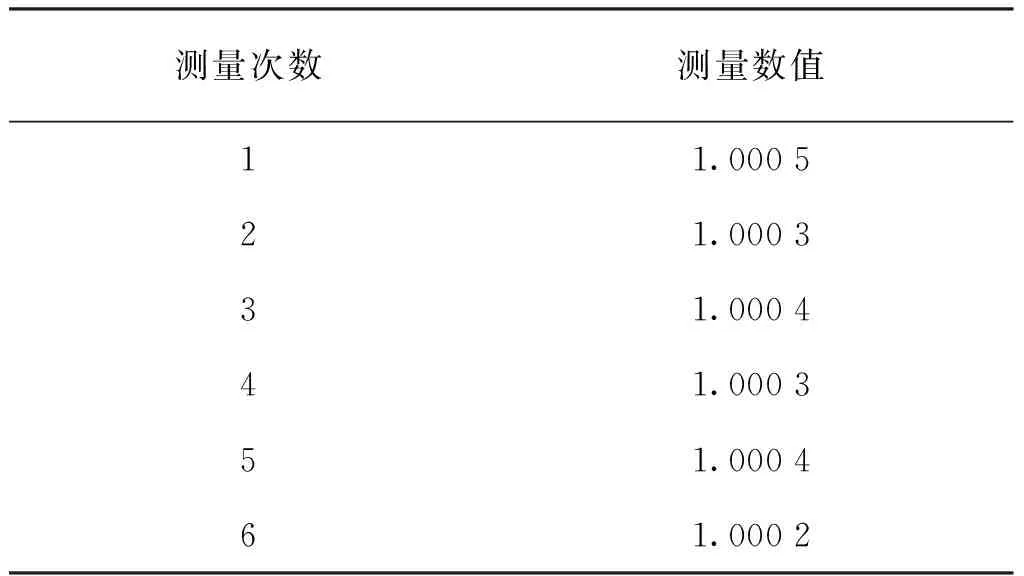

使用研制的在片开路器进行了开路及测试的操作,测试数据如表2所示。

表2 在片开路方式测量结果Tab.2 Measurement results with on-wafer open operation pF

实验结果表明,采用空气悬空开路方式时,探针距离芯片的高度的变化,会对开路效果造成干扰,数据显示,高度每变化1 mm,电容测量值约变化0.6%。使用在片开路器进行开路时,由于对开路状态进行了有效固定,避免了环境条件的影响,开路数据一致性更好;通过计算相对标准偏差可知,在对1 pF电容进行测量时,测量重复性可以达到0.01%;同时,同电容样片的标称值相比,在片开路方法测得的结果也具有更好的符合性。

4 结 论

针对片上电容参数测试过程中缺乏专用开路器,开路效果无法保证的现状,在分析标准电容器、开路器原理结构的基础上,针对在片开路方法开展了研究,设计并制作了专用的在片开路器。通过与芯片工艺线上现行采用的空气悬空开路法进行实验比较,使用研制的在片开路器进行开路操作,能够有效提高测量结果的准确性、一致性。该在片开路器设计及制作方法,在片上电容计量测试领域具有较好的应用价值。