面向低轨卫星通信的K波段LTCC多通道集成接收前端模块

2022-07-02徐仲麟吴林晟佘胜团吴毓英毛军发叶雯燚

徐仲麟,吴林晟,佘胜团,吴毓英,毛军发,叶雯燚

(1. 高速电子系统设计与电磁兼容教育部重点实验室(上海交通大学),上海 201100;2. 广州润芯信息技术有限公司,广东广州510700;3. 上海航天电子通讯设备研究所,上海 201100)

1 引言

低轨道(Low Earth Orbit,LEO)卫星通信可以在宽带互联条件下提供高速多媒体传输,包括但不限于语音、数据、图像以及视频等信息. 低轨卫星通信是对地面无线通信的重要补充,是构建下一代空-天-地-海一体化宽带无线通信系统从而大幅提高通信覆盖范围的潜在关键技术之一[1]. 接收前端对接收到的射频信号进行低噪声放大和多通道幅相控制,在卫星通信系统中扮演着重要角色,接收前端的性能直接影响卫星通信系统接收链路的性能. 另外,无线通信系统朝着高速率、多功能化的方向快速发展. 随着工作频段不断升高,天线单元间距明显缩小,高频传输损耗和寄生效应越来越显著,射频前端小型化和高集成的需求变得越来越迫切. 因此,研发高性能的集成接收前端模块对满足低轨卫星通信应用需求十分重要[2].

系统级封装(System in Package,SiP)技术充分融合了半导体、微组装与先进封装工艺的优势,所需的各类功能芯片采用各自最优的工艺实现,无源器件与互连器件嵌入多层封装基板内部,芯片与封装基板三维堆叠,同时实现了高集成度和高性能[3].SiP技术由于克服了单一半导体材料工艺的限制,在三维集成方面具有突出优势,并为散热设计提供了多样化的有效方案以增强系统可靠性,因此已成为目前高性能集成射频前端模块的重要解决方案[4].

射频SiP 的主要实现工艺有多层低温共烧陶瓷(Low Temperature Cofired Ceramic,LTCC)技术、高密度互连基板技术、晶圆级扇出封装技术、硅基三维集成技术等. 其中,LTCC 工艺将多层陶瓷基板压接的三维封装工艺. 它可以将各类无源器件,包括薄膜电阻、电容、传输线等集成到多层陶瓷基板内部,并与贴装在基板表面或腔体内的有源器件芯片连接.LTCC 多层布线与埋置组件更容易进行高密度集成前端模块设计,同时具有较好的加工精度和良好的稳定性[5]. 目前,基于LTCC 的射频SiP[6]已受到国内外学者和产业界的广泛关注.

2002 年,Lee 等人[7]提出了用于Ku 波段卫星通信的LTCC 单通道发射SiP 模块,集成了商用的GaAs MESFET MMIC,通道增益为41 dB,输出功率为26 dBm,验证了高密度集成SiP 射频前端的可行性. 2011 年,Karim 等人[8]将工作在60 GHz 的4×4 天线阵列与一颗GaAs 低噪声放大器芯片或一颗CMOS 开关键控(OOK)发射机芯片集成为SiP,设计中对键合线的寄生效应进行了补偿,集成低噪放芯片的天线阵列峰值增益约为35 dBi,集成了发射机芯片的有源天线阵列支持2 Gb/s 数据发射,能耗仅13.2 pJ/bit.2015 年,北京电信卫星研究所李银桥等人[9]基于LTCC 工艺设计了一款Ka 频段单路收发前端,集成了低噪放、移相器、衰减器、开关、驱放和功放等有源MMIC,带通滤波器和传输线过渡结构在LTCC 基板内部实现,整体尺寸为36×20×1.1 mm3. 该接收机的增益为33 dB,噪声信号小于4.2 dB;发射机输出功率大于24.6 dBm,测试增益大于25 dB.2018 年,中电54 所王璇等人[10]采用LTCC 结合薄膜工艺研制了一款Ka 频段六通道接收前端组件,集成了32 颗有源MMIC 和71 颗无源器件,整体尺寸为65×47.2×1.5 mm3,如果采用LTCC 工艺实现嵌入式滤波器则有望进一步提高系统集成度. 多层LTCC技术还被用于更高频段的三维集成射频前端实现当中.2016年,Tajima等人[11]基于LTCC工艺设计了一款300 GHz、数据率高达27 Gb/s的短距离通信集成前端系统,还集成了一个直径6 mm 的硅透镜,整体尺寸为10×10×4 mm3. 总体来说,目前还较少有多通道高频段三维集成前端SiP模块相关的报道.

本文面向低轨卫星通信,研发了一款工作在K 波段的LTCC 四通道集成接收前端模块,具有幅度和相位控制功能. 首先研究了接收前端模块的系统架构和低噪声放大器、移相器、衰减器等芯片选型,然后针对嵌入到多层基板内部的低通滤波器、功率合成器等无源器件进行了设计,并针对键合线的高频寄生效应提出了补偿设计方案,进而研制了整个集成接收前端模块及其控制板. 该模块链路增益、噪声系数、对发射频段的抑制度、相位和幅度控制误差等性能指标测试结果符合设计预期,验证了本集成SiP 方案的正确性和有效性.

2 系统设计

2.1 技术指标与系统架构

为满足低轨卫星通信接收前端技术需求,本文研制的K波段集成接收模块的主要设计指标如下:

(1)工作频带为17.7~20.2 GHz;

(2)通道数为4;

(3)单通道增益≥36 dB;

(4)单通道噪声系数≤2 dB;

(5)幅度控制为5位;

(6)相位控制为6位;

(7)对28~30 GHz发射频段的抑制≥50 dBc;

(8)面积为28×28 mm2.

根据上述指标,主要器件选型信息如表1 所示,均为GaAs芯片.

表1 器件选型

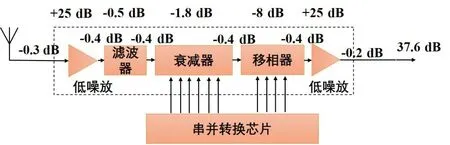

图1展示了单通道接收链路框图,包括两级低噪声放大器、滤波器、衰减器、移相器以及用于控制移相器和衰减器的串并转换芯片等. 其中,滤波器、衰减器、移相器等无源器件位于两级低噪放之间,可降低链路局部增益过高可能造成的风险;设置于第一级低噪放之后的低通滤波器由嵌入LTCC 多层基板中的带状线结构实现,可对发射28~30 GHz 频段提供较高的抑制度.图1 上标注了互连的传输损耗和经过各级器件后链路增益的数值. 第一级低噪放输入端的互连包括一根键合线和LTCC 基板上的传输结构,各级芯片之间采用键合线及基板上的传输线进行互连,第一级前互连和级间互连的插入损耗分别按照0.3 dB和0.4 dB预估,主要由键合线引入. 自第一级低噪放输入端互连开始,经过两级低噪放、滤波器、衰减器、移相器及各级间互连器件后,到达该链路的输出端,累计增益约为37.6 dB.

图1 单通道接收链路框图

对于接收链路,进行链路预算时主要考量通道增益与噪声系数指标. 对于由不同器件与传输结构级联而成的接收链路,其整体噪声系数Ftotal可由下式计算得到:

其中,F1,F2,Fn分别代表链路中从输入端开始第1 级、第2级、第n级器件的噪声系数;G1,G2,Gn分别代表各级的增益. 前级器件的噪声系数与增益对于接收链路整体噪声指标影响较大,将低噪声放大器放置在链路前级,可有效压制后级器件对于噪声性能的不利影响. 在接收前端模块实现中,低噪放前无源互连器件的损耗对接收链路噪声系数的影响不可忽略,应做好传输匹配,尽量降低互连损耗. 将低噪放噪声系数1.3 dB 和增益25 dB代入式(1)可得,接收通道经过输入端无源互连器件及第一级低噪放后,噪声系数为1.6 dB. 将滤波器、衰减器、移相器及其互连组成的无源电路整体视为一级,其插入损耗约为11.9 dB(衰减器基态). 经过该无源电路后链路噪声系数约为1.74 dB,经过末级低噪放后,链路的噪声系数约为1.79 dB. 由此,单通道接收链路增益和噪声系数相比设计目标均有一些余量.

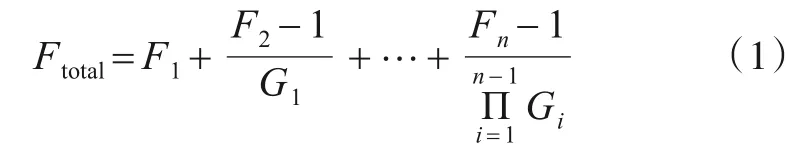

图2 为LTCC 四通道接收前端模块的原理框图. 该接收前端的工作频带主要由射频电路、控制及电源构成,外部接口包含1个公共的射频输出端口、4个天线输入端口及电源、控制接口等. 具体模块介绍如下.

图2 四通道射频接收前端模块原理框图

(1)射频电路:包括4个接收通道,每个通道主要包括两级低噪声放大器、用于抑制发射频段的低通滤波器、衰减器和移相器,4个通道经功率合成器后输出.

(2)控制电路:每个通道都配有1个串并转换芯片,为数控衰减器和数控移相器提供逻辑电平,实现对接收通道移相量、幅度衰减量的控制.

(3)去耦电路:低噪声放大器、串并转换芯片等的供电通过多层陶瓷电容在模块内实现第一级去耦.

该接收前端模块中总共集成了20个GaAs 芯片、16个陶瓷电容,以及嵌入多层LTCC 基板中的4 个低通滤波器和1个4路功率合成器.

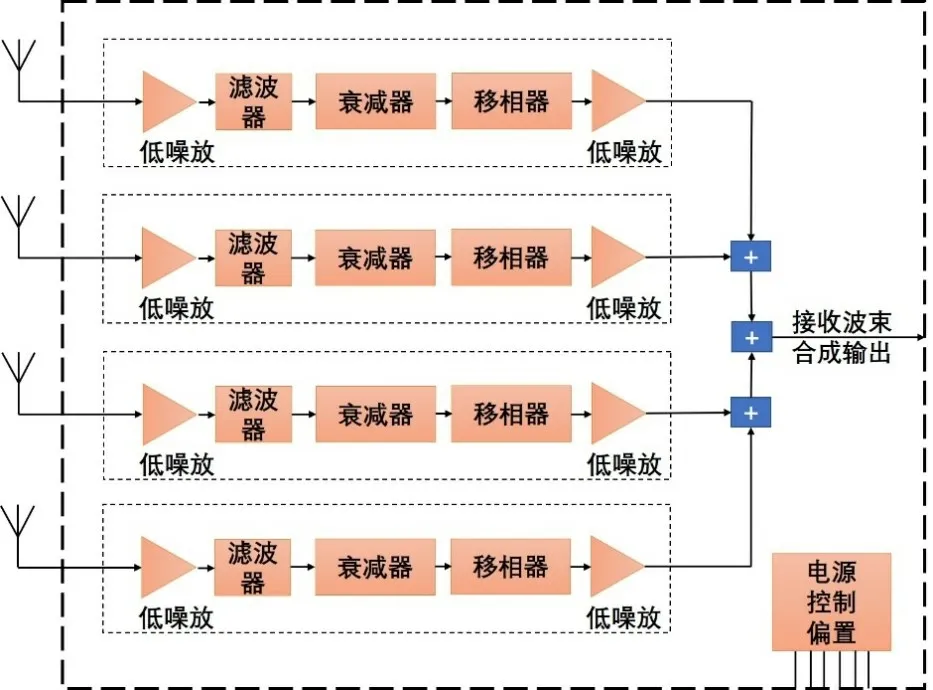

多通道集成接收模块封装引脚与芯片引脚之间的连接关系如图3 所示,图中红线代表射频信号,黑线代表控制和供电信号. 每条链路配备1 个串并转换芯片,用来提供衰减器和移相器的控制信号. 串并转换芯片24~20 端口对应衰减器的1~5 端口,12~8 端口对应移相器的1~5 端口,5~1 端口对应移相器的6~10 端口,共使用串并转换芯片中15个端口,有9个端口空载.4个串并转换芯片采用数据与时钟接口串联拓展,仅需要第一路引出数据与时钟输入接口,即可完成4路数据与时钟写入.4个串并转换芯片供电并联,仅需要第一路引出正负2 个供电输入端口.4 个串并转换芯片的使能输入单独引出,每条通道2 个低噪放共用1 条漏压供电通道,共引出4条LNA漏压供电,方便进行单链路调试测试.

图3 芯片和封装引脚连接关系

2.2 低通滤波器设计

本文使用的LTCC 基板材料为Ferro A6,相对介电常数为εr=5.76,损耗角正切为tanδ=0.002. 每层陶瓷基板烧结后的厚度为96 μm,金属厚度为10 μm,金属化通孔的直径为127 μm. 图4为嵌入LTCC多层基板中的带状线低通滤波器结构,采用1/4波长开路支节线滤波器拓扑,两端通过金属化过孔由带状线过渡到微带线形式. 该滤波器带状线部分由4层LTCC瓷带构成,外侧由金属化过孔阵列包围以保证电磁屏蔽,面积约为2.4×6 mm2.

图4 低通滤波器结构

图5给出了该低通滤波器的全波仿真结果,其截止频率为22.5 GHz,在17.7~20.2 GHz 频段内插入损耗为0.4~0.6 dB,回波损耗大于18 dB,在28~30 GHz 频段内插入损耗大于35 dB. 因此,该滤波器可以有效提高接收模块对发射频段的抑制度,并对接收频段影响较小,有更好的接收效果.

图5 低通滤波器的全波仿真结果

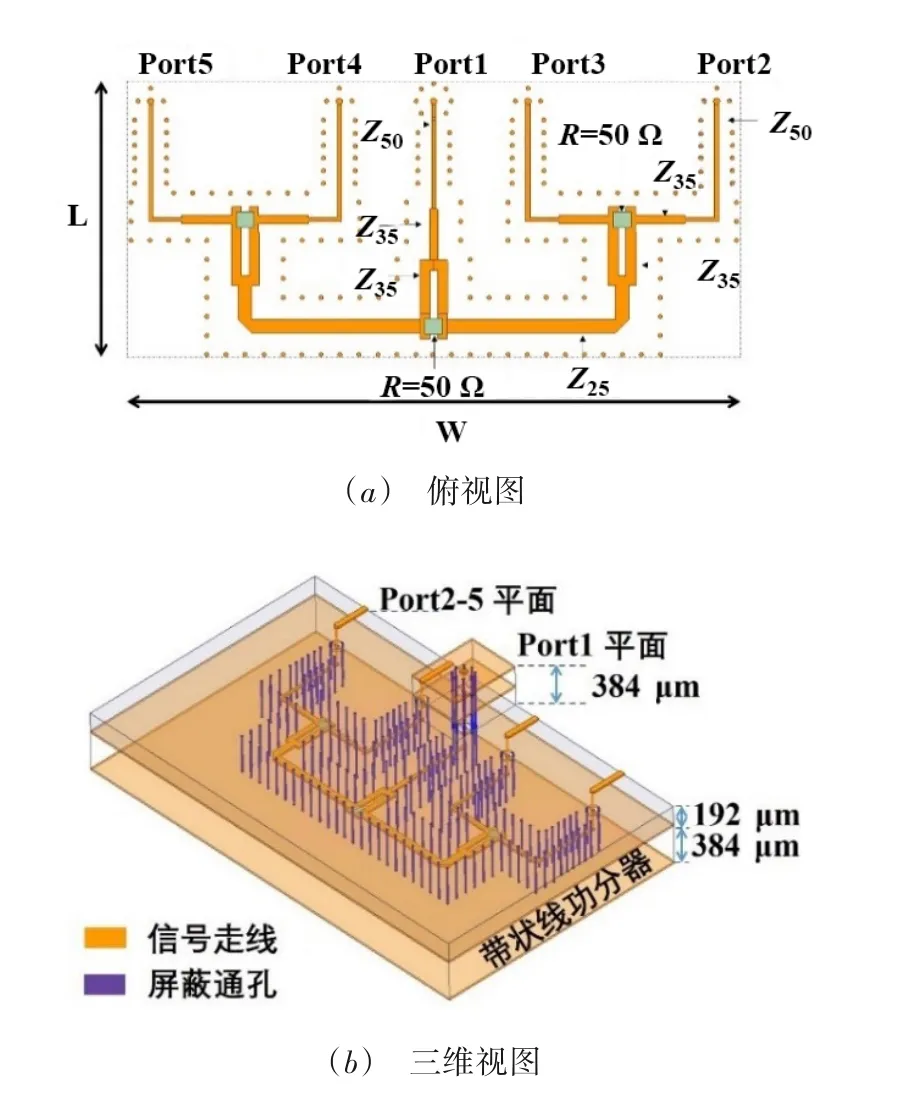

2.3 四路功率合成器设计

图6为所设计的四路功率合成器结构,其由两级二路等功分带状线Wilkinson 功分器级联而成. 带状线周围布有金属化过孔阵列,用于连接上下地面,并提供良好的隔离效果,避免电磁干扰和寄生谐振. 功率合成器的5 个输入/输出端口均通过金属化过孔组成的准同轴结构引至上层,实现与基板表面微带线的过渡以及与其他元器件的连接. 传统Wilkinson 功分器的端口阻抗均为50 Ω,用于阻抗匹配的1/4波长传输线特性阻抗为70.7 Ω. 但由4 层瓷带构成的LTCC 基板中70.7 Ω 带状线的导带宽度为40µm,不符合本文采用的LTCC 工艺最小线宽70µm的限制. 出于集成前端模块整体厚度与成本方面的考量,未采用增加瓷带层数即基板厚度的方式以增大传输线导带宽度. 将2路功分器端口阻抗和中间传输线的特性阻抗均设为25 Ω,1/4 波长传输线的特性阻抗相应调整为35.35 Ω,隔离电阻调整为50 Ω. 为实现对外50 Ω 的端口阻抗,在每个端口增加特性阻抗为35.35 Ω 的1/4波长传输线阻抗变换器.4层瓷带介质厚度为384µm,25 Ω,35.35 Ω 和50 Ω 带状线的导带宽度分别为419 µm,244 µm 和124 µm,均满足工艺要求.功率合成器整体面积约为12.5×20 mm2.

图6 功率合路器结构示意图

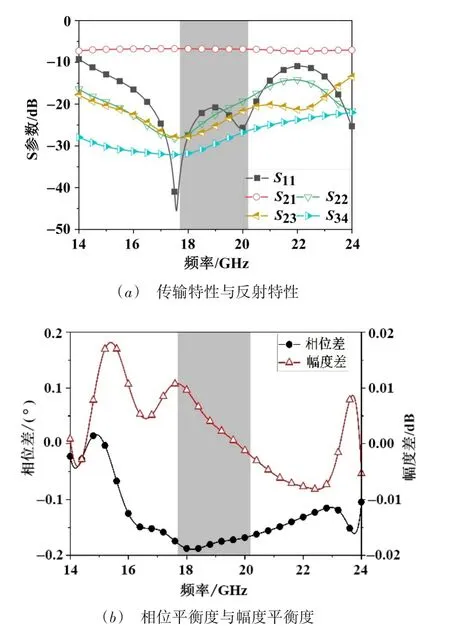

图7展示了所设计的功率合成器的全波仿真结果.鉴于结构的对称性,输入端口2与端口5、端口3与端口4 分别对称,图中只展示了部分具有代表性的曲线. 在17.7~20.2 GHz 频段内,输入到输出端口的插入损耗约6.8 dB,考虑到四路功率分配插损理想值为6 dB,该电路引入的额外插损为0.8 dB. 输出端口1 的反射系数在-21 dB 以下,输入端口的反射系数优于-18.5 dB,保证其在前端系统中与其他电路连接时不易引入额外反射和寄生谐振. 在工作频带内,该功率合成器各输入端口的幅度差异小于0.02 dB,相位相差小于0.2°,平衡度较好. 该四路功率合成器也具有良好的输入端口间隔离特性,相邻输入端口间隔离度优于21 dB,非相邻输入端口间隔离优于26 dB.

图7 功率合路器全波仿真结果

2.4 键合线补偿结构设计

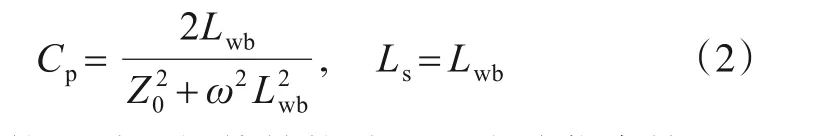

在三维SiP 结构中,射频芯片通过导电银胶贴装到LTCC 基板表面,芯片与微带线、控制线之间通过直径25 µm 的金丝键合线实现电气连接. 随着工作频段的升高,键合线带来的寄生效应愈发显著,会引入一定的失配和损耗,特别对噪声系数等指标产生负面影响,需要采用额外的补偿结构来优化传输特性. 键合线具有较强的感性,可使用容性结构进行补偿. 图8 所示是键合线以及补偿结构的三维结构示意图,等效电路模型如图9 所示. 双线键合线由芯片射频口的信号电极引出,另一端接在LTCC 基板表面微带线焊盘上,等效为电感Lwb. 连接键合线的微带线焊盘面积较大,并在焊盘下方设置一片同样大小的接地贴片以进一步增大并联电容Cp,见式(2). 贴片后设置了一段高阻抗传输线,提供串联电感Ls,端口阻抗为Z0. 当满足下式时,工作频带内具有较好的匹配特性[12].

图8 键合线补偿结构

图9 键合线及其补偿结构的等效电路模型

图10 比较了采用补偿结构前后的全波仿真结果.采用所设计的键合线补偿结构后,在17.7~20.2 GHz 接收频段内,回波损耗增加了18 dB 以上,插入损耗减小了0.2~0.3 dB. 因此,该键合线补偿方案对改善互连器件传输特性具有显著效果,进而对接受链路的噪声系数有较大改善.

图10 采用补偿结构前后全波仿真结果比较

2.5 三维集成接收前端模块设计

图11 给出了整个集成接收前端模块的结构图,总共使用了13 层LTCC 瓷带,以L1~L13 表示. 其中,L1~L4层构成口状围墙结构,所有射频与控制信号都通过位于围墙顶部M1金属层的接口输入输出.

图11 集成接收前端模块的层叠示意

在L5 层表面的M5 金属层上布有用于贴装芯片的大面积金属地以及传输射频信号的微带线,控制线和供电线主要分布在M5和M6金属层上. 通过合理布局,射频信号线与控制、供电线均互不干扰. 基板L7~L10为带状线功率合成器和4 个低通滤波器的介质层,M7和M11 金属层为带状线的上、下金属地面,带状线导带位于M9 金属层上.M12 金属层也用于供电线和逻辑控制信号互连,L13介质底部的M14金属层是整个接收模块地平面. 不同金属地平面通过金属化过孔阵列连接,以实现良好的接地效果和电磁屏蔽.

3 测量结果与分析

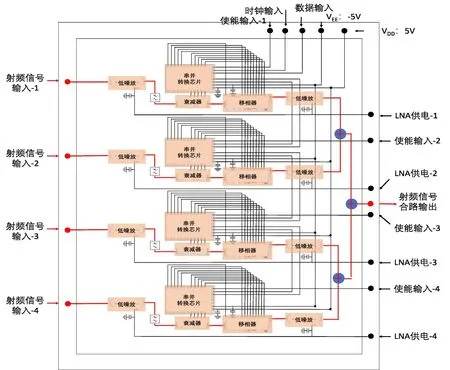

加工完成的集成接收前端模块及其控制板如图12所示,接收前端模块的整体尺寸为28×28×1.35 mm3.图13 为控制板电路原理图. 控制板为集成接收前端模块提供了外部电源管理与数控接口,控制板引出+7 V与-6 V 两个电源接口,通过板内的电源转换芯片为模块中和控制板上各芯片提供所需的电压(包括+5 V,+3.3 V,-5 V)和使能信号. 数字控制信号由单片机以串行码的方式输入.

图12 集成接收前端模块及其控制板

图13 接收模块控制板电路原理图(续)

图13 接收模块控制板电路原理图

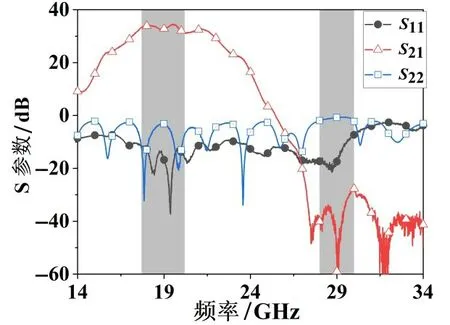

将其他3 个通道供电关断时,单通道基态的S 参数测量结果如图14所示.

图14 单通道基态测量结果

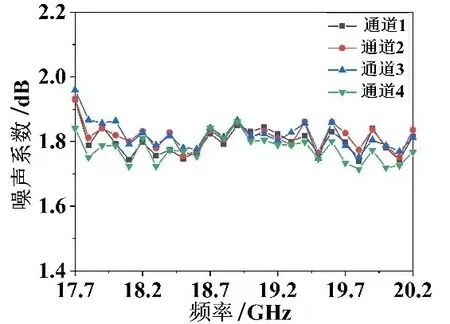

该通道带内传输增益大于31.5 dB,注意单通道测量时四路功率合成器会引入约6.8 dB 的插入损耗,因此单通道接收链路增益约为38.3 dB. 在28~30 GHz频段内,|S21|小于-30 dB,因此其对发射频段的抑制度超过61.5 dBc,主要来源于前级低通滤波器. 图15为4 个通道分别测试的噪声系数,在17.7~20.2 GHz 频段内为1.7~1.9 dB,该结果与此前估算的数值相吻合.

图15 四通道噪声测试结果

图16 给出各种幅度控制条件下的测量结果,此时移相器处于基态. 表2总结了5位衰减器从0.5~15.5 dB 各衰减状态的幅度控制误差,均在±1 dB以内.

表2 不同衰减态幅度控制误差

图16 幅度控制功能测量结果

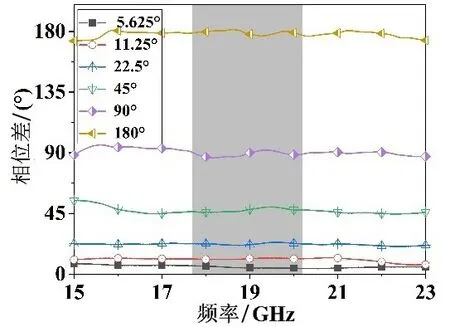

图17 给出了各种相位控制条件下的相移结果,此时衰减器处于最大衰减态,表3 列出了6 位移相器从5.625°到180°的相位控制误差,均在-3.7°~4.7°以内.

表3 不同移相态相位控制误差

图17 相位控制功能测量结果

表4对比了相近频段不同LTCC射频前端模块尺寸和性能. 文献[10]中滤波器采用薄膜工艺单独实现后安装在LTCC 表层,再通过键合线与LTCC 表面的传输线互连,未充分利用LTCC 基板埋置和三维集成能力,并可能引入更多的互连损耗. 文献[7]和[9]较好地利用了多层LTCC 的集成优势,在LTCC 基板内部嵌入了无源器件,使得前端整体的集成度有所提升. 但这两项工作的通道数量仅1~2,总器件数量较少,互连器件和系统复杂度都相对较低. 本文为满足低轨卫星通信多通道集成接收前端设计实现需求,对器件安装布局和互连网络布线设计都进行整体优化,充分利用多层LTCC 三维互连和嵌入无源器件的突出优势,在LTCC基板内部嵌入了一个4 路功分器和4 个低通滤波器,结构十分紧凑,单位面积集成器件密度进一步提高. 而且,由于本文对输入端互连结构进行了优化补偿,插入损耗和回波损耗都有所改善,接收链路噪声系数也显著优于其他文献报道.

表4 不同前端模块性能对比

4 结论

综上所述,本文基于GaAs射频芯片和多层LTCC封装工艺,设计研发了一款K 波段四通道集成接收前端SiP模块. 该前端模块集成了低噪放、移相器、衰减器、串并转换芯片和去耦电容,将低通滤波器和四路功率合成器嵌入到三维封装基板中,并对键合互连寄生效应进行了补偿. 单个接收通道的带内增益测试结果优于38.3 dB,噪声系数优于1.9 dB,带外抑制度优于61.5 dBc,增益和噪声系数测试结果与预测值较为吻合,且幅度和相位控制的测量结果较好,验证了本文设计的正确性和有效性. 所研发的LTCC多通道集成接收前端模块具有集成度高、增益高、抑制度高、噪声低等突出优点,可进一步与封装天线阵列一体化集成,在低轨卫星通信前端系统中具有较好的潜在应用价值.