高性能FPGA核电压的数字电源设计

2022-06-16陆骏,唐勇,王朋

陆 骏,唐 勇,王 朋

(中国电子科技集团公司第58研究所,江苏 无锡 214072)

0 引 言

随着科学技术的发展,得益于更高制程能力下,从百万门、千万门,到当代数亿门的高性能FPGA处理器广泛应用于通信、医疗、航天、航空等领域。从28 nm、20 nm、16 nm到7 nm,内部集成的门电路也急剧增多,对应需求配套的核电压也越来越低,电流越来越大,同时需要满足2%的输出电压精度,在大电流的负载高速突变下也要保证输出电压的稳定性[1]。数字电源具有的高控制精度和电源管理的优势,能很好地应用于高性能FPGA供电设计。

1 高性能FPGA的性能指标要求

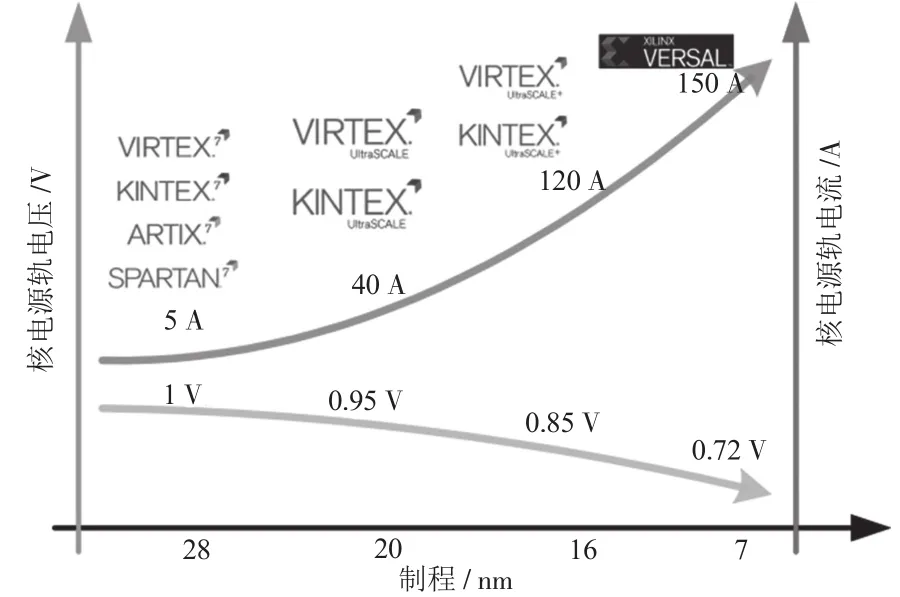

XILINX和Intel公司的高性能FPGA占据了全球90%的市场份额,其中XILINX的产品系列最为丰富,应用较为广泛。图1展示了XILINX公司系列产品的制程发展。目前已量产的最先进7 nm制程下产品需要的核电压低至0.72 V,供电电流高达150 A甚至更高。且FPGA的工作特点是大电流的负载瞬变特性下要求的输出电压交流值变化量在5%以内。这对核电压电源设计充满了挑战。

图1 赛灵思系列产品

2 数字电源方案设计

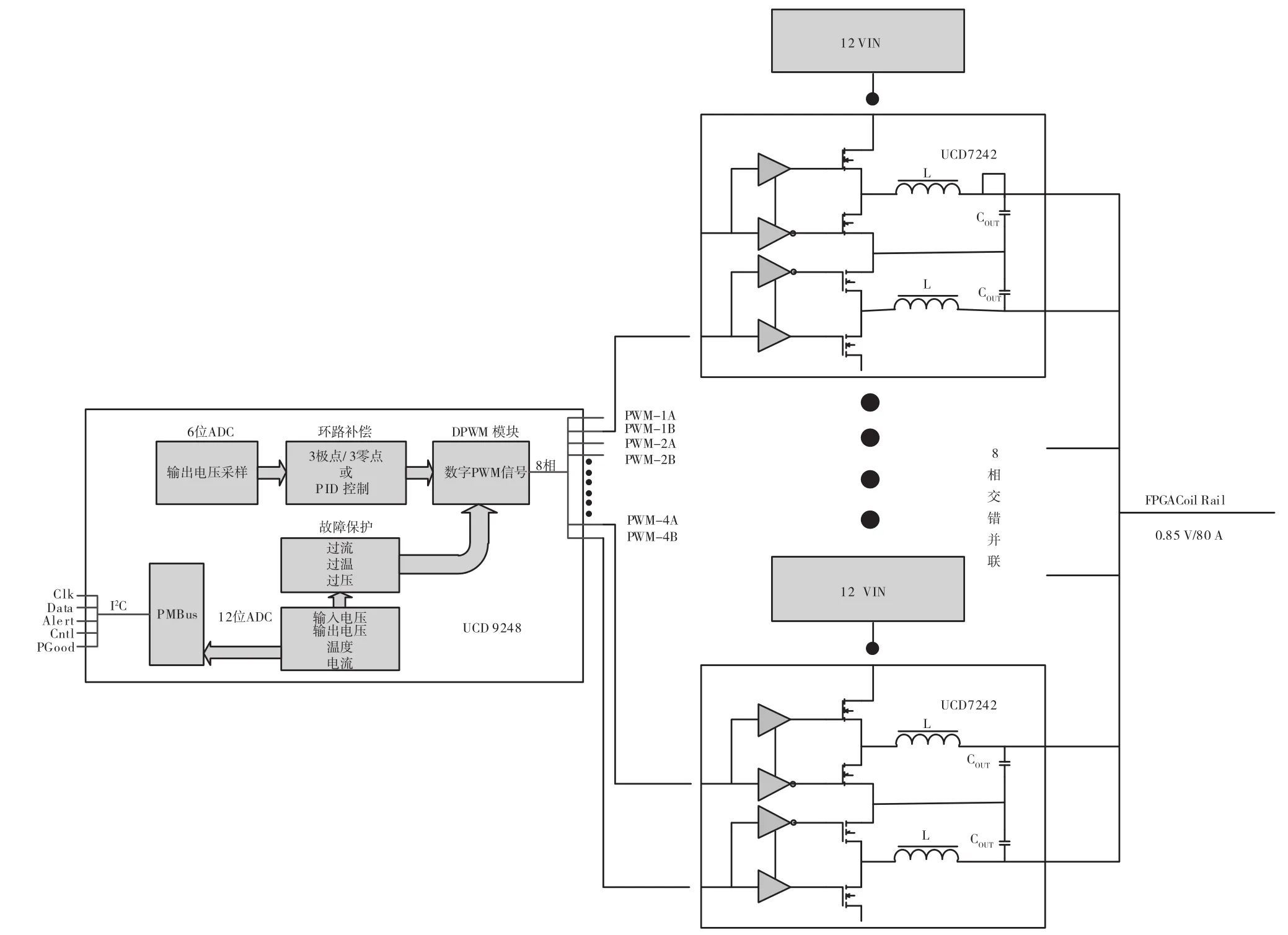

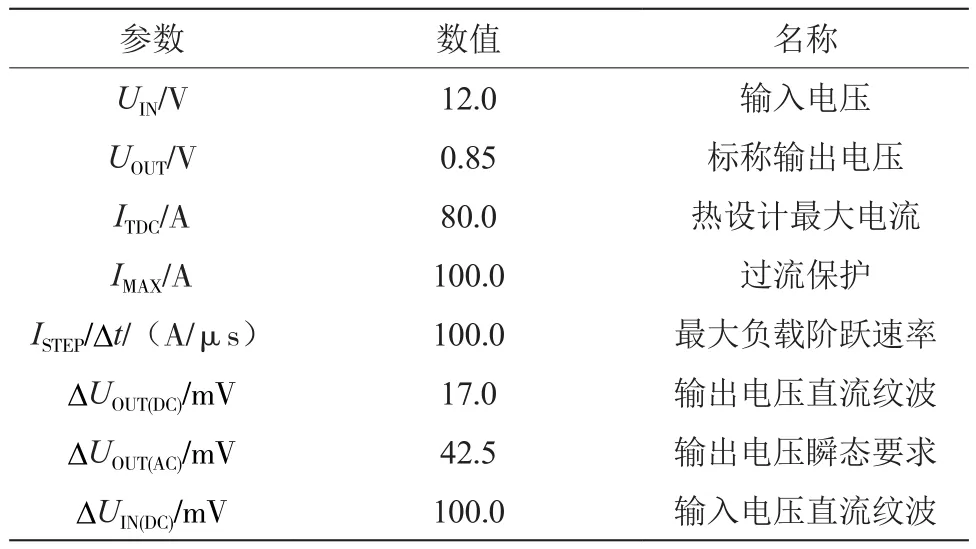

本文介绍的数字电源方案包含主控电路和驱动电路两部分。主控电路采用德州仪器的UCD9248,最大支持4个电源轨8相并联工作,UCD9248内部具有一个基于I2C通信协议的PMBus(电源管理总线)可以将电源输入电压、输入电流、各相输出状态、温度信息等上传主机系统并获得管理。数字环路控制支持3极点、3零点或数字PID控制,且最小1 mV的闭环控制精度,非常契合高性能大型FPGA的供电需求。驱动电路采用UCD7242,该驱动电路内部集成MOSFET,单通道最大输出10 A,尺寸小,功率密度高。通过8相交错并联,可以实现最大80 A的输出,设计满足表1的应用需求,设计方案框图如图2所示。

图2 电源方案框图

表1 应用需求表

2.1 电感量设计

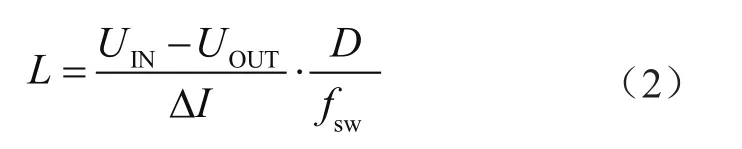

开关频率的取值与电感量的设计紧密相关,开关频率一般设计在100 kHz~2 MHz,通常较小的开关频率可以减少电源的开关损耗、电感的磁损和铁损,但需要的电感量和磁芯尺寸都将增大,较低的带宽也不利于瞬态响应。相反,较高的频率能提供良好的瞬态响应,较小的电感尺寸,但会增加开关损耗。平衡整体性能,选择开关频率fsw为500 kHz。单相输出纹波电流ΔI目标值为单相输出电流的35%,选取常用电感量330 nH。对应ΔI为4.787 A。占空比D与输入电压UIN以及输出电压UOUT之间的关系为:

每相的电感量为:

2.2 输入电容和输出电容设计

与单相输出电源相比,更多的相位交错并联能降低流经去耦电容的有效输入电流,从而降低输入电压上的直流纹波。由于实际电容存在等效串联电阻,电容内部发热的效应也可以减小,多相并联输出的设计能减少输入输出电容[2]。

每相上的输入有效电流与相位数和占空比的关系为:

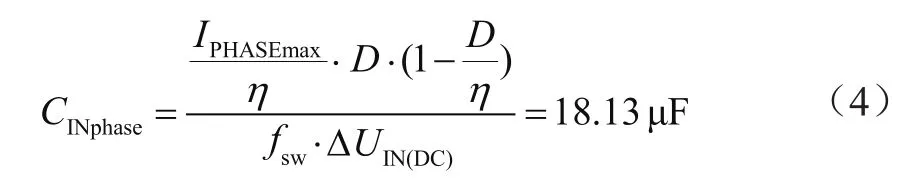

从式(3)和图3比较出,8相并联的有效输入电流约为单相的25%,4相的55%。根据每相输入电容电流,计算出需要的输入电容值为:

图3 输入电流有效值与占空比和相位数的关系

图3考虑陶瓷电容的温度和电压降额,每相采用两个输入为22 μF的陶瓷电容并联。

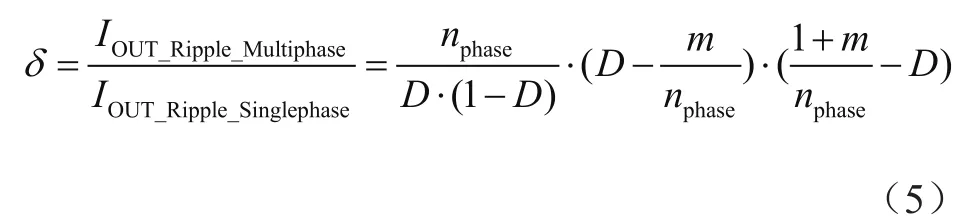

单相输出电源在上管开通、下管关断时,负载电流需要从输出电容提供,在上管关闭、下管开通时,电感给输出电容续流,整个过程产生了三角形的纹波电流和纹波电压。使用多相错位并联的电源,上管开通、下管关断时,可以由其他相的电感给输出电容续流,从而降低输出纹波电流和电压[3]。多相输出的纹波电流IOUT_Ripple_Multiphase和单相输出的纹波电流IOUT_Ripple_Singlephase与相位数和占空比的关系如图4所示。

图4 输出纹波电流与占空比和相位数的关系

式中,nphase为相位数;m等于floor(nphase·D)。

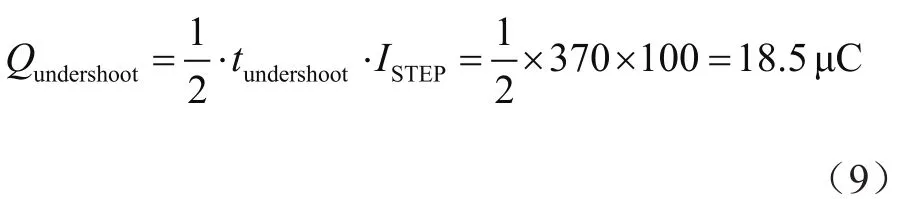

输出电压直流纹波要求为输出电压的±1%,需要的输出电容值为:

需要至少两颗47 μF的电容才能满足输出电压直流纹波要求。但是该电容通常不能够满足输出负载动态变化时输出电压的交流变化量(ΔUOUT(AC))。尤其是像现代FPGA这种要求内核供电电流大、变化速度快的负载特性,供电电源的输出电容往往需要进一步计算。

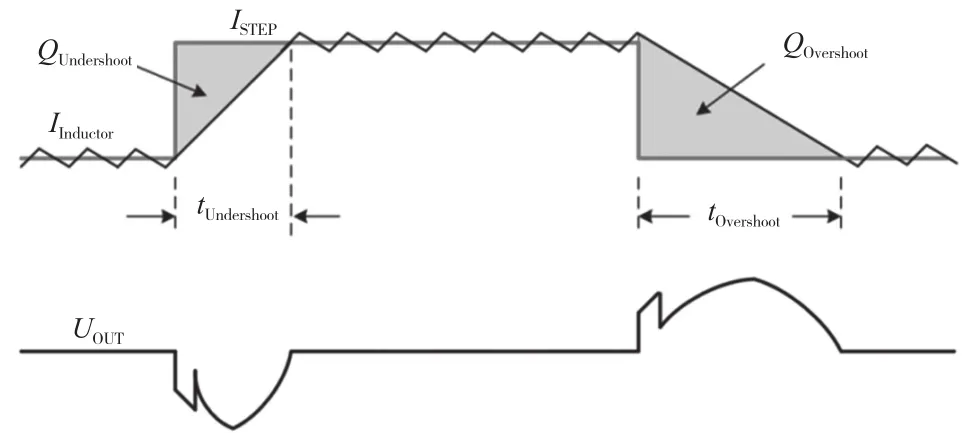

在负载突然上升时,输出电容优先供电流给负载,需要增大电感电流,电感给电容充能增大,输出电压出现下冲。在负载突然下降时,需要减小电感电流,在电感电流调节过程中,电感给输出电容的充电量过多,导致输出电压出现过冲,如图5所示。

图5 负载动态变化输出电压波形图

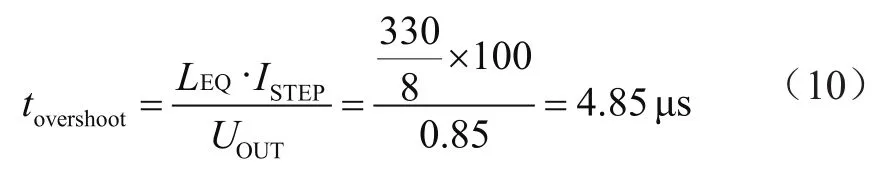

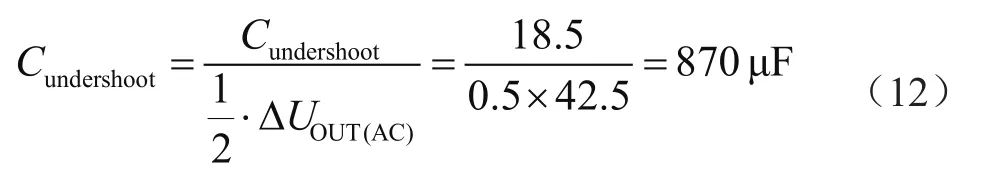

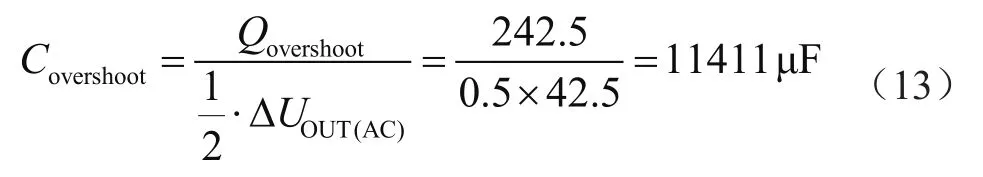

由于设计的电源是8相并联,因此等效的输出电感LEQ为:

下冲时间为:

下冲时间输出端需要的电量为:

上冲时间为:

上冲时间输出端增加的电量为:

满足下冲电压跌落需要的电容为:

满足过冲电压需要的电容为:

计算满足负载动态变化的输出电容为11 411 μF,每相用330 μF的电容5个。

2.3 环路补偿设计

电压型控制的同步降压电路由调制器和输出LC滤波器组成的开环系统,加上环路补偿网络组成稳定输出的闭环系统如图6所示。

图6 同步降压电路的闭环系统框图

误差电压输出与振荡器比较产生PWM信号驱动电路的上下管,振荡器波形是一个与开关频率相同峰峰值电压为1 V的锯齿波。调制器的增益由输入电压UIN与振荡器的峰峰电压ΔUOSC确定,计算公式为:

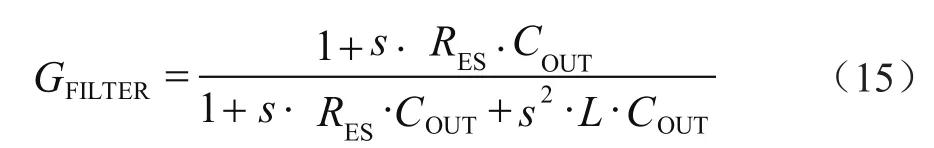

如图7所示的降压电路的开换系统,输出滤波器包含电感,所有输出电容和电容的寄生电阻RES,输出的LC滤波器是一个二阶带阻尼的系统,相关计算为:

图7 电压型控制的同步降压电路的开环系统

电压型降压电路的开环传递函数为:

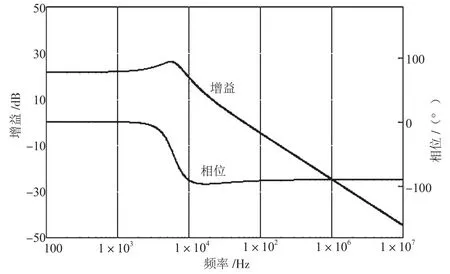

利用Mathcad数学软件制作波特图如图8所示,在LC谐振频率上存在一个双极点,RES产生的一个零点。FLC与FESR频率之间,幅值增益在双极点作用下以40 dB每十倍频速度减小,而且有一个非常高的峰值点,相位也在该位置发生陡峭的180°的变化。在FESR处ESR零点的作用下,幅值增益以20 dB每十倍频速度减小,相位提升了90°[4]。

图8 开环系统传递函数波特图

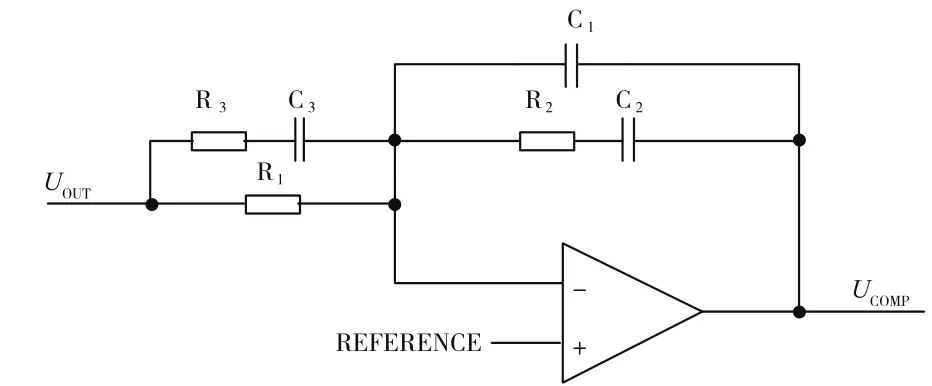

为使系统稳定,在双极点位置需要额外增加零点来提升相位,保证闭环系统的稳定性。一般而言,通过环路补偿的降压电路理想的波特图是幅值下降速度20 dB每十倍频,幅值裕量20 dB,相位裕量大于45°,带宽是开关频率的20%~30%。在模拟电路设计中,通常采用TypeⅢ型电路进行补偿,示意如图9所示。

图9 TypeⅢ型电路示意

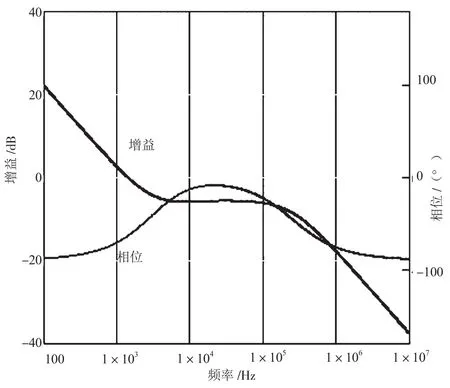

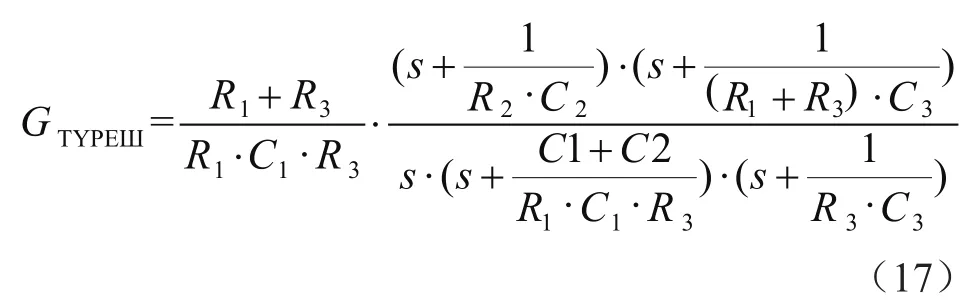

TypeⅢ电路可以提供两个零点,3个极点补偿。两个零点可以提供180°的相位提升,将两个零点合理地设置在输出LC谐振频率附近,可以抵消双极点的影响。TypeⅢ电路的传递函数如式(17)所示,对应波特图如图10所示。

图10 TypeⅢ型电路波特图

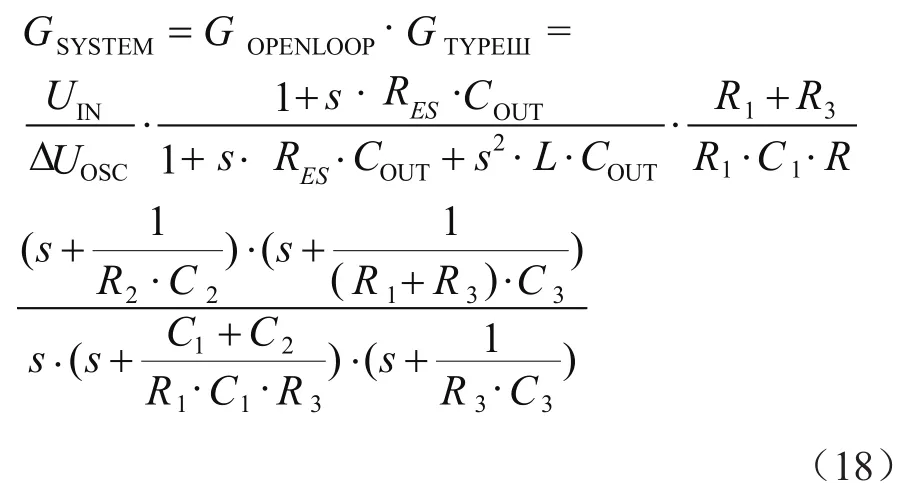

闭环系统的传递函数为:

通过环路补偿后的闭环降压电路系统,能够稳定地产生固定输出电压。根据闭环系统的传递函数公式(18)可以得出系统的穿越频率、相位增益和幅值增益如图11,图12所示。一般而言,穿越频率越大,系统的响应速度越快,但由于香农采样定理,穿越频率必须小于开关频率的一半,否则输出将会有很大的开关纹波,工程上通常取穿越频率为开关频率的1/10到1/5[5,6]。理想条件下,通过补偿电路零极点的设计,需要将系统的相位裕量大于45°,相位裕量低于60°时,会增大负载瞬态变化时的电压过冲[7]。

图11 闭环系统增益图

图12 闭环系统相位图

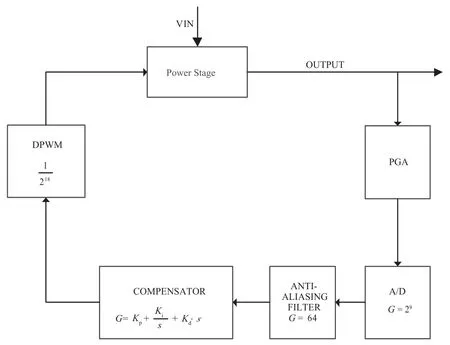

采用数字控制的UCD9248通过多个功能模块产生PWM信号,由于数字控制信号时钟高达4 GHz,分频到每相的斜坡比较器时的时钟信号最大有250 MHz,远远大于几百千赫兹开关工作频率,因此可以认为误差放大器的输出信号是连续的电压值。数字可调放大器可以设置1倍到8倍的增益。误差信号通过9位A/D转换,为防止高频噪音干扰,需要经过一个低频增益64的数字滤波器(Anti-Saturation)。整个数字闭环控制系统框图如图13所示。

图13 数字控制同步降压电路的闭环系统框图

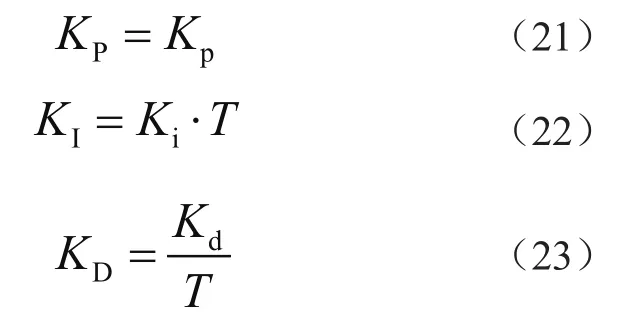

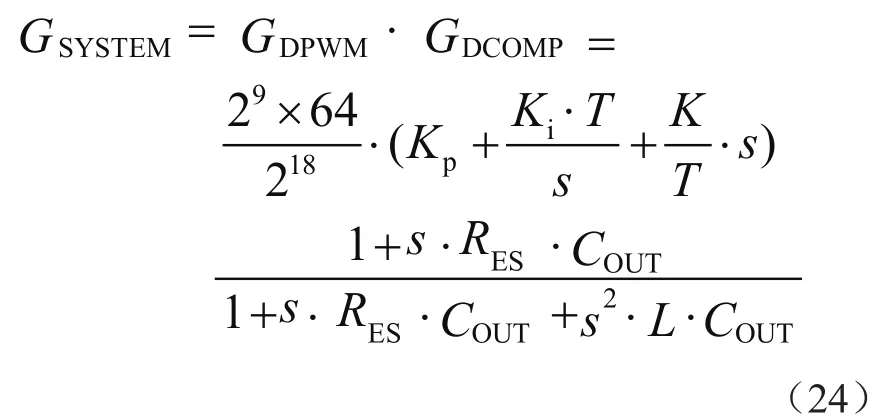

以上模块组成了数字PWM信号(DPWM)的固定增益,即:

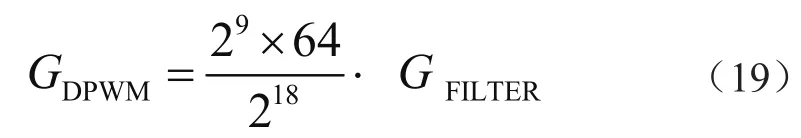

类似模拟电路的环路补偿传递函数,数字控制部分的环路补偿传递函数为:

对数字PID控制进行离散化对比,可得模拟PID控制器参数离散化公式为:

式中,T为最小采样时间;Kp为比例控制参数;Ki为积分控制参数;Kd为微分控制参数。

数字电路的系统传递函数为:

数字电路的环路补偿可以模拟3个极点、3个零点,或者模拟PID算法,方便设计系统的环路。

3 数字电源仿真

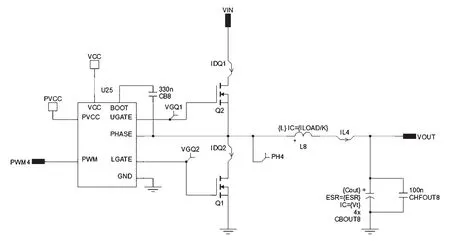

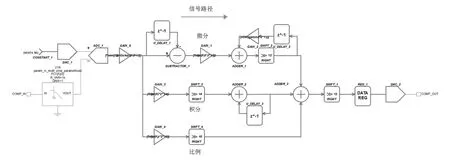

SIMetrix/SIMPLIS软件能够快速地对开关电源进行频率响应分析,在电源设计中应用广泛。根据上述的理论分析和芯片参数,建立由UCD9248数字芯片控制的8相BUCK降压电路[8]。其中,每相降压电路的功率电路部分和PID控制补偿部分仿真原理如图14和图15所示。

图14 功率级单相仿真电路原理图

图15 数字PID控制部分仿真原理图

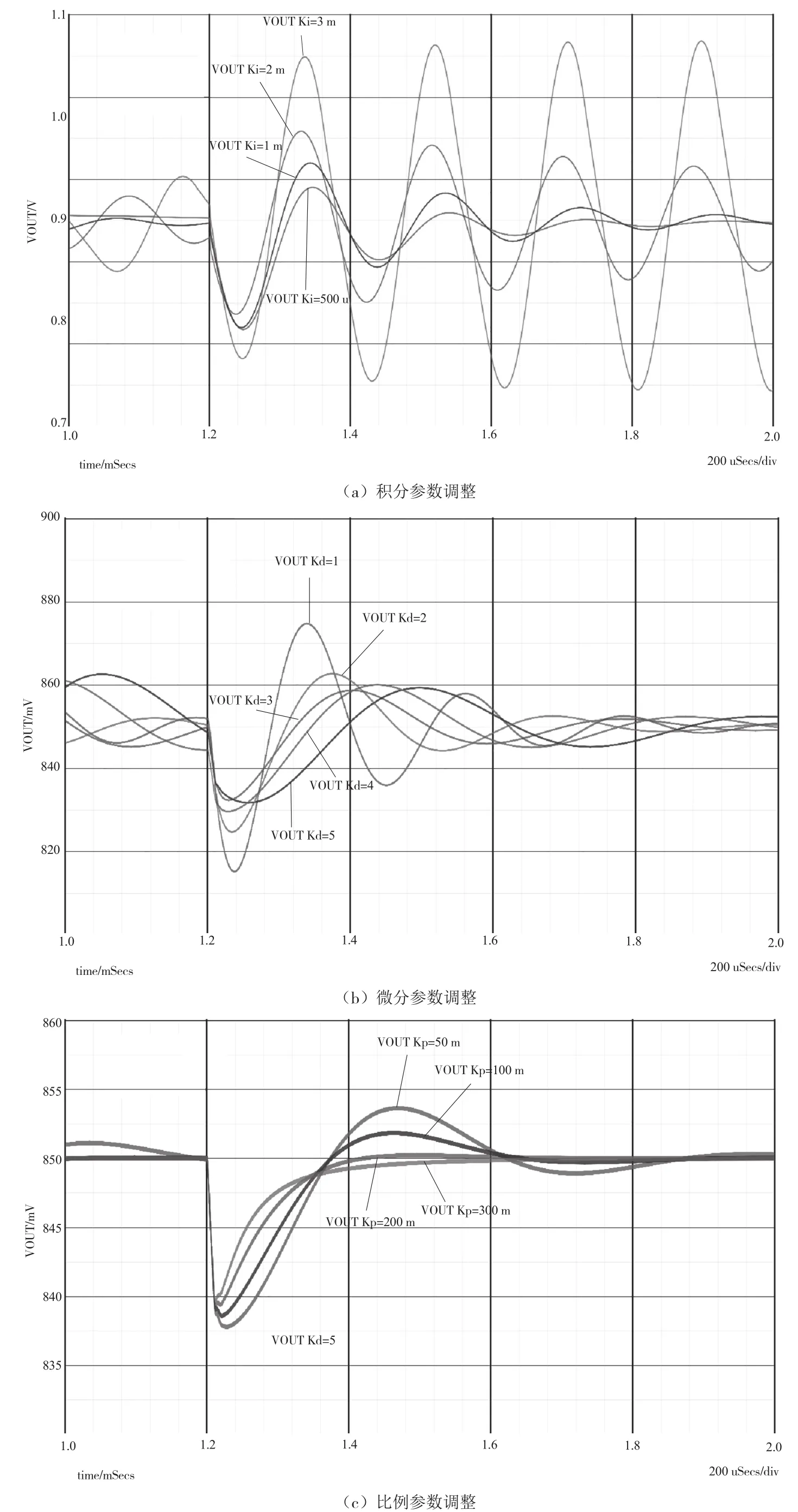

数字PID控制可以采用3个步骤进行调整:

(1)单用积分控制。逐渐增大Ki直到系统收敛。单积分控制输出电压可能存在振铃,需增加微分、比例控制来减小振铃。当Ki增大到4×10-3时,系统不收敛,如图16(a)所示。

(2)增加微分控制,逐渐增大Kd,直到Kd值的增加不能减小振铃振幅。Kd从1增加到4时,振幅逐渐减小。继续增大Kd时,振幅不变。如图16(b)所示。

图16 数字PID控制

(3)通过调整Kp进一步减小振铃。Kp从5×10-2增大到0.3时,系统由过阻尼变为欠阻尼,当Kp=0.2时,系统接近临界阻尼状态。

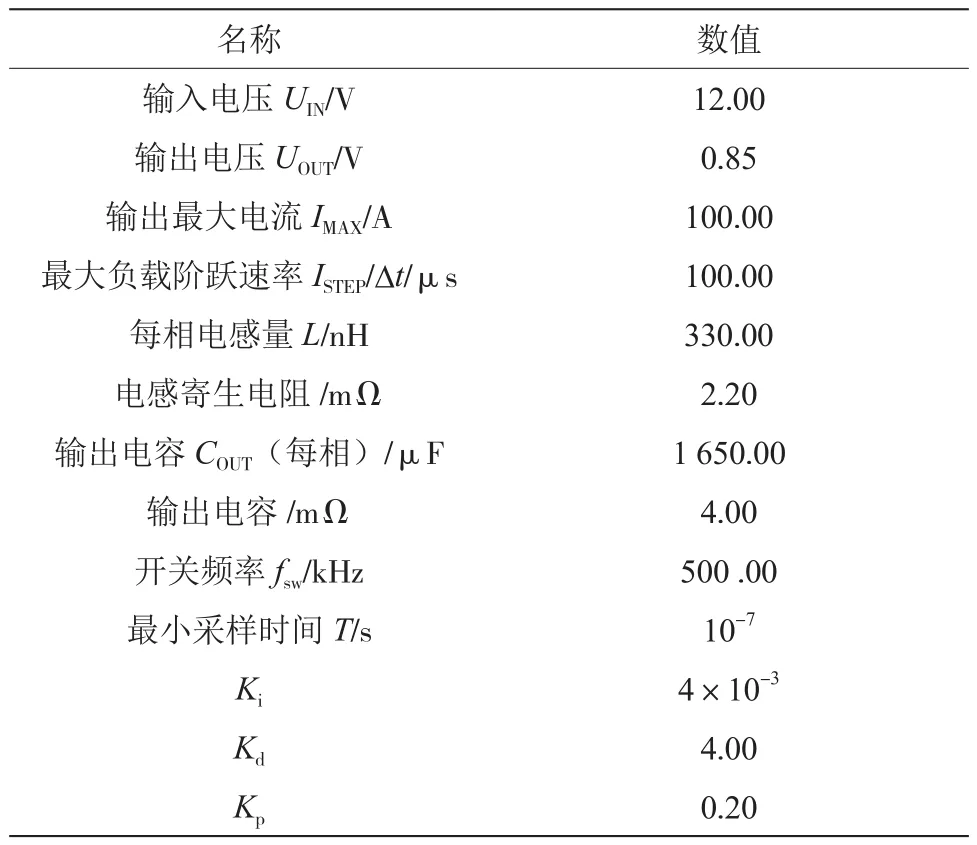

最后调试采用的参数如表2所示。

表2 调试参数

仿真结果,穿越频率37 kHz,相位裕量78°。仿真输出负载从100 A/μs速度从10 A增大到100 A,电压跌落了22 mV,如图17所示。

图17 仿真结果

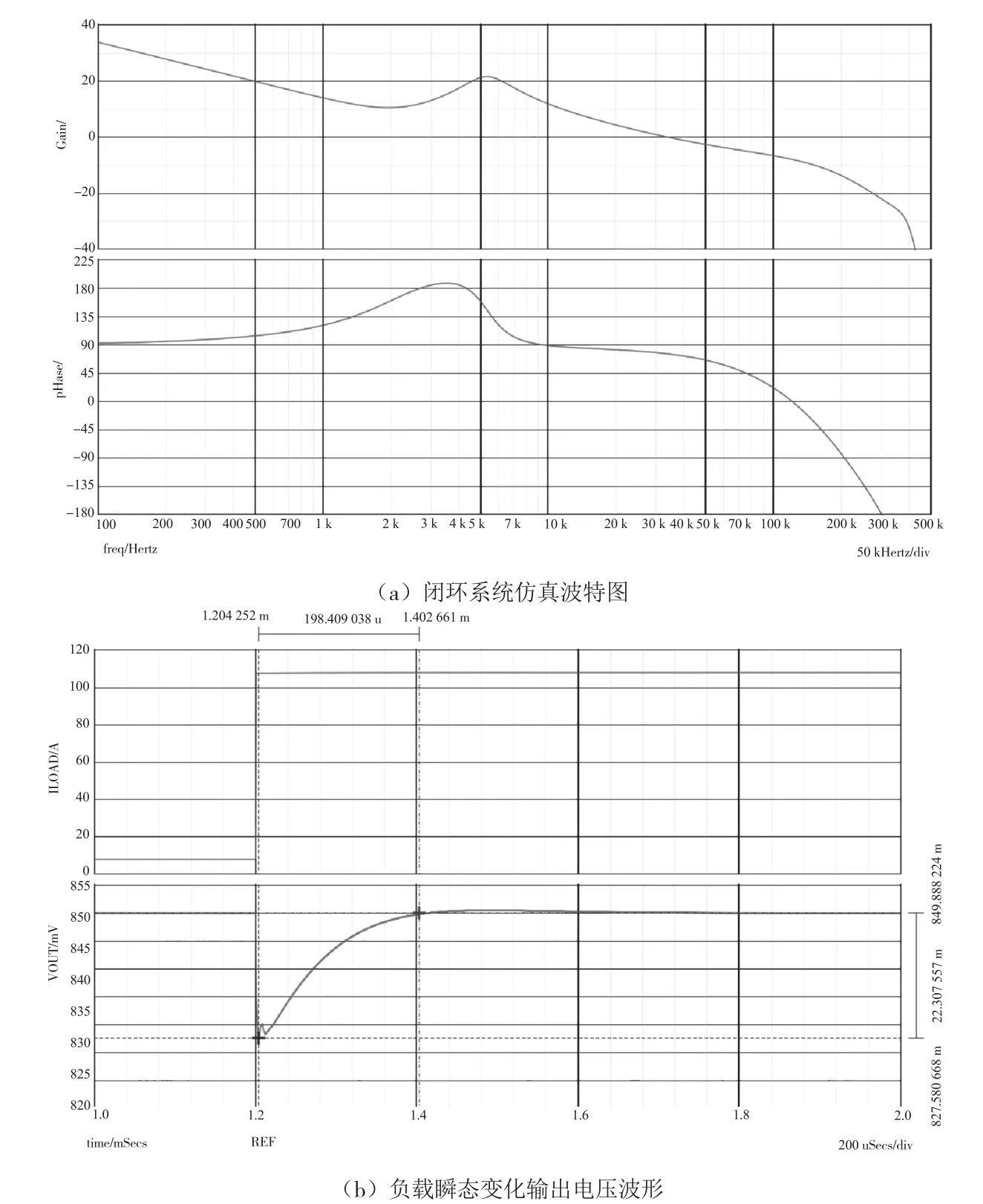

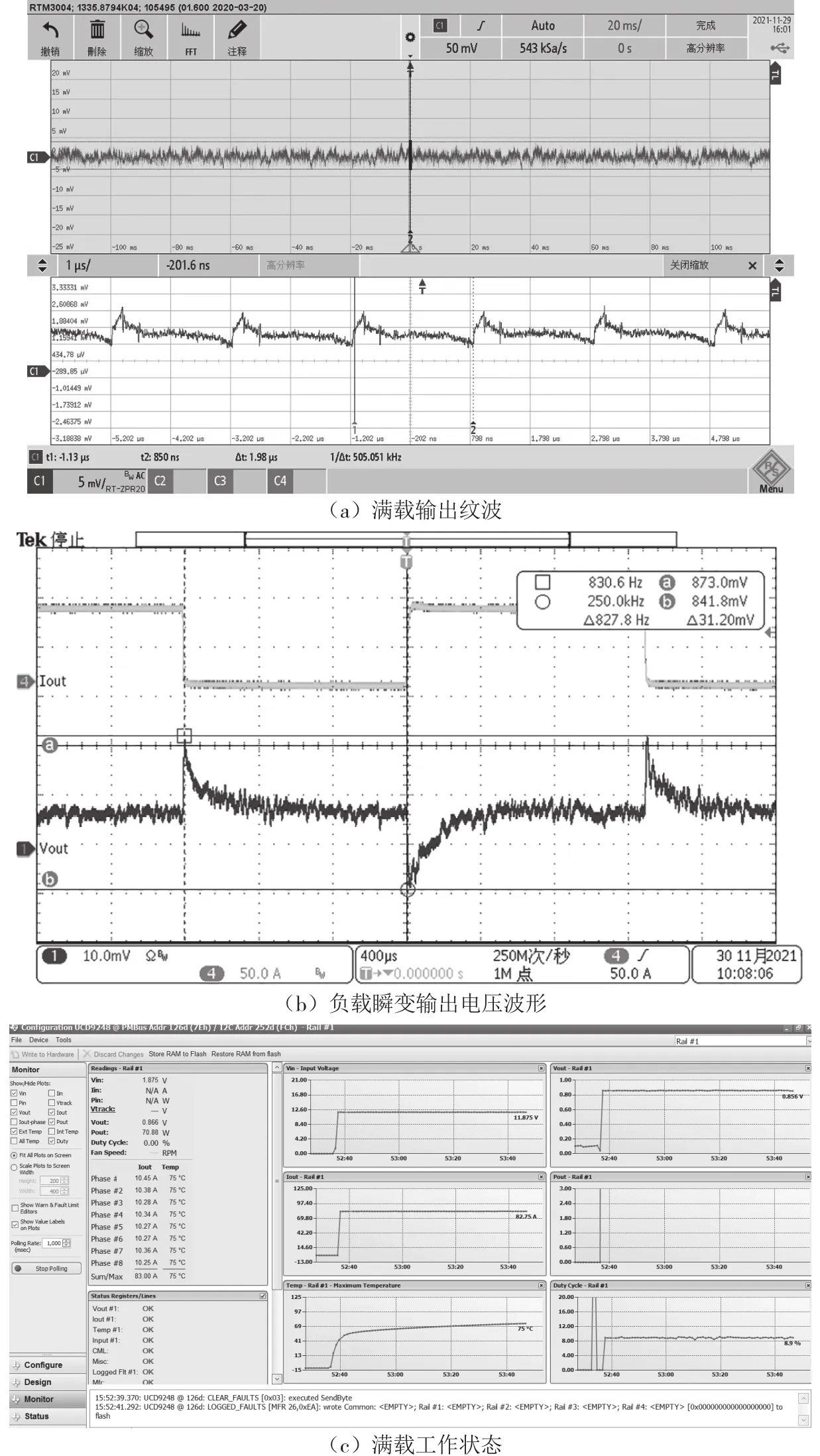

4 实验结果

根据上述设计,制作了基于UCD9248数字控制的8相交错并联降压电路验证板,并进行了测试,性能满足表1要求。在满载80 A输出电压下,输出电压纹波10 mV,如图18(a)所示。测试负载从10 A到80 A以100 A/μs变化时,输出电压峰值为31.2 mV,如图18(b)所示。通过UCD9248的PMBus电源管理总线系统,可以监测电源每相的输出电流、温度、输出功率、输出电压等信息,如图18(c)所示。

图18 实验结果

5 结 论

本文提出的应用于高性能FPGA核电压的数字电源设计,基于UCD9248设计了8相交错并联,数字PID控制,实现了输出电压在稳态和瞬态负载电流条件下,都有非常高的精度,并能与主机系统实现PMBus通信,仿真和实验结果表明设计的数字电源能够满足高性能FPGA核电压的供电要求。