基于FPGA的宽带线性调频信号的产生与实现

2022-06-09张浩然吴姿妍赵晓龙周寿桓

张浩然,吴姿妍,赵晓龙,刘 波,周寿桓

(固体激光技术重点实验室,北京 100015)

1 引 言

随着现代武器和现代飞行技术的发展,人们对雷达的作用距离、分辨力和测量精度等性能提出了越来越高的要求。为了提高测距精度和距离分辨力,要求信号具有大的带宽[1]。线性调频信号(Linear Frequency Modulation,LFM)因其具有信号波形易产生、脉冲压缩特性好和信噪比对多普勒频移不敏感等优点,在合成孔径雷达(Synthetic Aperture Radar,SAR)、逆合成孔径雷达(Inverse Synthetic Aperture Radar,ISAR)和激光雷达(Light Detection And Ranging,LiDAR)等系统中应用广泛[2]。LFM信号的带宽越大,激光雷达的分辨力越高。因此,研究大带宽LFM信号的产生对于促进高分辨力激光雷达的发展具有重要意义。

本文以激光雷达远程测距为背景,提出一种基于现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)、采用直接数字波形(Direct Digital Waveform Synthesis,DDWS)合成技术的方法,设计并最终产生出了带宽为150 MHz,距离分辨力为1 m的宽带线性调频信号。

2 基于DDWS技术的LFM信号产生理论

2.1 LFM信号的数字形式

线性调频信号又称啁啾信号,也叫鸟鸣(Chirp)信号。它是一种在信号持续期间频率发生连续线性变化的信号。线性调频信号可以进行脉冲压缩,它经匹配滤波器压缩后可输出窄脉冲。它也是一种常用的雷达脉冲调频信号,由于具有良好的距离分辨力和较大的发射能量,在雷达领域中得到了广泛的应用[3]。

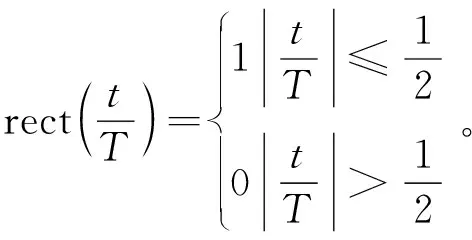

矩形包络的LFM信号的复数表达式为:

(1)

(2)

对式(2)进行傅里叶变换,可求得线性调频信号的频谱表达式为:

(3)

经整理得:

(4)

其幅度谱|S(ω)|为:

(5)

其相位谱φ(ω)为:

φ(ω)=φ1(ω)+φ2(ω)

(6)

其中:

(7)

(8)

式(7)~(8)为菲涅尔积分(Fresnel integral)公式。

一般雷达的单载频脉冲信号时宽和带宽的乘积接近为1,大时宽和大带宽不可兼得。而脉冲压缩技术能在宽脉冲信号内附加非线性调相以扩展信号的频带,从而使信号同时获得大时宽和大带宽。脉冲压缩技术能对宽脉冲的LFM信号进行非线性相位调制,进而使其带宽增大,使得宽脉冲的LFM信号同时具有大带宽。这样既能提供雷达的探测距离,又能提高雷达的分辨力。LFM信号的时域波形、时频分析图及其频谱如图1所示。

图1 LFM信号时域波形、时频分析及频谱图Fig.1 LFM signal time-domain waveform, time-frequency analysis and spectrum diagram

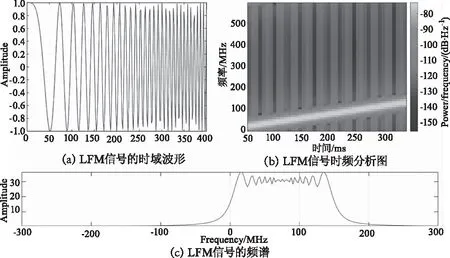

2.2 LFM信号产生方法选取

LFM信号的产生方法如图2所示,主要分为模拟法和数字法。模拟法起源较早,它主要依靠模拟器件产生信号。模拟法主要分为有源和无源两种方法。有源法一般采用压控振荡器(Voltage-Controlled Oscillator,VCO)或者锁相环(Phase Locked Loop,PLL)来产生线性调频信号。而无源法常用色散延迟线或者声表面波(Surface Acoustic Wave,SAW)器件来产生[4]。随着科学技术的发展,模拟法产生的LFM信号渐渐不能满足军事的需求。它产生的线性调频信号存在线性度低、稳定性差、相位噪声较大等问题。

图2 LFM信号产生方法Fig.2 LFM signal generation method

采用数字法可以获得更好的线性调频信号。目前使用较多的LFM信号产生方法为数字法。数字法主要以直接数字合成(Direct Digital Synthesis,DDS)技术为主。DDS主要分为基于相位累加的直接数字频率合成(Direct Digital Frequency Synthesis,DDFS)技术和基于波形存储直读的DDWS技术两种[6]。

DDWS技术不但具有精确的相位和频率分辨力,而且能方便的实现多种复杂波形,同时能采用各种有效方法提高频谱纯度。相比于DDFS技术,利用DDWS技术可以更方便灵活的改变生成LFM信号的带宽、脉宽等参数,并容易对线性调频信号的幅度和相位进行预失真校正,进而得到接近理想的LFM信号。本文将采用DDWS技术产生宽带线性调频信号。

2.3 DDWS技术工作原理与特点

2.3.1 DDWS技术工作原理

直接数字波形合成技术主要分为两个阶段,存储波形和还原波形。存储波形是将我们所需要的输出信号波形,由上位机仿真软件按照采样率、带宽和时宽等参数计算出信号波形中各个采样点的值,经量化和编码存储至高速存储器中。还原波形时,由系统时钟提供一个参考时钟给时钟控制逻辑,时钟控制逻辑分别控制地址控制逻辑和D/A转换。高速存储器按照时钟控制逻辑分配的时钟顺序,对存储在寄存器地址中的波形数据进行读写操作。按采样顺序读出波形数据,经D/A转换成我们所需的模拟波形信号[7]。原理框图如图3所示。

图3 DDWS技术原理框图Fig.3 DDWS technology principle block diagram

2.3.2 DDWS技术的特点

由于DDWS技术采用了不同于传统合成方法的全数字结构,因而具备许多模拟合成技术或者频率合成技术不具有的特点。

(9)

其中,N为D/A转换器的位宽,当位宽N越大时,LFM信号的频率分辨率越高。

2)极短的频率转换时间:由DDWS技术的原理框图可知,输出信号的波形存储于高速存储器中,切换不同频率的信号时,频率转换时间由高速存储器读取决定,读取时间可达皮秒量级。

3)预失真补偿:预失真补偿是DDWS技术最显著的优点,它能方便灵活地对信号的幅度和相位进行预失真处理,补偿系统畸变的影响[8]。

3 系统设计

3.1 控制逻辑和D/A器件选择

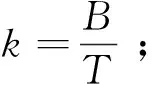

考虑到系统稳定性、时钟频率和高采样率等因素,本文最终选FPGA当做系统的控制模块。其中FPGA采用Xiinx公司推出的Kintex7系列的KC705开发板,原理如图4所示。板上载有高性能芯片XC7K325T-2FFG900C,该芯片在运算速率和传输性能等方面都具有良好的性能,板上包含326080个逻辑单元。其中系统时钟为200 MHz,是由Si Time公司的SiT9102芯片产生的LVDS差分时钟,其频率稳定度高达1 PPM(Part Per Million,百万分比)。由于时钟控制着波形数据在寄存器中的读写操作,所以对于输出接近理想的信号波形起着关键性作用。

图4 KC705开发板原理图Fig.4 KC705 development board schematic diagram

时钟控制逻辑,我们选取ANALOG DEVICES公司的AD95XX时钟芯片为整个系统提供时序逻辑。该芯片片内VCO的调谐频率范围为2.30 GHz至2.65 GHz,能产生4对800 MHz LVDS时钟输出,其时钟抖动超低(≤275 fs、rms)。为满足对信号带宽的要求,根据奈奎斯特定理,为得到较好的LFM信号,过采样率应较大。一般取过采样率≥4,即D/A转换速率至少应为LFM信号最高频率的4倍。根据我们想产生150 MHz的LFM信号,其采样率应大于600 MHz,D/A器件选用ANALOG DEVICES公司的AD91XX的DAC芯片,该芯片有4个通道,采样率超过2.0 GSPS,分辨率为16 Bit,完全能满足我们的要求。

3.2 JESD204B数据传输

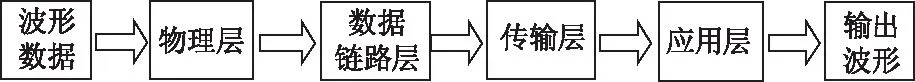

JESD204B是一种新型的高速串行接口,传输速率可达12.5 Gbit/s。其结构主要分为4层,包括物理层、数据链路层、传输层和应用层。其结构框图如图5所示。

图5 JESD204B数据传输关系图Fig.5 JESD204B data transmission diagram

物理层主要为高速串行信号的接收和发送提供底层通路;数据链路层主要包括数据的8 B/10 B编解码和确定数据的发送/接收;传输层主要将数据映射为帧数据;应用层主要为数据添加控制字符和尾字符,并把数据进行打包和添加扰码[9]。目前Xilinx公司已开发出JESD204B接口的ip核,本文将采用其ip核进行数据传输。

3.3 系统结构设计

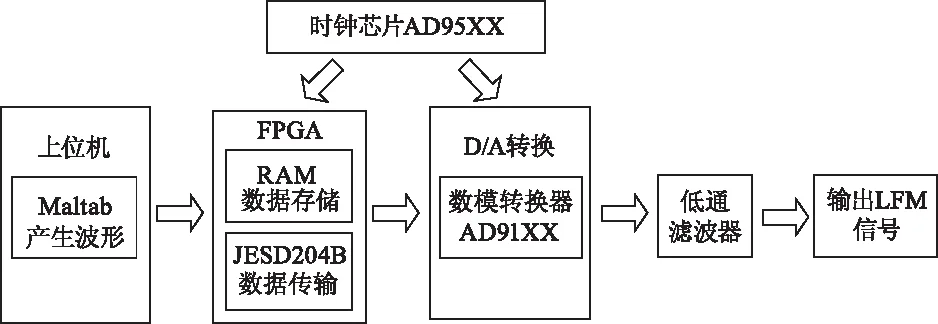

本文基于激光雷达远程测距的应用背景,总体系统结构如图6所示。

图6 宽带线性调频信号产生总体系统结构Fig.6 Broadband chirp signal generation overall system structure

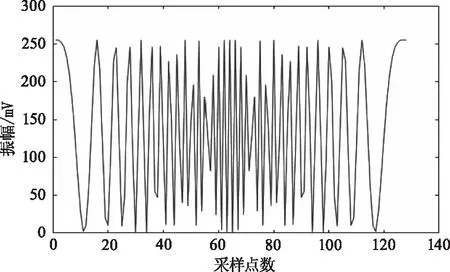

首先需要由上位机产生原始的LFM信号波形文件。利用Matlab仿真软件,根据Chirp函数设置LFM信号的带宽为150 MHz,采样率设置为320 MHz,脉冲宽度设置为400 ns,产生128个采样点。如图7所示,然后将128个采样点转换为16进制的数据并存储在FPGA(KC705)的存储单元中。

图7 LFM信号波形Fig.7 LFM signal waveform

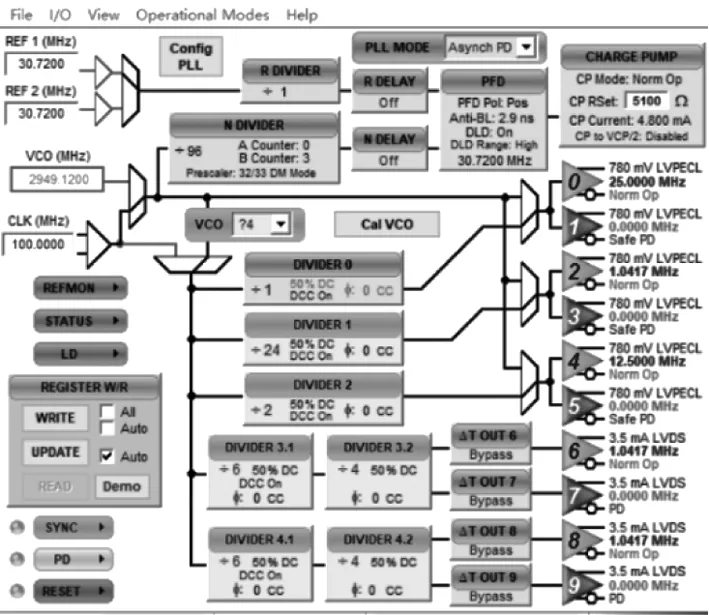

然后利用Vivado中的PLL ip核,将KC705的系统时钟200MHz分频为2个不同频率的时钟,分别为clk_80MHz,clk_100MHz。将clk_100MHz作为时钟芯片AD95XX和DAC芯片AD91XX的输入时钟,通过SPI(Serial Peripheral interface,串行外围设备接口)协议,分别对AD95XX的68个寄存器和AD91XX的76个寄存器完成初始化配置。时钟芯片AD95XX完成初始化后,将分别给AD91XX和JESD204B模块提供参考时钟。AD95XX的时钟配置如图8所示。

图8 AD95XX时钟配置Fig.8 AD95XX clock configuration

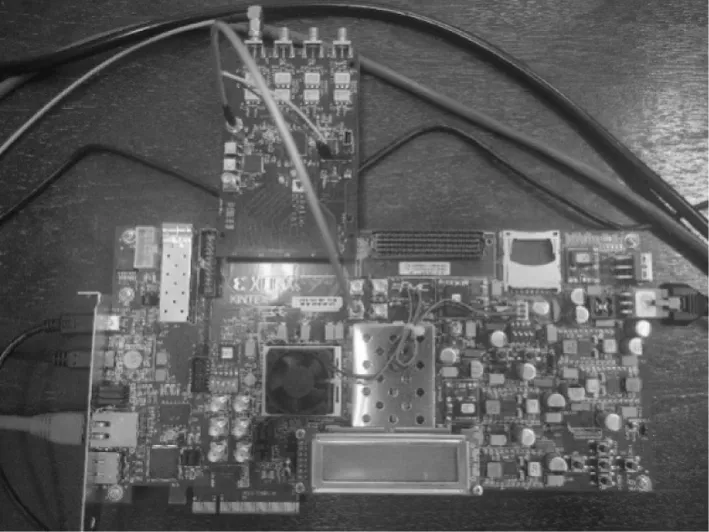

JESD204B模块主要包含两个部分,数据链路层ip核和物理层ip核。我们通过AXI4-Lite协议完成对数据链路层和物理层的初始化配置。一切准备就绪后,将FPGA的RAM中存储的波形数据将通过JESD204B口发送给数模转换器AD91XX。数据先写入寄存器中,然后再通过寻址找到对应的数据并读出来,最后就产生出信号波形。系统总体实物如图9所示。

图9 系统总体实物图Fig.9 Overall physical map of the system

4 测试结果

工程实践平台采用LeCroy公司的610Zi示波器,宽带LFM信号的实现如图10所示。

图10 150 MHz的线性调频信号Fig.10 150 MHz chirp signal

图10的上半部分是宽带LFM信号的波形图,每格是50 ns,该信号的一个周期是8格,时宽为400 ns;图10的下半部分是对宽带LFM信号做快速傅里叶变换(Fast Fourier Transform,FFT),每格的宽度是50 MHz,可以看出产生的宽带LFM信号的带宽是3格,实现了150 MHz的带宽。因为距离分辨力与带宽成反比,由公式:ΔR=c/2ΔF,(c为光速,c=3×108m/s)可知,当带宽为150 MHz时,距离分辨力为1 m。实验产生的LFM信号的带内平坦度较高,说明该信号所含各频率成分大小的差异较小,更接近于理想值。

5 结 语

本文基于FPGA,通过DDWS技术设计并实现了带宽为150MHz的宽带LFM信号。通过对LFM的产生和原理分析,对DDWS技术的描述、对器件性能和实现过程的具体描述,最后给出了系统测试结果,验证了该系统的可行性和有效性,产生了较为理想的宽带LFM信号。该信号可以作为激光雷达光发射机的射频调制信号,通过相位调制器,对激光信号源产生的“种子光”进行相位调制,获得调制的“种子光”。而后再对“种子光”进行放大,实现调制光的大功率输出,这有利于提升激光雷达的作用距离和距离分辨力。本文的研究结果对激光雷达在实际中的应用具有重要的实际意义。但本文产生的宽带LFM信号也存在不足之处,信号的带宽和带内平坦度还有优化和提升空间。