一种高可靠的星载多核DSP加载方式及实现

2022-06-02璩泽旭孙钰林

璩泽旭,王 鹏,孙钰林

(中国空间技术研究院西安分院,西安 710000)

0 引言

在航空、航天、武器等领域,越来越复杂的图像处理需要并行化的处理系统,以满足实时性要求。要实现复杂功能的系统,高性能的FPGA+DSP架构是目前常用的方案。由于单核的DSP性能已发展至极限,无法适应复杂的并行算法,多核DSP应运而生,成为当前数字信号处理的发展方向。

TMS320C6678是基于KeyStone架构,采用8个DSP内核构建而成,集成了320 GMAC定点计算或160 GFLOPS浮点计算性能,每个内核工作频率达到1.25 GHz,支持高性能信号处理应用[1]。为了满足不同应用场合的需求,实现最大的设计灵活性。TMS320C6678支持的BOOT模式有SPI、I2C、PCIe、EMAC、SRIO和并口EMIF16 Nor Flash[2]。邓豹[3]和刘章文等[4]提出针对C6678利用EMIF16(external memory interface,外部存储器接口)的Nor Flash加载实现方法,但不能直接在轨应用,存在单粒子翻转可能。薛志远等[5]针对C6678多核的特点,提出了一种基于多核Bootloader的设计方法,侧重于多核程序生成和Bootloader自启动。而本文针对多核DSP的卫星应用环境,从系统的角度出发,解决空间单粒子翻转问题,实现多核DSP在轨高可靠加载。

本文详细研究TMS320C6678的加载模式和流程,并提出基于EMIF16的Nor Flash高可靠异构加载方式,实现程序Bootloader上电启动和任意时刻重启动。经测试验证,TMS320C6678能够稳定可靠运行。该方法支持在轨可重构,加载不同的DSP软件处理不同功能,实现软件定义卫星。

1 C6678加载方式

BOOT过程就是DSP的自动加载启动过程,在上电或复位后,根据设定的不同的加载模式,将可执行代码自动加载到内存中,并正确运行程序的过程[6]。可执行代码可以存放在外部的非易失存储器中(如I2C PROM、SPI FLASH等),也可以存放在外部设备中,由通用接口(如SRIO、PCIe、HyperLink等)加载。DSP通过内部集成的自动加载器(rom boot loader,RBL)来实现BOOT过程,默认RBL只执行核0(主核)[7]。

RBL就是固化在DSP内部ROM中的软件程序代码,DSP在上电或复位后,由RBL负责自动加载/接收(外部或存储器)传送的应用程序代码,并跳转到入口地址运行程序。在C6678中,RBL存放在0x02B00000~0x02B1FFFF的128 KB空间内[8]。

C6678启动有两种方式:主机启动、存储器启动。主机启动也叫从模式,通过其他处理器向DSP写入代码,完成加载。包括网口、RapidIO、PCIe等[9]。存储器启动也叫主模式,DSP主动从外部存储器中存放的代码搬到其内部高速存储器并且运行。一般通过外挂在EMIF16或I2C总线接口的FLASH完成。由于C6678的配置程序较大,带I2C接口的FLASH容量较小,不满足大工程应用。因此本文采用的存储器启动使用EMIF16接口方式加载[10]。

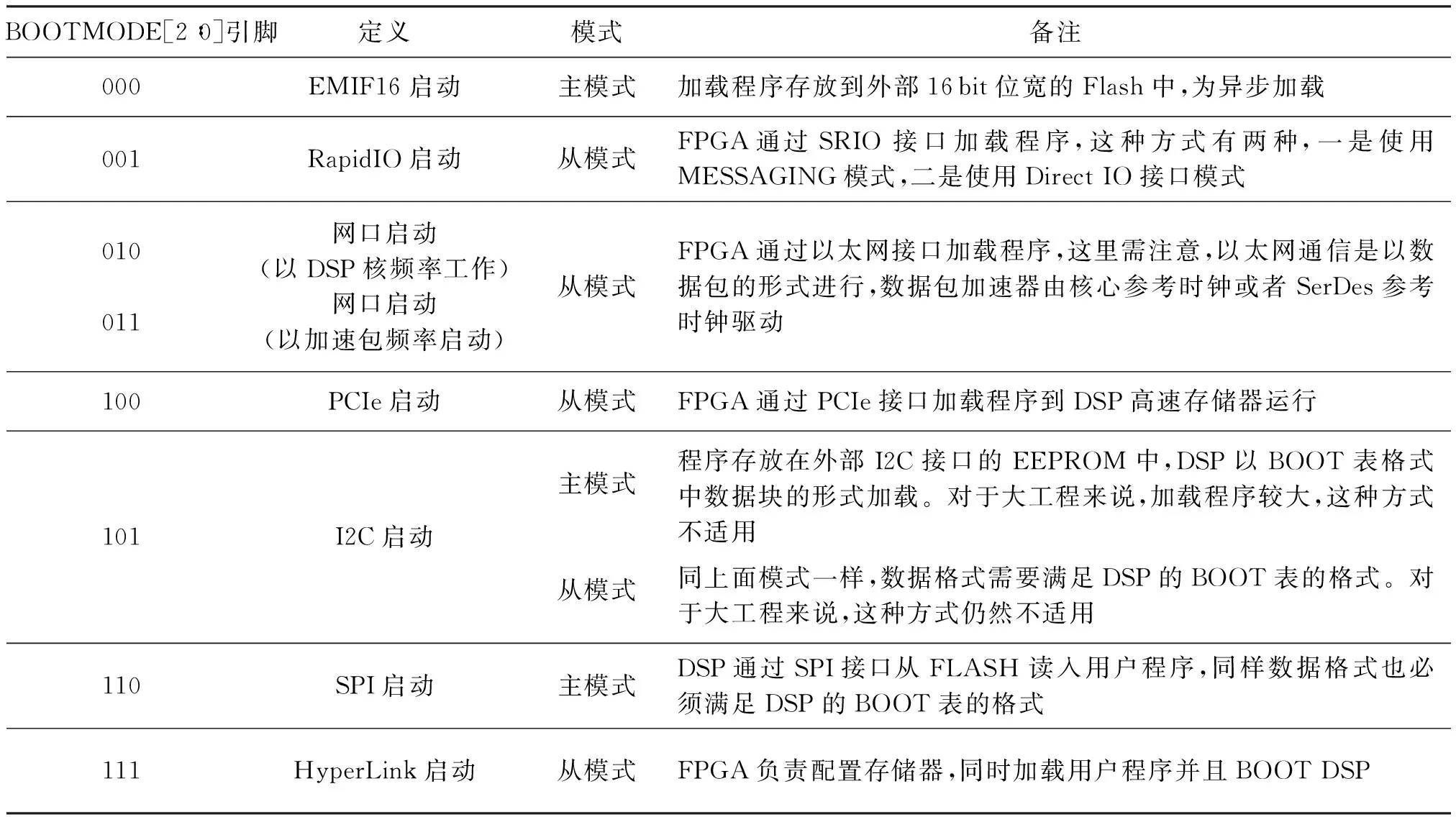

DSP的加载启动模式通过外部的13个引脚BOOTMODE[12∶0]/GPIO[13∶1]复位时的硬件状态来选择[11]。BOOTMODE配置引脚中,BOOTMODE[2∶0]用于选择启动模式,BOOTMODE[12∶3]是根据设定的启动模式,初始化相应的配置参数和寄存器[12]。BOOTMODE引脚对应不同的加载方式,启动加载器的模式配置如表1所列。

表1 C6678 BOOTMODE引脚对应的加载方式

2 硬件设计

EMIF16 Nor Flash模式是不用上位机参与、相对简单、独立成系统,本系统采用此方式。EMIF16接口接FPGA,FPGA外挂Nor Flash。C6678的加载通过FPGA配合完成,C6678的程序存放在可靠性更高的Nor Flash中,并外挂在FPGA上。对应的电路原理如图1所示。

图1 C6678加载的硬件原理Fig.1 Hardware principle of C6678 loading

与常用的DSP加载设计不同,本论文创造性提出DSP的EMIF接口与FPGA相连,FPGA与Nor Flash相连,通过软硬件结合的方式,提高DSP程序可靠性。系统上电后先完成FPGA的配置加载,待FPGA加载成功后启动DSP复位,并将EMIF接口与Nor Flash接口连通,让DSP通过EMIF接口从Nor Flash中自动读取DSP加载文件,实现DSP的自动加载。这样做的好处主要有两个,一是实现DSP程序在轨重构功能;二是在空闲时可以对存放在Nor Flash内部的DSP程序进行RS编译码,针对空间单粒子打翻的Nor Flash程序进行纠检错,并将译码后的结果重新写入Nor Flash中,防止DSP程序SEU造成卫星功能失效。

Nor Flash内部分为多个区,主要存放DSP程序和智能处理DEM参数,本文主要介绍DSP程序。存放DSP程序分为功能1区、功能2区、上注1区和上注2区。其中上电后系统自动加载功能1区,通过指令可以切换加载功能2区或上注1区、上注2区,上注1区和上注2区用于在轨重构,4个区的程序均可以在轨更新。

FPGA加载成功后状态机开始工作,步骤如下:

1)先产生一个全局复位信号,对V7程序内所有需要复位的状态寄存器赋予初值;

2)全局复位结束后,进入对DSP复位初始化状态,产生DSP所需的POR、RESETFULL复位信号,使DSP完成全局复位;

3)初始化结束后,V7程序进入配合DSP加载的状态,将Nor Flash接口的操作权交给DSP的EMIF接口,同时等待DSP加载成功的反馈信号(检测GPIO9和GPIO10信号);

4)DSP加载成功后,进入配合DSP的DEM参数读取状态;

5)DEM读取结束后,进入IDLE状态,从DSP的EMIF接口中收回Nor Flash操控权,等待来自下位机的Nor Flash操作指令,根据指令对其进行读、写、擦操作(RS编译码、回写)。

FPGA控制DSP加载状态机跳转时序如图2所示。

图2 DSP加载状态机Fig.2 DSP loading state machine

3 程序设计

C6678为JTAG连接提供了专门的绿色通道,不管采用何种BOOT方式,当仿真器连上时会自动Reset并从仿真器下载初始化代码,即JTAG优先级最高。调试C6678需要用到两个主要的配置文件,一个仿真器配置文件ccxml和一个gel文件。其中ccxml是用来对仿真器和板参数进行定义,当连上仿真器并connect后可以确定JTAG扫链成功。gel文件包含基本的调试函数和Bootloader文件,用于仿真开发的初始化文件。在器件Reset后需要对硬件地址进行确认并完成内存的初始化,不同的电路板对应的gel文件不同,需要根据需求对其进行参数修改。

程序读入前要根据不同的BOOT方式进行格式转换,转换工具是将各核的.out文件转换成.dat文件,主核BOOT之后再引导其他的从核。

C6678启动软件包括核0(也称为主核)和其他7核的启动。一般由主核启动成功后,主核运行应用程序,对其他核依次写入程序代码,然后依次中断其他核,让其启动。多核的启动流程如图3所示。

图3 软件处理流程Fig.3 Software processing flow

主核和其他核同时启动,在启动过程中,主核需完成向其他核写程序代码和中断其他核这两项工作,其中,主核向其他核写入程序代码涉及核间通信。C6678的每个核都有单独的RAM空间,这些RAM空间也可以被其他核读写。需要注意的是两个核或者多个核不能同时读写同一个地址空间,会导致数据读写错误。为了避免这个问题,其他核在上电后,将一直处于IDLE状态,IDLE状态下不会对外设和片内RAM资源进行操作。主核对其他所有核依次写入程序代码,在主核对所有其他核完成代码写入后,主核依次快速地给其他核发出IPC中断,其他核就逐一被启动。主核给其他核按照先后顺序发IPC中断,在这个很小的时间差内,首先被启动的核不能读写另外核的RAM空间。因此其他核的程序代码有一个延迟程序,该延迟程序执行后,主核即可完成对其他核的启动工作。

4 验证结果

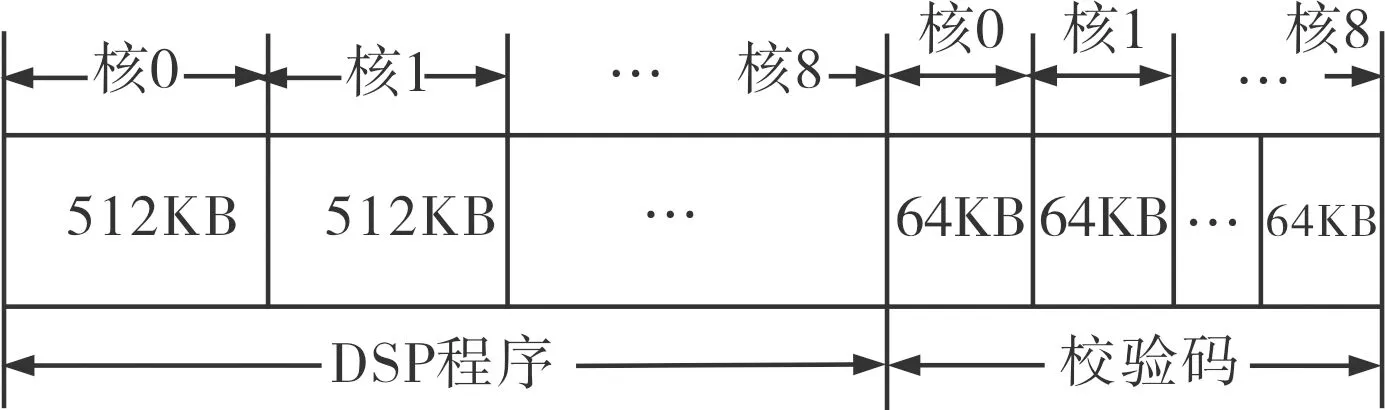

本文设计的DSP程序大小为512 KB,8个核总共大小为512 KB×8。选取的RS编译码为RS(144,128),上注的DSP程序经过RS编码后的数据量为512 KB×8×144÷128=4 608 KB,其中原始程序为4 096 KB,校验码为512 KB。每套DSP程序在Nor Flash中存放分布如图4所示。

图4 DSP程序在Nor Flash存放分布Fig.4 Storage and distribution of DSP programs in Nor Flash

为了验证本文提出的多核DSP加载方式,模拟卫星在轨SEU效果,对写入Nor Flash的DSP程序改写不同位置的数据(包括校验码),模拟空间单粒子翻转,上电自动启动失败。同时发送FPGA复位进行DSP重加载,仍然启动失败。随后发送FPGA编译码指令,对Nor Flash内部存放的DSP程序进行RS编译码后回写,断电后重启,DSP上电启动成功,同时发送FPGA复位指令加载DSP,DSP重加载成功。如图5所示,GPIO_reg1[9]和GPIO_reg1[10]分别表示核1和核2成功返回的遥测(协议规定DSP启动成功后通过GPIO管脚向FPGA间隔发送0、1数据)。

图5 DSP加载成功结果Fig.5 DSP load successful result

5 结论

本文提出的基于TMS320C6678多核DSP 中EMIF16主模式加载方式,介绍了C6678的加载模式和流程;给出了EMIF16 Nor Flash加载硬件设计原理和具体的软件设计流程,以及具体的实现步骤。最后,在基于高性能的FPGA+DSP板卡上给出C6678的EMIF16自启动试验结果,验证了方案的可行性。本文将存放DSP程序的Nor Flash外挂到FPGA上,实现在轨可重构功能,同时利用空闲时间对Nor Flash中DSP程序进行RS编译码回写,实现多核DSP加载的高可靠性,具有重要的应用价值。