基于JTAG的CPLD测试配置方法研究

2022-05-26姚鼎武翰

姚鼎,武翰

(中国船舶重工集团公司第七一六研究所,连云港 222006)

引言

JTAG(Joint Test Action Group)是一种国际标准测试协议(IEEE 1149.1),主要用于芯片内部测试,目前主流的CPLD、FPGA、DSP等器件均已支持边界扫描测试技术,区别于传统接触式测试,JTAG可以明显提升测试效率,降低测试成本,因此JTAG技术现已在大规模集成电路测试与诊断中广泛应用。本文基于JTAG测试技术的CPLD测试流程主要是:利用EDA专业软件工具基于改良移步算法自动生成测试向量,然后通过USBBlaster下载电缆,将测试向量通过JTAG接口加载至待测CPLD中,同时依据测试项目要求选择对应的测试模式,将测试响应向量与期望的向量进行分析处理从而得出判定结果。

1 JTAG测试技术基本原理

JTAG测试实质上是在芯片每个引脚上增加一个边界扫描单元(BSC),这些BCS以串联的方式连接起来,形成了一条特殊的测试链。芯片正常工作时,数据流不会经过BSC,也就是不影响芯片的正常工作;当芯片处于测试逻辑时,内部逻辑工作停止,测试数据经测试链以串行移位的方式开始进入测试,并作用于芯片的I/O引脚,通过对这些I/O引脚的激励/响应信号采集分析得出测试结果,边界扫描测试电路的基本结构如图 1所示。

图1 边界扫描基本结构图

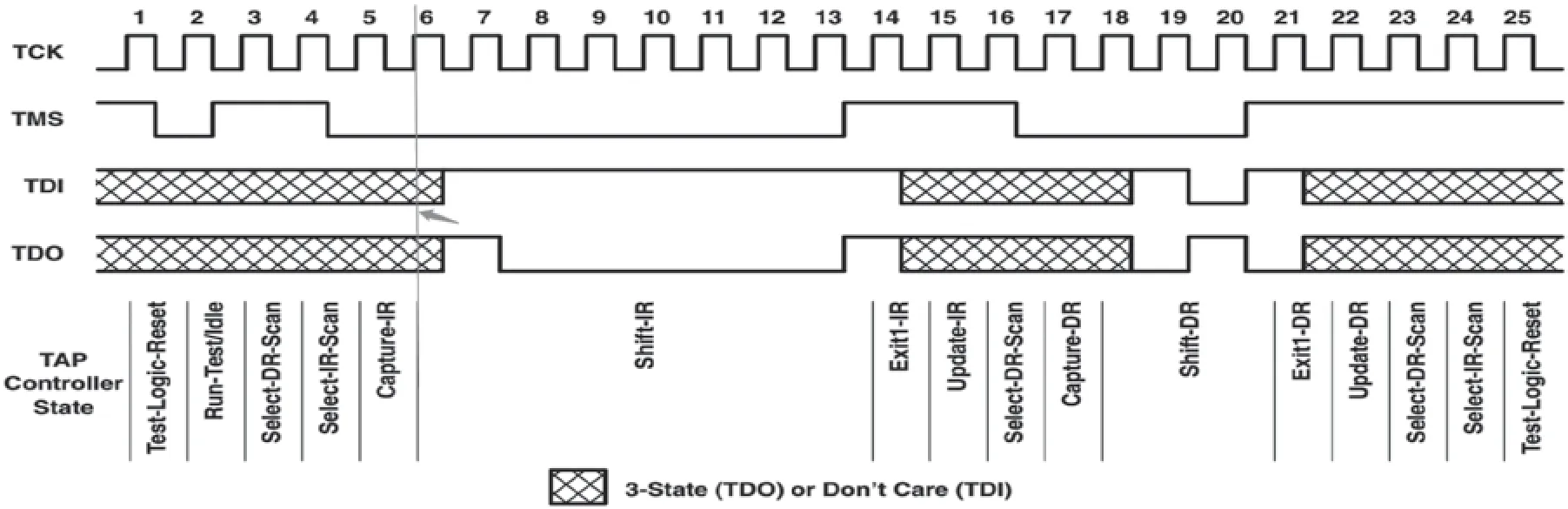

其中测试访问端口(TAP)是JTAG的重要结构,主要是通过对 TMS 和 TCK 信号的采样,将不同类型的寄存器连接到 TDI 与 TDO 之间,TAP端口描述如表1所示。

表1 测试访问端口[1]

JTAG典型时序图如图2所示。

图2 JTAG的一个典型时序图

依据IEEE1149.1对JTAG接口的五个引脚的接法规定如下:

1)TDI必须上拉

TDI上拉电阻的选择应参照器件的参数手册,如果手册中没有具体的要求,一般选取4.7 K,但不能小于1 K。根据IEEE 1149.1标准,全“1”指令为旁路指令(BYPASS),而给JTAG接口装入旁路指令不会影响该器件的正常工作,如果将TDI上拉,即使器件被错误装入其他指令,也将转换为旁路指令, 不会影响其正常工作。

2)TDO不用上拉/下拉

TDO悬空,在设计中应避免将TDO脚作为I/O脚。器件在进行指令移位和数据移位时TDO才有输出,其他情况下均为高阻状态。

3)TMS必须上拉

TMS上拉电阻的选择可参照器件手册,一般选取4.7 K。根据TAP控制器的十六状态机原理可以知道,若TMS 在5个时钟周期内连续保持高电平,则无论TAP控制器处于何种状态,都将回到Test-Logic-reset状态,此时器件正常工作。

4)TCK建议下拉

TCK采用上拉或下拉电阻的选择应参照器件的参数手册,若手册未给出具体要求,则应进行下拉,一般下拉电阻选取1 K。JTAG器件的TDI和TMS都在TCK时钟的上升沿有效,如果TCK下拉或上拉,将不会产生有效的TCK上升沿。但是请注意TCK下拉电阻至少要大于330 Ω,否则JTAG测试加载仪可能无法正确驱动TCK信号。

5)TRST必须下拉

TRST下拉电阻的选择参照具体器件手册,一般选取1 K。根据TAP控制器的十六状态机工作原理,/TRST下拉,器件处于Test-Logic-reset状态,不影响正常工作,因此通过JTAG进行测试时,必须首先将/TRST拉高才能进行。

综上所述,JTAG测试引脚接法如图3所示。

图3 JTAG测试引脚接法示意图

以上电阻的阻值是在VCC为5 V或3.3 V时确定的,VCC为2.5 V等电压时电阻的阻值确定可参考器件手册和以上电阻阻值并依据相同的原理进行确定,如果器件手册有推荐的上拉或下拉电阻的阻值,则推荐以器件手册的为准。

本文拟开发对象为Altera公司的MAX-7000CPLD,因此选择利用Quartus Ⅱ将测试程序通过MasterBlaster串行/USB通信电缆下载至CPLD中,MasterBlaster串行/USB通信电缆USB接口与计算机相连,与PCB板相连的是标准的10针插座。JTAG引脚配置如图4所示。

图4 JTAG引脚配置图

2 测试访问端口(TAP)设计

TAP控制器是整个JTAG电路实现的核心控制器,控制着测试过程中相关信号的传递和改变,其内部由一个16状态的有限状态机、控制逻辑和译码电路组成[2]。指令寄存器与各种数据寄存器的运行均由TAP控制器通过发出控制信号来控制,即在TCK上升沿采样TMS信号用于控制TAP状态转移,其状态转移的翻转逻辑如图5所示。

TAP控制器内的状态机有16个状态,用于解释串行输入的TMS控制信号,且均在TCK上升沿进行转变,图5中箭头上的“0”或“1”即表示在TCK上升沿采样到的TMS值,两竖列分别表示数据路径和指令路径,且均有7个状态。TMS为“01”时,TAP控制器为“选择数字寄存扫描”状态;当TMS为“11”时则为“选择指令寄存扫描”状态;当TMS为连续5个(及以上)的TCK脉冲宽度信号时,TAP控制器则跳转至“测试逻辑复位”状态[3]。

图5 TAP控制器的状态转换图

3 测试向量生成

测试向量生成算法非常多,有移步算法、等权值算法、计数补偿算法等等,阶段实际工作中,对测试结果有较高要求,需要重点考虑测试覆盖率即测试向量的完备性,因此采用移步算法,同时对该测试向量生成算法进行进一步的优化。

在具体测试时,首先进行全0和全1的测试,判断CPLD是否存在固定故障,并记录存在的故障引脚。然后进行移步0的测试,若激励与响应相等,表明没有短路故障,本项测试结束,若第n个激励与响应向量不等,则需判断第n个测试向量的第n位是否为0,若是,则为线与故障,反之则为线或短路故障,同时继续执行移步0测试,直至结束,并记录存在的故障引脚,最后可根据移步0测试中存在的短路故障生成移步1的测试向量。因此当CPLD中的线网数为A时,移步0的测试向量个数也为A,若存在短路故障的线网个数为B,移步1测试向量个数为B 基于JTAG标准的边界扫描测试一般的执行过程如图6所示。首先解析和综合测试程序开发过程中的描述文件,并通过专用EDA工具对测试算法进行仿真,同时将仿真信号转换成测试软件可识别的测试向量信息,然后利用JTAG转换接口将测试向量加载至被测电路中,执行测试程序,将测试响应信息与期望值进行比较,从而完成最终的测试。 图6 JTAG测试的执行过程 基于JTAG的测试流程首先必须进行完整性测试,只有完整性测试合格才能说明测试扫描链正常,完整性测试主要是对 TCK、TMS、TDI、TDO 四个进行检测,确定TAP控制器各信号状态,从而确定扫描链是否正常。而后可以进行功能及参数的测试,通过采样激励/响应信号,并进行分析,完成每项测试内容具体测试流程如图7所示。 图7 JTAG测试具体流程 本文主要从软件设计方面详细介绍了基于JTAG的CPLD测试配置方法,给出了JTAG测试的设计与实现过程,从而为下一步CPLD测试的工程实现奠定了基础,有利于缩短CPLD的测试周期,降低测试成本。4 JTAG测试的设计与实现

5 结束语